Изобретение относится к импульсной технике и может быть использовано в цифровых синтезаторах частот.

Цель изобретения - повьппение быстродействия и увеличение числа ступеней коэффициента деления.

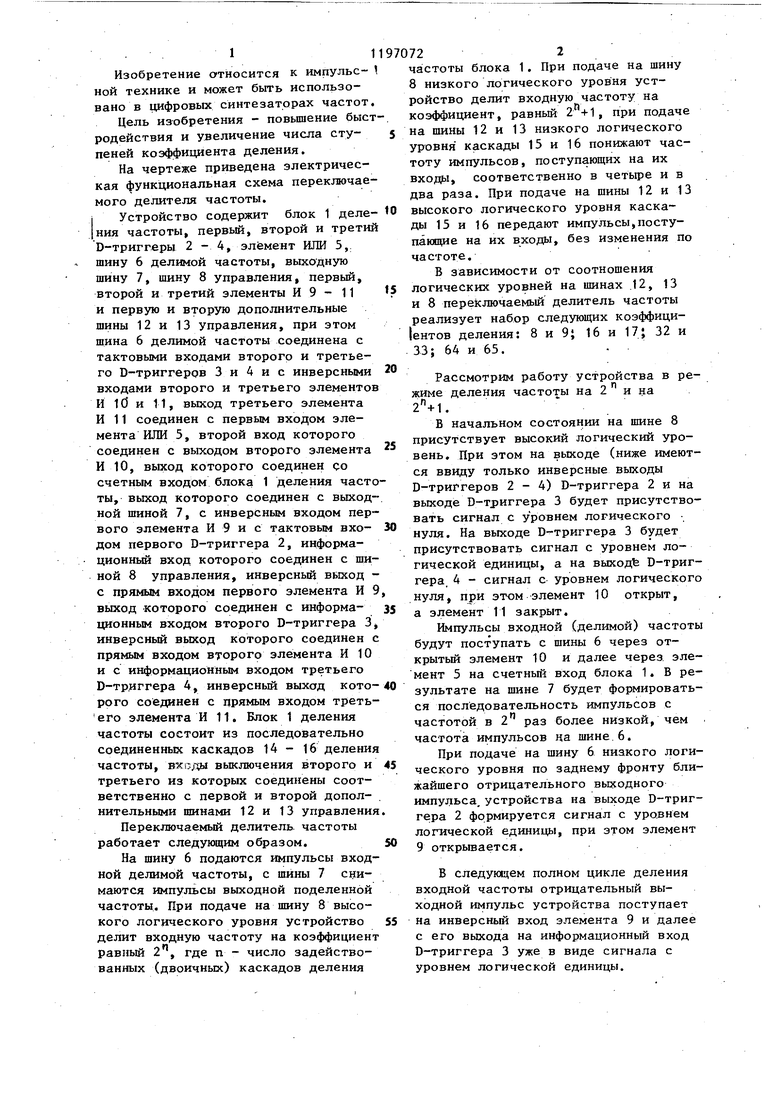

На чертеже приведена электрическая функциональная схема переключаемого делителя частоты.

Устройство содержит блок 1 деления частоты, первый, второй и третий D-триггеры 2-4, элемент ИЛИ 5, шину 6 делимой частоты, выходную шину 7, шину 8 управления, первый, второй и третий элементы И 9 - 11 и первую и вторую дополнительные шины 12 и 13 управления, при этом шина 6 делимой частоты соединена с тактовыми входами второго и третьего В-триггердв 3 и 4 и с инверснЕ 1ми входами второго и третьего элементов И 1б и 11, выход третьего элемента И 11 соединен с первым входом элемента ИЛИ 5, второй вход которого соединен с выходом второго элемента И Ю, выход которого соединен со счетным входом блока 1 деления частоты, выход которого соединен с выходной шиной 7, с инверсным входом первого элемента И 9 и с тактовым входом первого D-триггера 2, информационный вход которого соединен с шиной 8 управления, инверсный выход - с прямым входом первого элемента И 9 выход которого соединен с информационным входом второго D-триггера 3, инверсный выход которого соединен с прямым входом второго элемента И 10 и с информационным входом третьего D-триггера 4, инверсный выход которого соединен с прямым входом третьего элемента И 11. Блок 1 деления частоты состоит из последовательно соединенных каскадов 14 - 16 деления частоты, входы выключения второго и третьего из которых соединены соответственно с первой и второй дополнительными шинами 12 и 13 управления

Переключаемый делитель, частоты работает следующим образом.

На шину 6 подаются импульсы входной делимой частоты, с шины 7 снимаются импульсы выходной поделенной частоты. При подаче на шину 8 высокого логического уровня устройство делит входную частоту на коэффициент равный 2, где п - число задействованных (двоичных) каскадов деления

частоты блока 1. При подаче на шину

8низкого логического уровня устройство делит входную частоту на коэффициент, равный , при подаче на шины 12 и 13 низкого логического уровня каскады 15 и 16 понижают частоту импульсов, поступающих на их входы, соответственно в четыре и в два раза. При подаче на шины 12 и 13 высокого логического уровня каскады 15 и 16 передают импульсы,поступаюпре на их входы, без изменения по частоте.

В зависимости от соотношения логических уровней на шинах 12, 13 и 8 переключаемый делитель частоты реализует набор следующих коэффици|ентов деления: 8 и 9; 16 и 17J 32 и 33; 64 и 65.

Рассмотрим работу устройства в режиме деления частоты на 2 и на .

В начальном состоянии на шине 8 присутствует высокий логический уровень. При этом на вь1ходе (ниже имеются ввиду только инверсные выходы D-триггеров 2-4) D-триггера 2 и на выходе D-триггера 3 будет присутствовать сигнал с Уровнем логического нуля. На выходе D-триггера 3 будет присутствовать сигнал с уровнем логической единицы, а на выходЬ D-триггера, 4 - сигнал с уровнем логического нуля, при этом элемент 10 открыт, а элемент 11 закрыт.

Импульсы входной (делимой) частоты будут поступать с шины 6 через открытый элемент 10 и далее через элемент 5 на счетньй вход блока 1. В результате на шине 7 будет формироваться последовательность импульсов с частотой в 2 раз более низкой, чем частота импульсов на шине.6.

При подаче на шину 6 низкого логического уровня по заднему фронту ближайшего отрицательного вьшодного импульса, устройства на выходе D-триггера 2 формируется сигнал с урознем логической единицы, при этом элемент

9открывается.

В следующем полном цикле деления входной частоты отрицательный выходной импульс устройства поступает на инверсный вход элемента 9 и далее с его выхода на информационный вход D-триггера 3 уже в виде сигнала с уровнем логической единицы.

По заднему фронту первого отрицаельного входного импульса рассмативаемого цикла деления на выходе -триггера 3 будет сформирован сигнал с уровнем логического нуля, при этом элемент 10 закрьшается. В ре- . зультате следующий второй входной импульс не пройдет на. счетный вход блока 1.

Одновременно по заднему фронту торого отрицательного входного имnyjlbca на выходе D-триггера 4 будет сформирован .сигнал с уровнем логической единицы. При этом элемент 1 Т откроется. Все последующие, отрицательные входные импульсы, начиная с третьего, начнут вновь, поступать с шины 6, но теперь уже через эле- . . мент 11 и далее в виде положительных импульсов через элемент 5 на счетный вход блока 1.

После окончания отрицательного выходного импульса в рассматриваемом цикле деления входной частоты на информационном входе D-триггера 3 устанавливается сигнал с уровнем логического нуля, а по заднему фронту ближайшего отрицательного входного импульса на выходе D-триггера 3 вновь будет сформирован сигнал с уровнем логической единицы, при этом элемент 10 откроется. Все послегдующие отрицательные входные импульсы будут поступать через элемент 10 и далее в виде положительных импульсов через элемент 5 на счетный вход блока 1. С задержкой на один такт входной частоты На выходе D-триггера 4 будет сформирован сигнал с уровнем логического нуля и элемент 11 закроется.

Таким образом, в рассмотренном цикле деления частоты на счетный вход блока 1 поступает гшсло импульсов на единицу меньше, чем число импульсов, поступивших на шину 6о

Очевидно, что до тех пор, пока на шину 8 воздействует низкий логический уровень, в каждом полном цикле деления входной частоты каждьй второй входной импульс (считая с момента поступления выходного импульса на информационный вход D-триггера 3) не достигнет счетного входа блока 1 .

Исключение одного счетного импульса в каждом цикле деления входной частоты приведет к увеличению длительности положительного полуперио- да выходной частоты устройства на величину одного периода входной частоты и равносильно увеличению.на единицу коэффициента деления переключаемого делителя частоты.

Таким образом, при наличии на шине 8 сигнала низкого логического уровня на шине 7 будет формироваться последовательность импульсов с частотой 2 +1 раз более низкой, шм частота и |пyльcoв на шине 6.

После подачи на шину 8 высокого логического уровня по заднему фронту ближайшего отрицательного импульса выходной частоты на выходе D-триг.гера 2 вновь будет сформирован сигнал с уровнем логического нуля, запрешающий прохождение-. через элемент

9на информационный вход D-триггера 3 всех последующих импульсов выходной частоты. Одновременно на выходе D-триггера по заднему фронту ближайшего отрицательного импульса входной частоты будет сформирован сигнал с уровнем логической единицы, а по заднему фронту следующего отрицательного импульса входной частоты сигнал с уровнем логического нуля

будет сформирован на выходе D-триггера 4, при этом элемент 10 открывается, а элемент 11 с задержкой на один период входной частоты закрывается. Все без исключения импульсы входной частоты будут поступать с шины 6 через открытый элемент 10 и

далее через элемент 5 на счетный вход блока 1. В результате переклю- . чаемый делитель частоты в этом режиме имеет коэффициент деления, равный 2.

Задержка прохождения импульсов входной частоты через идентичные по структуре и параметрам элементы

10и 11, а также через элемент 5 не влияет на максимальную рабочую частоту переключаемого делителя частоты, которая в этом случае будет определяться только быстродействием не-. пользуемых триггерных каскадов.

8

д 3

сQt

| название | год | авторы | номер документа |

|---|---|---|---|

| Масштабный преобразователь кодов | 1988 |

|

SU1569994A1 |

| Устройство для деления двоичных чисел | 1987 |

|

SU1432508A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ФУНКЦИИ МОМЕНТОВ ЕРМАКОВА В.Ф. | 1994 |

|

RU2092897C1 |

| Устройство фиксации переходов через нуль периодического сигнала | 1984 |

|

SU1187145A1 |

| Измеритель средней частоты импульсов | 1987 |

|

SU1487661A1 |

| Делитель частоты с переменным коэффициентом деления | 1988 |

|

SU1677869A2 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Делитель частоты с переменным коэффициентом деления | 1983 |

|

SU1119177A1 |

| УПРАВЛЯЕМЫЙ ДЕЛИТЕЛЬ ЧАСТОТЫ ИМПУЛЬСОВ | 2000 |

|

RU2175167C1 |

| Синтезатор интервалов времени | 1986 |

|

SU1406558A1 |

ПЕРЕКЛЮЧАЕМЫЙ ДЕЛИТЕЛЬ.ЧАСТОТЫ, содержащий блок деления частоты, выход которого соединен с вьгходНой шиной, элемент ШШ, первый, вто- рой и третий D-триггеры, шину управления и шину делимой частоты, которая соединена с тактовыми входами второго и третьего D-триггеров, отличающийся тем, что, с целью повышения быстродействия и увеличения числа ступеней коэффициента деления, в него введены первая и вторая дополнительные шины управления и три элемента И, инверсный вход первого из которых соединен с выходной шиной и с тактовым входом первого D-триггера, информациоаный вход которого соединен с шиной управления, инверсный выход - с прямьм входом первого элемента И, выход которого соединен с информационным Входом второго D-триггера, инверсный (ВЫХОД которого соединей с информационным входом третьего D-триггера и с прямым входом второго элемента И, инверсный вход которого соединен с шиной делимой частоты и с инверсным входом третьего элемента И, I прямой вход которого соединен с версным выходом третьего D-триггера, выход - с первым входом элемента. ИЛИ, второй вход которого соединен . с выходом второго элемента И, выход со счетным входом блока деления частоты, первый и второй входы изменения модуля коэффициента пересчетг которого соединены соответстве первой и второй дополнительным шинами управления.

Ч. С

/«

7

15

16

| Делитель частоты импульсов с переменным коэффициентом деления | 1978 |

|

SU769745A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ приготовления сернистого красителя защитного цвета | 1921 |

|

SU84A1 |

| Солесос | 1922 |

|

SU29A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Деревянный коленчатый рычаг | 1919 |

|

SU150A1 |

| Автоматический переключатель для пишущих световых вывесок | 1917 |

|

SU262A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-07—Публикация

1984-06-29—Подача