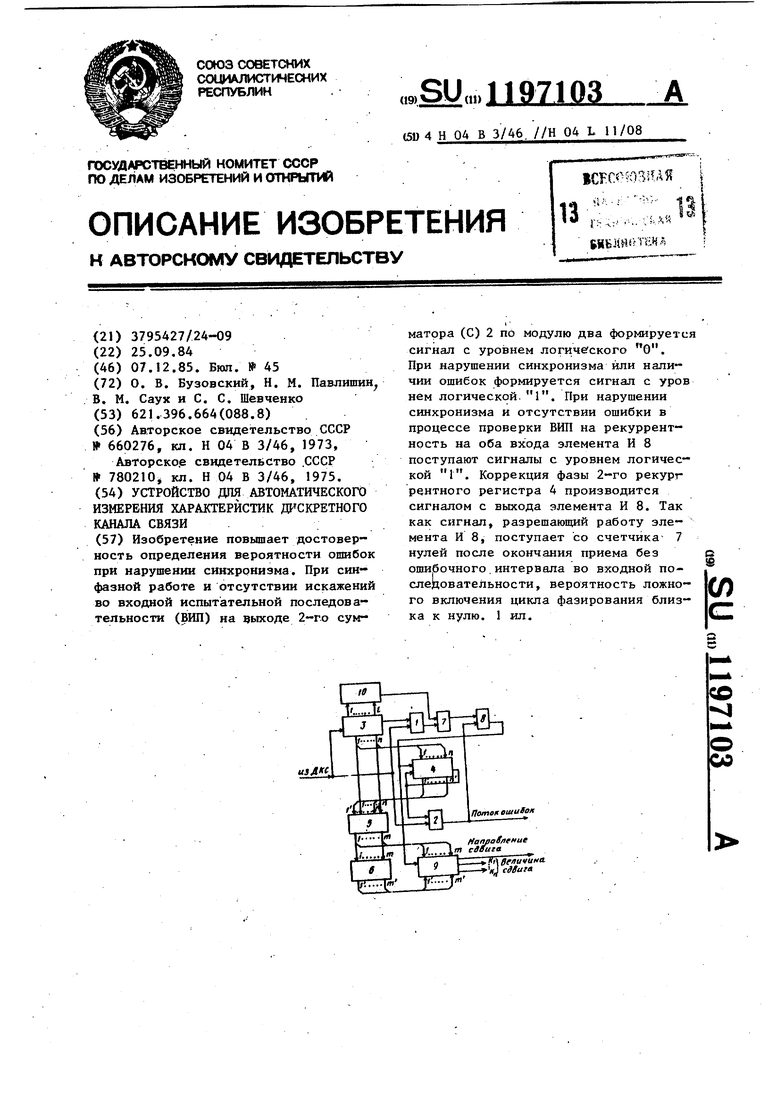

Изобретение относится к электро связи и может использоваться Для из мерения статистических характеристик дискретного канала связи (ДКС). Цель изобретения - повьгление дос- товерности определения вероятности ошибок в принимаемой информации при нарушении синхронизма. На чертеже изображена структурная электрическая схема устройства. Устройство для автоматического измерения характеристик дискретного канала связи содержит первый и второ лумматоры 1 и 2 по модулю два, первы ,второй рекуррентные регистры 3 и 4,постоннный запоминающий блок (ПЗВ 5,регистр 6 памяти, счетчик 7 нулей элемент И 8, блок 9 вычитания$ дешиф ратор 10 нулевого состояния. Устройство работает следугаш 1м образом. Исходное состояние устройства может быть произвольным и на процесс работы не влияет. Принимаемая испыта тельная последовательность с входа устройства поступает на вторые входы первого и второго сумматоров 1 и 2 по модулю два, а также на вход пер вого рекуррентного регистра 3, сигна с выхода которого поступает на первый вход первого сумматора 1 по мо дулю два. В первом сумматоре 1 по мо дулю два испытательная последователь ность проверяется на рекуррентность. Результат проверки с выхода первого сумматора 1 пр.модулю два поступает на счетчик 7 нулей. При соответствии испытательной последовательности рекуррентной последовательности на выходе первого сумматора ) по модулю два образуется нулевая последовательность, которая приводит к переполнению счетчика 7 нулей, сигнал с выхода которого разрешает работу элемента И 8. При не соответствии испытательной последова тельности рекуррентной последователь ности на выходе первого сумматора 1 по модулю два формируется сигнал, ус тан ав лив аюш;ий счетчик.7 нулей в ну левое состояние. Счетчик 7 нулей может быть установлен в нулевое состояние также сиг налом с выхода дешифратора 10 нулевого состояния в том случае, если на его входы поступит нулевая комбинация . Во втором сумматоре 2 по модулю два испытательная последовательность сравнивается с эталонной, поступающей со второго рекуррентного регистра 4, и результат этого сравнения, представляющий собой поток ошибок, поступает на выход устройства и на первый вход элемента И 8. При приеме каждого бита испытательный последовательности первый и второй рекуррентные регистры 3 и 4 поочередно подключаются к входам ПЗБ 5. В каждый данный момент времени на выходе ПЗБ появляется кодовая комбинация, опре- деляюп(ая номер такта, поступившего на вход первого ил.и второго рекуррентных регистров 3 и 4. Кодовая комбинация, определяющая номер такта , эквивалентного состоянию входной испытательной последовательности, записывается в регистр 6 памяти, с выходов которого она поступает на входы блока 9 вычитания. При синфазной работе и отсутствии искажений во, входной испытательной последовательности на выходе второго сумматора 2 по модулю два формируется сигнал с уровнем логического О. При нарушении синхронизма или наличии ошибок во входной испытательной последовательности на выходе второго сумматора 2 по модулю два формируется сигнал с уровнем логической 1. При нарушении синхронизма и от- сутствии ошибки в процессе проверки входной испытательной последовательности на рекуррентность, на оба входа элемента И 8 поступают сигналы с уровнем логической 1. На выходе элемента И 8 формируется сигнал вклю- чения цикла фазирования в процессе которого определяется величина и на правление расфазирования и корректи- руется фаза второго рекуррентного регистра 4. Величина и направление расфазирования определяются блоком 9 вычитания. Вычитание производится в двоичном коде. На первом выходе блока 9 вычитания формируется сигнал, указывающий на направление сдвига, на остальных выходах - сигналы, определяющие величину сдвига. Выходы блока 9 вычитания являются выходами устройства. Коррекция фазы второго рекуррентного регистра 4 производится сигналом с выхода элемента И 8 путем переза 3 писи входной испытательной последе - вательности с выхода первого рекурре тного регистра 3 во второй рекуррент ный регистр 4, Так как сигнал, раз- решающий работу элемента И 8 посту- пает со счетчика 7 нулей после окончания приема безошибочного интервала во входной последовательности, вероятность ложного включения цикла фазирования близка к нулю. Описанная схема позволяет определить наличие расфазирования за время 2 Т . N тч рр где Тт-ц - период Тактовой частоты; количество разрядог рекуррентного регистра) которое меньше времени, затрачиваемо го на определение состояния расфазирования в известном устройстве на ве личину N . N uto 2Т Т N рр РР 1-ТЧ р Вхождение в синхронизм производит ся в течение текущего такта в момент включения цикла фазирования, т.е. за время . Таким образом, уменьшение времени вхождения в синхронизм составляет величину .X.., тч ч C( dtt (М+1) где М - число бит принимаемой информации; . i - число вставленных или выпавших бит. . Формула изобретения Устройство для автоматического измерения характеристик дискретного 034 канала связи, содержащее последовательно соединенные первый рекуррентный регистр, дешифратор нулевого состояния и счетчик нулей, регистр памяти, первый сумматор по модулю два, первый вход которого соединен с сигнальным выходом первого рекур- .рентного регистра, второй рекуррент.ный регистр, сигнальный выход и первьй вход которого подключены к первому входу сумматора по модулю два, выход которого подключен к первому входу элемента И, отличающееся тем, что, с целью повышения дoctoвepнocти определения вероятности ошибок в принимаемой информации при нарушении синхронизма в не го введены последовательно соединенные постоянный запоминающий блок и блок вычитания, другая группа входов которого соединена с выходами постоянного запоминающего блока через регистр памяти, при этом, выход счетчика нулей подключен к второму входу элемента И, выход которого подключен к второму входу второго рекуррентного регистра и к управляющему входу блока вычитания, вторая группа выходов первого peKyppieHTHoro регистра подключена к группе входов второго рекуррентного регистра и к первой группе входов постоянного запоминающего блока, вторая группа входов которого соединена с группой выходов второго рекуррентного регистра, сигнальный вход первого рекуррентного регистра соединен : с вторыми входами первого и второго сумматоров по модулю, два, выход первого сумматора по модулю два подключен к второму . вькрду счетчика нулей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для автоматического измерения характеристик дискретного канала связи | 1983 |

|

SU1141578A2 |

| Устройство для автоматическогоизМЕРЕНия ХАРАКТЕРиСТиК диСКРЕТНОгОКАНАлА СВязи | 1979 |

|

SU809591A1 |

| Система формирования и приема телевизионного сигнала при передаче изображения | 1988 |

|

SU1555909A2 |

| Устройство фазирования по циклам | 1988 |

|

SU1601773A1 |

| Устройство для выделения ошибок из цифрового испытательного сигнала | 1988 |

|

SU1626400A1 |

| Устройство для автоматического измерения характеристик дискретного канала связи | 1975 |

|

SU780210A1 |

| Устройство для измерения статистических характеристик дискретного канала связи | 1975 |

|

SU558408A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ДОСТОВ^ЕЦ.ОСТИ ПЕРЕДАЧИ ДВОИЧНОЙ ИНФОРМАЦИИ | 1970 |

|

SU274152A1 |

| Устройство для контроля ошибок магнитной записи-воспроизведения цифровой информации | 1985 |

|

SU1273994A1 |

| УСТРОЙСТВО ДЛЯ ЦИКЛОВОЙ СИНХРОНИЗАЦИИ | 2005 |

|

RU2284665C1 |

Изобретение повышает достоверность определения вероятности ошибок при нарушении синхронизма. При синфазной работе и отсутствии искажений во входной испытательной последовательности (ВИЛ) на эыходе 2-го сумматора (С) 2 по модулю два формируется сигнал с уровнем логического О. При нарушении синхронизма или наличии ошибок формируется сигнал с урон нем логической. 1. При нарушении синхронизма и отсутствии ошибки в процессе проверки ВИП на рекуррентность на оба входа злемента И 8 поступают сигналы с уровнем логической 1. Коррекция фазы 2-го рекург рентного регистра 4 производится сигналом с выхода злемента И 8. Так как сигнал, разрешающий работу элемента И 8, поступает со счетчика 7 нулей после окончания приема без ошибочного.интервала во входной последовательности, вероятность ложного включения цикла фазирования близка к нулю. 1 ил. СО СО

| Устройство для автоматического измерения характеристик дискретного канала | 1976 |

|

SU660276A2 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1985-12-07—Публикация

1984-09-26—Подача