ка, регистра множителя, накапливающе го сумматора и регистра множимого, вход разрешения записи информации которого соединен с вторым выходом программного блока управления, третий и четвертый выходы которого соединены соответственно с входами разрешения записи информации регистра множителя и счетчика, входы разрешения умножения К матриц умножения, входы разрешения сложения (К-1) матриц суммирования и входы разрешения считывания (К-1) матриц суммирования и К-и матрицы умножения соединены соответственно пятым, шестым и седьмым выходами программного блока управления, восьмой, девятый и десятый выходы которого соединены соответственнЬ с входом разрешения записи информации накапливающего сумматора, с входом сброса {К+1)-го разряда регистра множителя и счетным входом счетчика, одиннадцатый, двенадцатый и тринадцатый выходы программного блока управления соединены соответственно с входами сдвига регистра множителя и накапливающего сумматора и входом разрешения записи знака накапливающего сумматора,

2. Устройство по п. 1, отличающееся тем, что программный блок управления содержит программируемый блок памяти, триггер, регистр, дешифратор, два элемента И, пять элементов НЕ и четыре элемента 2И-ИЛИ и генератор тактовых импулсов, выход которого соединен с первы входом первого элемента И, второй вход которого соединен с выходом триггера, а выход - с синхровходом регистра,-информаи юнные входы которого соединены с выходами программируемого блока памяти, первый, второй третий и четвертый адресные входы которого соединены соответственно с выходами первого, второго, третьего и четвертого элементов НЕ, входы которых соединены соответственно с выходами первого, второго, третьего и четвертого элементов 2И-ИЛИ, выходы первых п/2 разрядов регистра (п - разрядность регистра) соединены соответственно с информационными входами дешифратора, выход (п/2+1)-го разряда соединен с первым входом второго элемента И, второй вход которого соединен с первым входом программного блока управления, выход С входом пятого элемента НЕ и первым

входами всех элементов 2И-ИЛИ, вторые входы которых соединены с выходом пятого элемента НЕ, а третьи входы - с выходами (п/2+2)-го, (п/2+ +3)-го, (п/2+4)-го, (п/2+5)-го разрядов регистра соответственно, выходы (п/2+6)-го, (п/2+7)-го, (п/2+8)-го, (п/2+9)-го разрядов которого соединены соотве.тственно с четвертыми входами всех элементов 2И-ИЛИ, выходы дещифратора с первого по тринадцатый соединены соответственно с первого по тринадцатый выходами программного i блока управления, второй вход которого соединен с входом Пуск устройства и входом установки единицы , триггера, вход установки нуля которого соединен с четырнадцатым выходом дешифратора.

3. Устройство по п. 1, о т л и ч а ю-щ е е с я тем, что каждая матрица умножения содержит управляющий ключ, кодирующую (га х т)-ю матрицу узлов, каждый из которых выполнен в виде трех фoтoпpиe ffl:икoв (т 10 для десятичной системы счисления и определяет количество оптических каналов, из которых состоит каждый из выходов и входов матрицы умножения ), и два оптозлектронных модуля, состоящих из m регенеративных оптронов, каждый из которых выполнен в виде транзистора и оптически соединенных фотоприемника и светоизлучателя, причем в каждом из регенеративных оптронов первые выводы фотоприемника и светоизлучателя подключены соответственно к базе и к коллектору транзистора, эмиттер которого соединен с шиной нулевого потенциала, а вторые выводы подключены к шине пи тания через сигнальную цепь управляющего ключа, первые вьшоды первых фотоприемников в узлах кодирующей матрицы соединены с шиной питания, а вторые выводы - соответственно через вторые и третьи фотоприемники в узлах кодирующей матрицы с первыми и вторыми выходами соответствующих узлов кодирующей матрицы, которые соединены с базами транзисторов соответствующих регенеративных оптронов соответствующих оптозлектронных модулей таким образом, что первый выход (i, j)-ro узла кодирующей матрицы (i, j 0,1,.,., m-1) соединен с базой транзистора i-ro регенеративного оптрона оптоэлектронного модуля младшей цифры результата, а второй

выход (i, j)-ro узла кодирующей матрицы соединен с базой транзистора i-ro регенеративного оптрона опто- электронного модуля старшей цифры результата, j-й оптический канал первого информационного входа матрицы умножения соединен оптически с первыми фотоприемниками узлов j-го столба кодирующей матрицы, i-й оптический канал второго информационного ЭхоДа соединен оптически с вторыми и третьими фотоприемниками узлов i-й строки кодирующей матрицы, оптические выходы светоизлучателей регенеративных оптронов оптоэлектронных модулей младщей и старшей цифр результата соединены оптически с соответствующими оптическими каналами соответствующих выходов младшей и старшей цифр результата матрицы умножения, вход разрешения умножения которой соединен с управляющим входом управляющего ключа.

4, Устройство по п. 1, о т л ичающее.ся тем, что каждая матрица суммирования содержит управляющий ключ, кодирующую (га к т)-ю матрицу узлов, каждый из которых вьшолнен на трех фотоприемниках, регенеративный оптрон переноса, состоящий из транзистора, фотоприемника и светоизлучатёля, и оптоэлектрон ный модуль результата сложения,.состоящий из m регенеративных оптро- нов, каждый из которых содержит транзистор, фотоприемник и светоиз- лучатель и m управляющих фотоприемников, первые выводы которых подключены к входу разрешения считы-

98514

вания суммирования матрицы, а вторые - к соответствующим базам транзисторов соответствующих регенеративных оптронов оптоэлектронного модуля результата сложения, причем i-й управляющий фотоприемник i-ro регенеративного оптрона оптически соединен соответственно с (i+l)-M светоизлучателем (i+l)-ro регенеративного оптрона (i 1,,..,га-1), коллектор транзистора первого регенеративного оптрона оптозлектронного модуля результата сложения соединен с выходом суммы матрицы суммирования, регенеративные оптроны оптоэлектронного модуля результата сложения и . . регенеративный оптрон переноса сое;- динены через сигнальную цепь управляющего- ключа с шиной питания, i-й оптический канал первого информационного входа матрицы суммирования оптически соединен с первыми фотоприемниками узлов i-ro столбца кодирующей матрицы, j-й оптический канал второго входа информационной матрицы суммирования оптически соединен с вторым и третьим фотоприемниками узлов j-й строки кодирующей матрицы, первые выводы первых фотоприемников в узлах кодирующей матрицы соединены с шиной питания, а вторые выводы соединены через вторые фотоприемники в узлах кодирующей матрицы с базами соответствующих транзисторов регенеративных оптронов оптоэлектронного модуля результата сложения, вход разрешения сложения матрицы суммирования соединен с управляющим входом управляющего ключа.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1984 |

|

SU1249507A1 |

| Устройство для умножения десятичных чисел | 1981 |

|

SU1016780A1 |

| Оптоэлектронный сумматор | 1978 |

|

SU742936A1 |

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Оптоэлектронное устройство вычитания десятичных чисел | 1983 |

|

SU1136157A1 |

| Оптоэлектронный десятичный сумматор | 1978 |

|

SU840895A1 |

| Оптоэлектронный десятичный сумматор | 1978 |

|

SU796845A1 |

| Устройство для умножения в избыточной двоичной системе | 1982 |

|

SU1059568A1 |

| Устройство для умножения | 1980 |

|

SU960805A1 |

| УСКОРЕННЫЙ УМНОЖИТЕЛЬ НА НЕЙРОНАХ | 2006 |

|

RU2322688C2 |

1, УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ, содержащее регистр множимого, регистр множителя, накапливающий сумматор, узел анализа знаков и счетчик, причем входы множителя и множимого устройства соединены соответственно с информационными входами регистров множителя и множимого, выходы знаковых раз- рядов которых соединены с первым и вторым входами узла анализа знаков, отличающее ся тем, что, с целью повьпиения быстродействия, в него введены К матриц умножения (К - разрядность множителя и множимого), (К-1) матриц суммирования и программный блок управления, причем разрядные выходы регистра множимого соединены с первыми информационными входами К матрицы умножения, вторые информационные входы которых соединены с (К+1)-м выходом регистра множителя, (К+1)-й информационный вход которого соединен с К-м выходом регистра множителя, информационный вход младшего разряда которого соединен с выходом (К+1)-го разряда на- капливакщего сумматора, вход (К+1)-го разряда которого соединен с выходом старшей цифры результата умножения К-и матрицы умножения, выход старшей цифры результата умножения i-й матрицы умножения соединен с первым информационным входом i-й матрицы суммирования (i 1,...,К-1) второй информационный вход j-й матрицы суммирования соединен с выходом младшей цифры результата умножеi ния (J-1 )-й-матрицы умножения (j 2, 3,,..,К), выход младшей цифры (Л результата умножения первой матрицы., умножения соединен с информационным входом младшего разряда накапливающего сумматора, информационный вход знакового разряда которого соединен с выходом блока анализа знаков, вход j-ro разряда первого слагаемого насо капливающего сумматора соединен с вы00 ходом суммы 1-й матрицы суммирования ел соответственно, выход переноса которой соединен с выходом . разряда второго слагаемого накапливающего сумматора, входы знака множимого, знака множителя и кода разрядности множителя устройства соединены соответственно с входами знаковых разря дов регистров множимого и множителя и информационным входом счетчика, шина питания устройства соединена с шиной питания всех матриц умножения и суммирования, выход счетчика соединен с первым входом программного блока управления, первый выход которого соединен с входами сброса счетчи

Изобретение относится к, вычислительной технике и может быть исподь- зовано в оптоэлектронных устройствах. выполняющих операции над десятичными числами.

Цель изобретения - повышение быстродействия устройства для умножения десятичных чисел.

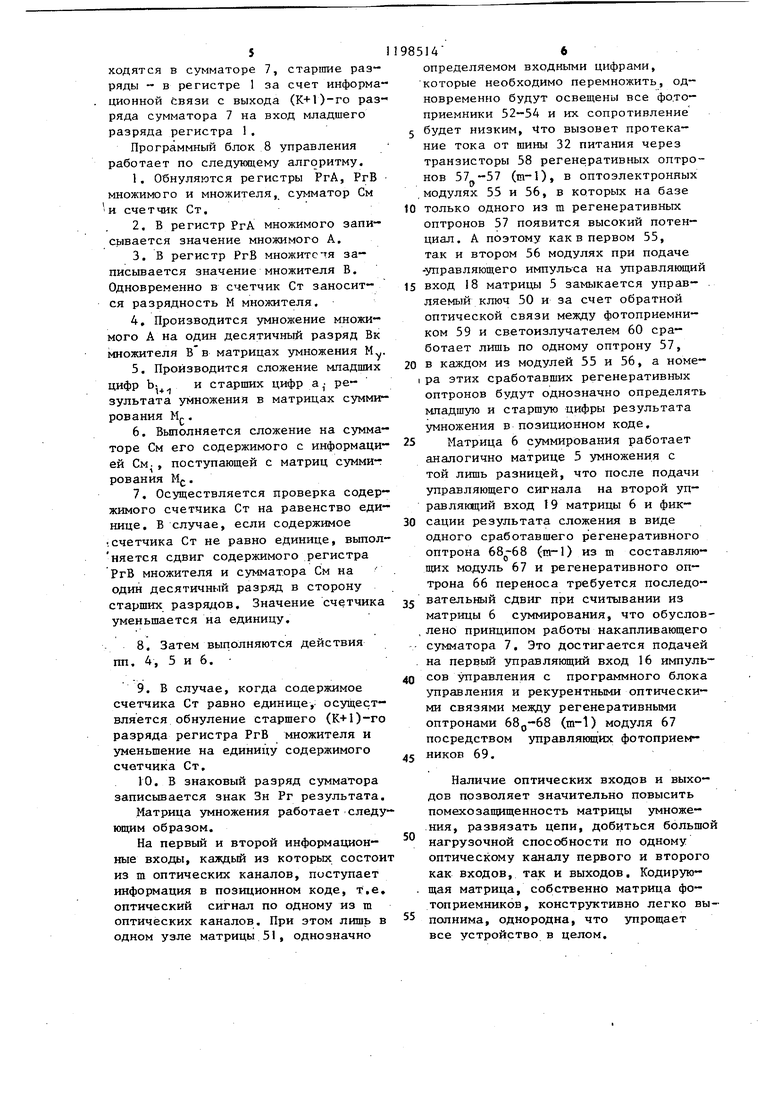

На фиг. 1 представлена блок-схема матричного оптоэлектронного устрой- ства для умножения десятичных чисел j на фиг. 2 - схема блока управления;

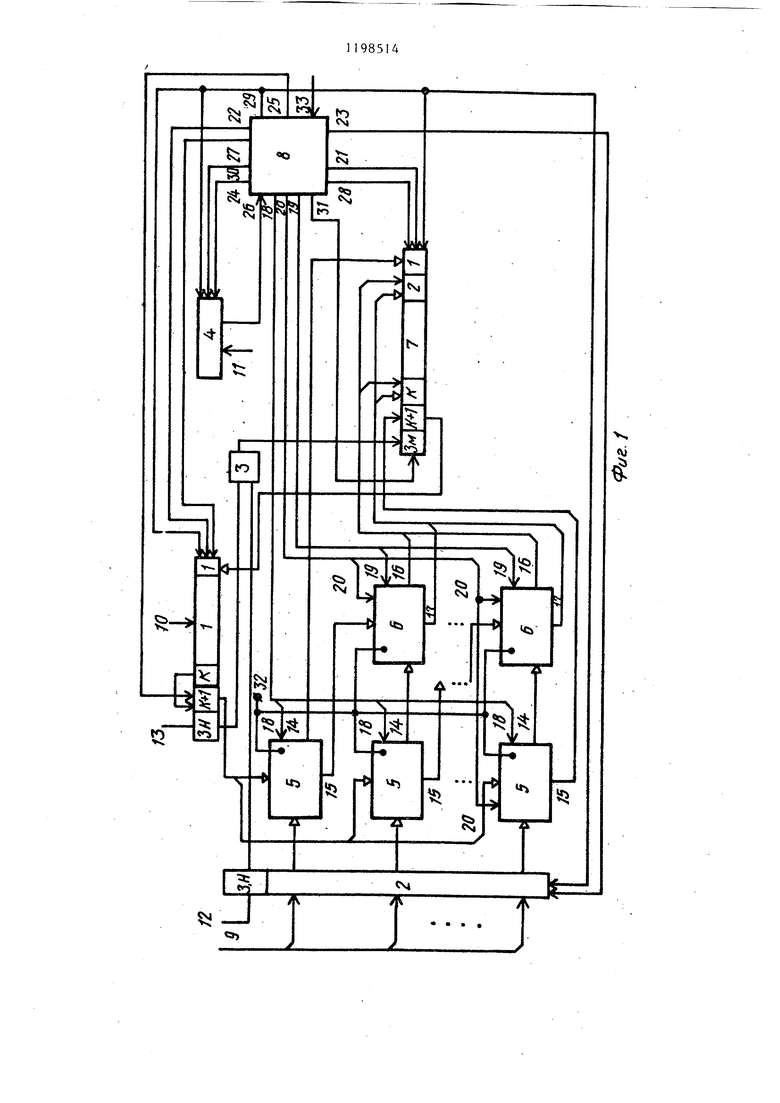

на фиг. 3 - схема матрицы умножения на фиг. 4 - схема матрицы сложения.

Устройство для умножения десятичных чисел (фиг. 1) содержит регистр 1 множителя, регистр 2 множимогоу узел 3 анализа знаков, счетчик 4, К матриц 5 умножения, (К-1) матриц 6 сложения, накапливающий сумматор 7, программный блок 8 згправления, входы множимого 9, множителя 10, кода разрядности множителя 11 устройства, входы знаков множимого 12 и чножите-

3

ля 13 устройства, выходы младшей 14 и старшей15 цифр результата матриц умножения, выходы суммы 16 и переноса 17 матриц суммирования, выходы 18-25, вход 26, выходы 27-31 программного блока зшравления, шину питания 32 устройства, вход Пуск 33 устройства, .

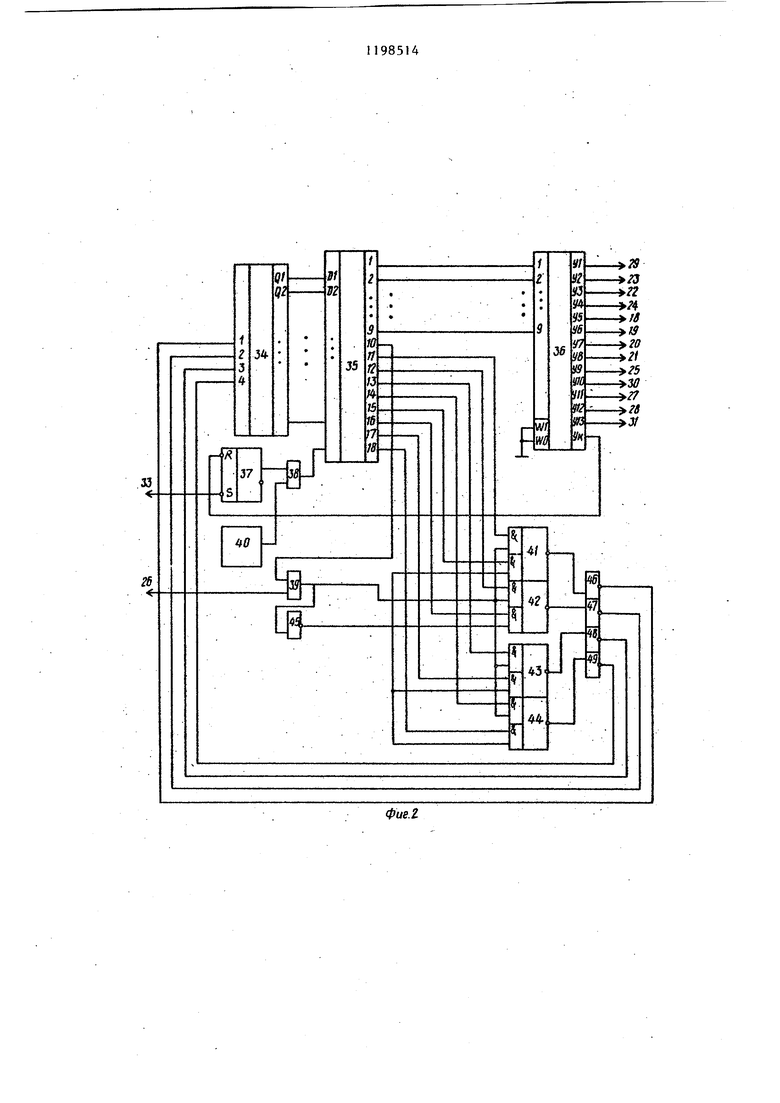

Программный блок управления (фиг, 2) содержит программируемый блок 34 памяти, регистр 35, дешифратор 36, триггер 37, два элемента И 38, 39, генератор тактовых им пульсов 40, четыре элемента 2И-ИЛ1 41-44, пять элементов НЕ 45-49,

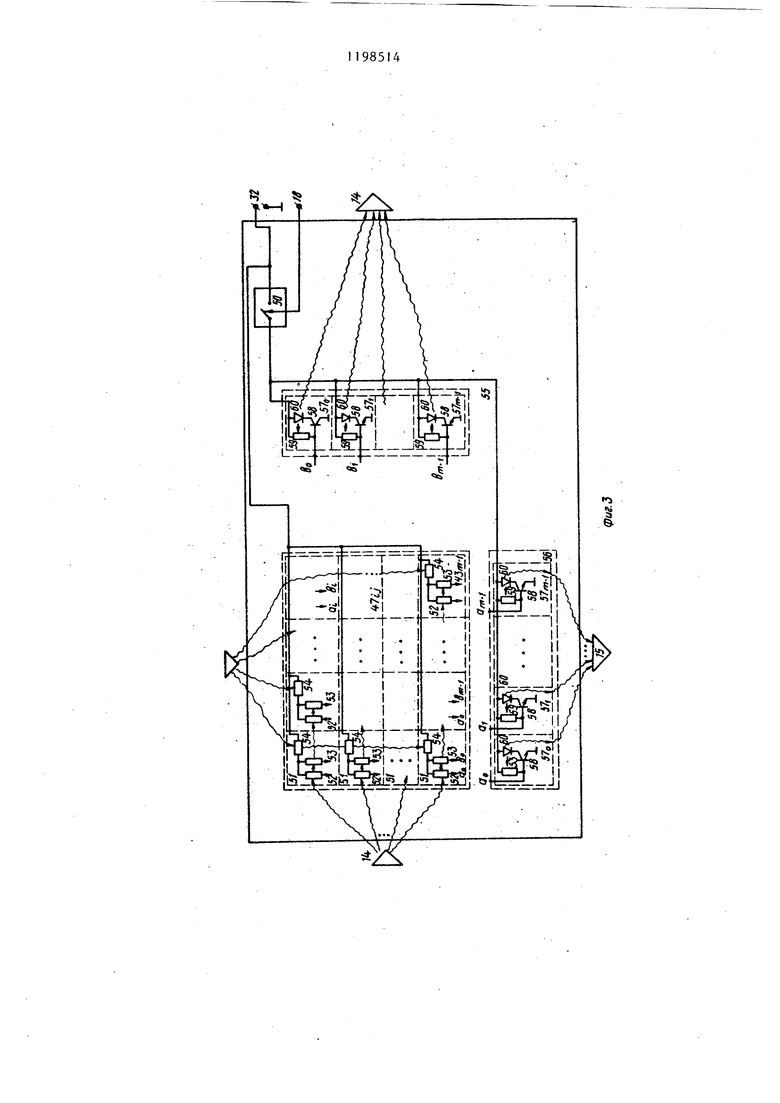

Матрица умножения (фиг, 3} содержит управляемый ключ 50,кодирующую (т X ni)-ro матрицу 51 узлов, три фотоприемника 52-54 узла кодирующей матрицы 51, оптоэлектронные модули 55 и 56,. га регенеративных оптронов 57 оптоэлектронных модулей 55 и 56, транзистор 58, фотоприемник 59 и светоизлучатель 60 регенеративных оптронов 57,

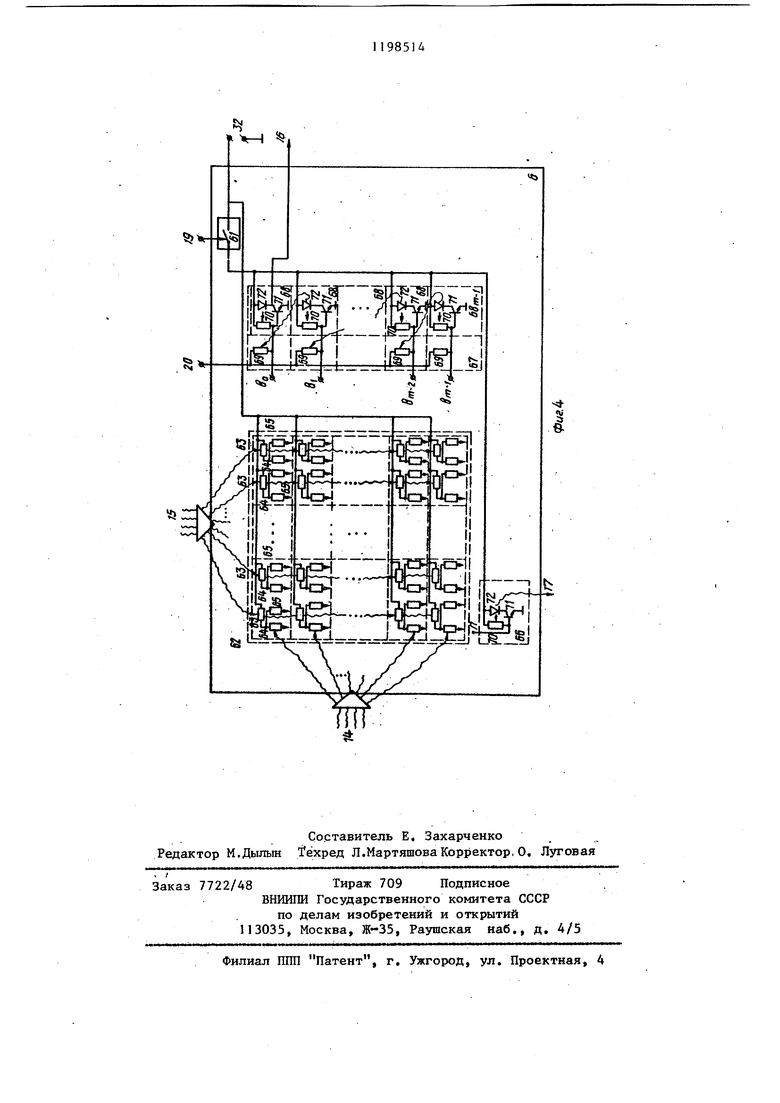

Матрица суммирования (фиг. 4) содержит управляемый ключ 61, кодирзда- щуто (т X та)-ю матрицу 62 узлов, три фотоприемника 63-65 узла кодирз ощей матрицы 62, регенеративный оптрон 66 переноса, оптоэлектронный модуль 67 результата сложения, п регенеративных оптронов 68 оптоэлектронного модуля 67, m управляющих фотоприемников 69 оптоэлектронного модуля 67, фотоприемник 70, транзистор 71 и светоизлучатель 72 регенеративных оптронов 66 и 68. .

Устройство для умножения десятичных чисел работает следующим образом

Множимое А записывается в регистр 2 множимого, множитель В - в регистр 1 множителя соответственно с входов 9 и 10 записи кода. Одновременно с входа 11 разрядность М множителя заносится в счетчик 4. Так как в (К+1)-м разряде регистра 1 находится старшая значащая цифра множителя В, то при наличии управляющего сигнала, поступающего на вход 18 матриц умножения, происходит срабатывание всех матриц 5 умножения. В результате этого появляется значение младшей цифры Ь. результата умножения на выходе14 всех матриц 5 умножения и значени старшей цифры а. результата умножени на выходе 15 всех матриц умножения, причем информация с выхода 14 первой матрицы 5 умножения и информация с

98514

выхода 15 старшей матрицы 5 умножения поступят соответственно на входы младшего и старшего разрядов сумматора 7. Остальная информация с выхода 14 поступает на вход первого

слагаемого матриц 6 суммирования таким образом, что с выхода 14 (1+1)-й матрицы 5 умножения информация поступает на вход первого слагаемого i-й

10 матрицы 6 суммирования, а информация с выхода 15 i-й матрицы поступает на вход второго слагаемого i-и матрицы 6 суммирования. Сложение информации в матрице 6 суммирования происходит

15 при поступлении управляющего сигнала на вход 19 каждой матрицы суммирования 6, Информация с матриц суммирования поступает на сумматор 7 только при наличии сигнала управления считывания, поступающего на управляющие входы 20 матриц 6 суммирования. При поступлении такого сигнала результат суммы операции сложения поступает с выходов 16 на входы суммы суммато25 Ра 7, начиная с второго и кончая

К-м разрядом, а информация о наличии единицы переноса поступает с выходов 17 матриц 6 cy шиpoвaния на входы переноса сумматора 7, начиная с второ

3Q го и кончая К-м разрядом,

В случае, если содержимое счетчика 4 не равно единице, в регистре 1 и сумматоре 7 осуществляется сдвиг на один десятичный разряд влево по уп- равляюпр м сигналам, поступающим на их входы 27 и 28 управления сдвигом, при этом, значение счетчика уменьшается на единицу по управлякицему сигналу с выхода 30 программного блока 8 управления. Вновь производится умножение множимого А на очередную цифру множителя В, Таким образом происходит умножение до тех пор, пока Содержимое счетчика 4 не станет раЪ- ным единице, о чем свидетельствует появление единичного сигнала на входе 26 программного блока В управления. Б этом случае происходит уменьшение на единицу содержимого счетчика 4 и обнуление (К+1)-го разряда

регистра 1 по управлягацему сигналу с выхода 25 программного блока 8 управления. Затем выполняется запись знака результата с выхода узла 3 анализа знаков в знаковый разряд сумматора 7 при наличии управляющего сигнала, поступающего с выхода 31 про-; граммного блока 8 управления. Младшие разряды результата зтножения наS

ходятСЯ в сумматоре 7, стартпие разряды - в регистре 1 за счет информационной связи с выхода (К+1)-го разряда сумматора 7 на вход младшего разряда регистра 1.

Программный блок 8 управления работает по следующему алгоритму.

И счетчик Ст.

.счетчика Ст не равно единице, выполняется сдвиг содержимого регистра

РгВ множителя и сумматора См на

один десятичный разряд в сторону старших разрядов. Значение счетчика

уменьшается на единицу.

Матрица умножения работает следующим образом.

На первый и второй информационные входы, каждый из которых состои из m оптических каналов, поступает информация в позиционном коде, т.е. оптический сигнал по одному из m оптических каналов. При этом лишь в одном узле матрицы 51, однозначно

98514 6

определяемом входными цифрами, которые необходимо перемножить, одновременно будут освещены все фо.то- приемники 52-54 и их сопротивление 5 будет низким, то вызовет протекание тока от шины 32 питания через транзисторы 58 регенеративных оптронов 57-57 (та-1), в оптоэлектронных .модулях 55 и 56, в которых на базе 10 только одного из m регенеративных оптронов 57 появится высокий потенциал. А поэтому как в первом 55, так и втором 56 модулях при подаче -управляющего импульса на управляющий 15 вход 18 матрицы 5 замыкается управ- . ляемый ключ 50 и за счет обратной оптической связи между фотоприемником 59 и светоизлучателем 60 сработает лишь по одному оптрону 57, 20 в каждом из модулей 55 и 56, а номеIра этих сработавших регенеративных оптронов будут однозначно определять младшую и старшую цифры результата умножения в позиционном коде.

25 Матрица 6 суммирования работает аналогично матрице 5 умножения с той лишь разницей, что после подачи управляющего сигнала на второй управляющий вход 19 матрицы 6 и фиксации результата сложения в виде одного сработавшего регенеративного оптрона (та-1) из m составляющих модуль 67 и регенеративного оп- трона 66 переноса требуется последовательный сдвиг при считывании из

матрицы 6 суммирования, что обуслов, лено принципом работы накапливающего сумматора 7. Это достигается подачей . на первьй управляющий вход 16 импульсов уттравления с программного блока управления и рекурентными оптическими связями между регенеративными оптронами 68о-68 (m-l) модуля 67 посредством управляющих фотоприем5 НИКОВ 69.

Наличие оптических входов и выходов позволяет значительно повысить помехозащищенность матрицы умноже- .ния, развязать цепи, добиться большой

0 нагрузочной способности по одному оптическому каналу первого и второго как входов, так и выходов. Кодирующая матрица, собственно матрица фотоприемников, конструктивно легко вы5полнима, однородна, что упрощает все устройство в целом.

it

| Кожемяко В | |||

| Д | |||

| и др | |||

| О реализа.ции алгоритмов умножения ri вычитания десятичных чисел на оптоэлектронных сумматорах | |||

| Изв | |||

| вузов | |||

| Приборостроение, 1976, Р 3, с | |||

| Способ крашения тканей | 1922 |

|

SU62A1 |

| Устройство для умножения десятичных чисел | 1981 |

|

SU1016780A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-12-15—Публикация

1984-02-01—Подача