ности множимого и произведения подключен к выходу признака нулевого множимого устройства, управляющие входы регистров фиксации разрядности множителя, множимого и произведения подключены к второму управляющему входу устройства, выходы всех разрядов регистра множимого подключены ,к соответствующим первым группам информационных входов регистров кратных множимого, вторая группа информационных входов i-ro (,... 9) регистра кратных множимого. подключена к первой группе выходов(i -1) -го регистра кратных множимого, выходы первой группы второго регистра кратных множимого подключены к соответствующим информационным входам третьей группы четвертого регистра кратных множимого, выходы первой

группы которого подключены к.соответствующим информационным входам третьей группы шестого, седьмого и восьмого регистров кратных множимого, выходы первой группы шестого регистра кратных множимого подключены к соответствующим информационным входам четвертой группы восьмого регистра кратных множимого, выходы вторых групп всех регистров кратных множимого подключены к соответствующим информационным входам сумматора, входы управления суммированием всех регистров кратных множимого подключены к шине .суммирования устройства, выхсды сумматора являются выходами младших разрядов произведения устройства, а выходы регистра множимого являются выходами старших разрядов произведения устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Устройство для умножения | 1984 |

|

SU1249507A1 |

| Устройство для умножения чисел | 1989 |

|

SU1817091A1 |

| Устройство для умножения | 1982 |

|

SU1229758A1 |

| Устройство для умножения | 1989 |

|

SU1668979A1 |

| Устройство для умножения | 1987 |

|

SU1509875A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1198514A1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Устройство для умножения | 1985 |

|

SU1278838A1 |

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДЕСЯ ТИЧНЫХ ЧИСЕЛ, содержащее регистр множителя, регистры кратных множимого и сумматор, отличающееся тем, что, с целью повьшения однородности устройства и сокращения аппаратных затрат, оно содержит регистр множимого, блок преобразот вания Десятичной цифры из единичного нормального в единичный поэиционнь«й код, два счетчика разрядности, регистр фиксации разрядности Множителя, регистр фиксации разрядности множимого и произведения и два элемента И, причем информационные входы регистров множителя и множимого подключены к соответствующим входгал множителя и множимого устройства, выходщ старшего десятичного разряда регистра множителя соединены с соответствующими информационными входами блока преобразования десятичной цифры из единичного нормального .в единичный позиционный код, управляющий вход которого подключен к входу модуляции устройства, информационные выходы блока преобразования десятичной цифры из единичного. нормального в единичный позиционный код подключены к соответствующим управляющим входам регистров кратных множимого, a управлякиций выход блока преобразования десятичной цифры из единичного нормального в единичный ПОЗИЦИОННЫЙ код - к первым управляющим входам регистров множителя и множимого и сумматора, вторые управляющие входы которых подключены к первому управляющему входу устройства, выходы всех десятичных разрядов регистра множителя подключены к соответствующим входам первого счетчика разрядности, выходы которого подключены к соответствующим информационнным вхЬдгм регистра фиксаций раз,рядности множителя, (Л выход стариегб разряда которого подкгаочен к выходу фиксации окончания операции сдвига устройства, a выход младшего разряда - к выходу признака нулевого множителя устройства, выхсзд знака регистра множителя подключен к первс 4у входу первого элемента и, вто|юй вход которого подключен к выходу знака регистра мнoжи 4oro, a выход - к входу СП знака регистра множимого, выходил всех десятичных разрядов регистра м множимого подключеЕол к соответствую00 щим входгм первой группы второго счётчика разрядности, входы второй группы которого подключены к выходам соответствующих десятичшлх разрядов cyMviaTOpa, выходы второго счетчика разрядности подключены к соответствующим инфОЕллационным входам регистра фиксации разрядности множимого и произведения, выход переполнения которого подключен к первому входу второго элемента И, второй, вкод которого соединен с ВЫХОДОК старшего разряда сумматора, a выход - с входом младшего разряда регистра миожи юго, выход младшего разряда регистра фиксации разряд

1

Изобретение относится к вычисли- . тельной технике и может быть использовано в оптоэлектронных арифметических устройствах, выполняющих операции над десятичными числами с j фиксированной запятой.

Известно устройство для умножения десятичных чисел, содержащее регистр множителя, блок формирования множимого, сумматор, блок управления, 10 первый выход которого соединен с входом управления регистра множителя, выход которого связан с входом блока управления, второй выход которого .соединен с входом управления сумматора, информационные входы ко-, торого соединены с информационными выходами блока формирования множимого, первый и второй входы управления которого соединены соответственно с третьим и четвертым вы- 20 ходами блока управления, информационные входы дополнительного регистра связаны с инфррмационными рыходами младших тетрад блока формирования множимого, информацион- 25 ные входы старших тетрад которого подключены к выходам дополнительного регистра, к управлякяцему входу которого подключен пятый вход блока управления

Умножение осуществляется за число циклов, равное разрядности десятичных операндов, при этом в каждом цикле осуществляется умножение множимого на один десятичный разряй- jj множителя, начиная с гдладшего. Таким образом, к недостатку данного устройства можно отнести значительное время, затрачиваемое на операцию умножения, поскольку каждый

цикл состоит из четырех тактов, по: числу разрядов представления десятичных цифр в -двоично-десятичной системе 8-4-2-1.

Наиболее близким к предлагаемому является устройство умножения десятичных чисел, содержащее регистр множителя, сумматор, восемь дополнительных регистров для хранения кратгых множимого и девять схем сравнения, входы которых соединены с выходом младшего разряда регистра множителя и выходом разряда признака соответствующих регистров хранения кратных множимого, причем выходы девят регистров хранения кратных множимого чере-з соответствующие схемы сравнени подключены к входу сумматора. Выходы каждого регистра хранения кратных множимого, кроме девятого, соединены с входом следующего соседнего регистра 2.

Недостатком такого устройства является необходимость использования девяти схем сравнения, а также последовательное формирование девяти кратных множимого на соответствующих регистрах; что в конечном счете ограничивает быстродействие оптоэлектронного устройства умножения.

Цель изобретения - повышение однородности устройства для умножения десятичных чисел и снижение аппаратных затрат.

Поставленная цель достигается тем, чтоустройство для умножения десятичных чисел, содержащее регистр множителя, регистры кратных множимого и сумматор, содержит регистр множимого, блок преобразования десятичной цифры, счетчика разрядноети, регистр фиксации разрядности множителя, регистр фиксации разрядности множимого и произведения и два элемента И, причем информационные входы регистров множителя и множимого подключены к соответствующим входам множителя и множимого устройства, выходы старшего десятичного разряда регистра множителя соединены с соответствующими информационными входами блока преобразования десятичной цифры из единичного нормального в единичный позиционный код, управляющий вход которог подключен к входу модуляции устройства, информационные выходы блока преобразования десятичной цифры из единичного нормального в единичный позиционный код подключены к соответствующим управляющим входам регистров кратных множимого, а управляющий выход блока преобразования десятичной цифры из единичного нормального в единичный позиционный код - к первым управляющим входам регистров множимого и множителя и сумматора, вторые управляйидае входы которых подключены к первому управляющему входу устройства, выходы всех десятичных разрядов регистра множителя подключены к соответствующим входам первого счетчика разрядности , выходы которого подключены к соо.тветствующим информационным . входам регистра фиксации разрядности множителя, выход старшего разрйда которого подключен к выходу фиксации окончания операции сдвига устройства, а выход младшего разряда к выходу признака нулевого множителя устройства, выход знака регистра множителя подключен к первому входу первого элемента И, второй вход которого подключен к выходу знака регистра множимого, а выход к входу знака регистра множимого, выходы всех десятичных разрядов регистра множимого подключены к соответств5пощим входам первой группы второго .счетчика разрядности, входы второй группы которого подключены к выходам соответствующих десятичных разрядов сумматора, выходы второго счетчика разрядности подключены к соответствующим информационным входам регистра фиксации разрядности множимого и произведения, выход переполнения которого подключен к первому входу второго элемента И, второй вход которого соед{1нен с выходом старшего разряда сумматора, а выход - с входом младшего разряда регистра множимого, младшего разряда регистра фиксации разрядности множимого.и произведения подключен к выходу признака нулевого множимого устройства, управляющие входы регистров фиксаций разрядности множителя, множимог

и произведения подключены к второму управляющему входу устройства, выходы всех разрядов регистра множимого подключены к соответствующим информационным входам первых групп

регистров кратных множимого йнформационЕЯле входы второй группы i-ro (,...9) регистра кратных множимого подключены к соответствующим выходам первой группы (i - 1)-го реQ гистра кратных множимого, выходы

первой группы второго регистра кратных множимого подключены к соответствующим информационным входам третьей группы четвертого регистра кратных множимого, выходы первой группы

5 которого подключены к соответствующим информационным входам третьей группы шестого, седьмого и восьмого регистров кратных множимого, выходы первой группы шестого регистра

0 кратных множимого подключены к соответствующим информсщионшым входам четвертой группы восьмого регистра кратных 4Hoжимoгo, выхода вторых групп всех регистров кратных множи 5 мого подключены к соответствующим информационным входам сумматора, входы управления, суммирования всех регистров кратных множимого подключены к шине суммирования устройства,

0 выходы сумматора являются, выходами младших разрядов произведения устройства, а выходы регистра множимого являются выходами старших разрядрв произведения устройства.

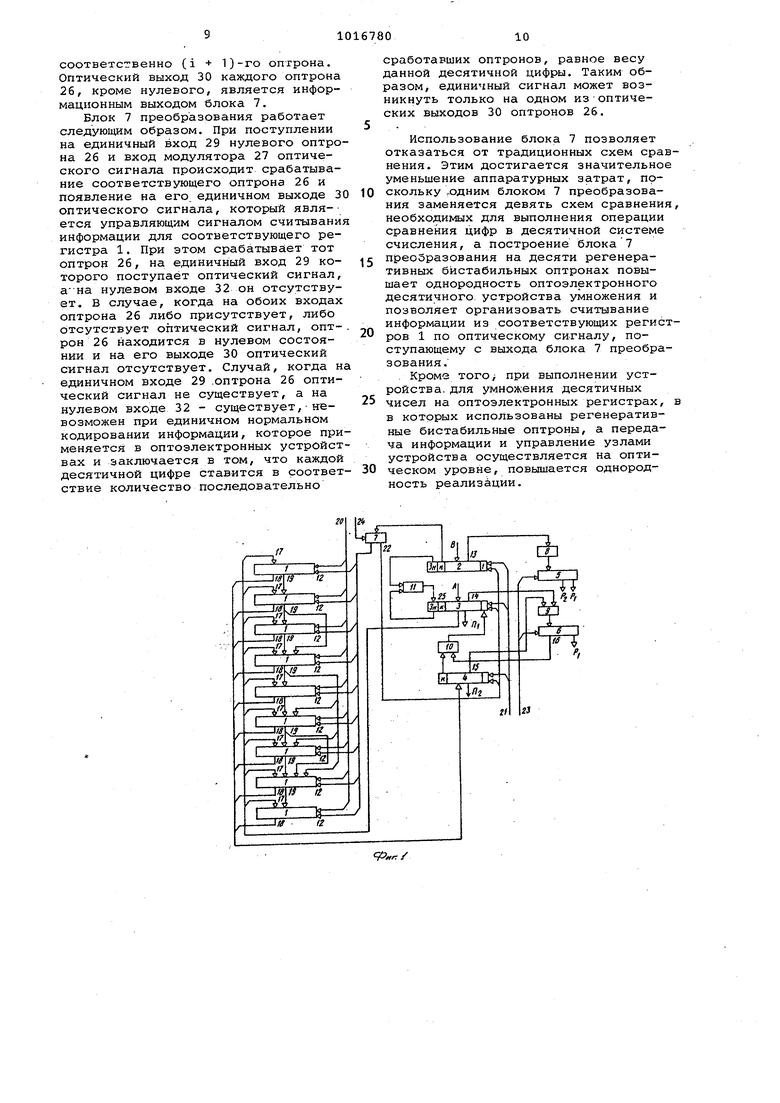

На фиг, 1 представлена блок-схема устройства-для умножения десятичных чисел; на фиг. 2 - структурная схема блока преобразования десятичной цифры из единичного нормального кода в единичный позиционный KOfi,

0 Устройство умножения содержи.т девять регистров 1 кратных множимого, регистр 2 множителя, регистр 3 множимого, сукалатор 4, регистр 5 фиксации разрядности множителя, регистр б фиксации разрядности множйMQro и произведения, блок 7 преобразования десятичной цифры, счетчики 8 и 9 разрядности и элементы И 10 и 11. Выходы ст аршего К-го десятичного разряда регистра 2 соединены через блок 7 преобразования десятичной цифры с управляющими входами первой группы 12 девяти регистров 1 кратных множимого, а выходы

г 13 регистра 2 через счетчик 8 разрядности - с входом регистра 5 фиксации разрядности множителя. Выходы 14 регистра 3 множимого и выходы 15 сумматора через счетчик 9 разрядности связаны с входами регистра 6

0 фиксации разрядности множимого и произведения, выходы 16 которого и выход старшего К-го десятичного разряда сумматора 4 через элемент И 10 соединены с входсш младшего десятичного разряда регистра 3 множимого. 5 Выходы регистра 3 множимого соедине ны с 17 девяти регистров 1 кратных множимого. Информационные выходы 18 первой группы которых свя заны с входами сумматора 4, а информационные выходы 19 второй группы с входами 17 соответствующих соседних старших регистров 1. Причем выходы 19 второго регистра 1 соединены также с входами 17 четвертого регистра 1, выходы 19 которого связаны с входами 17 шестого седьмого и восьмого регистров-1, а выходы 19 шестого регистра 1 - свходами 17 восьмого регистра 1. Шина 20 суммирования подключена к входам управления суммирования-девяти регистров 1, первый управляющий вход 21 и выход 22 блока 7 преобразования десятичной цифры - к управляющим входам регистров 2 и 3 и сумматора 4. -Второй управляющий вход 23 соединен с управляющими входами регистров 5 и 6, у которых выходы младших разрядов являются выходами признака нулевого сомножителя, а выход старшего разряда регистра 5 является выходом признака фиксаций окончания операций сдвига в регистре 2. Вход 24 блока 7 является его управляющим входом. Выходы знака регистров 2 и 3 через элемент И 11 соединены с входом 25 знакового разряда регистра 3 множимого. По входам множителя и мнйжимо го устройства В и А в регистры 2 и поступают соответственно множитель и множимое А. С выходов П и П регистра 3 и сумматора 4 снимаются зн чения соответсвенно старших и Ь4ладших разрядов произведения. Устройство реализует следующий алгоритм умножения десятичных чисел 1.Проверяется равенство множимо го и множителя нулю. В случае, если один из сомножителей или оба сомножителя равны нулю, результату присваивается нулевое значение и опера ция умножения прекращается. В противном случае формируются кратные множимого на соответствующих регист рах и знак результата, который буде положительным при совпадении знаков сомножителей и отрицательным при их несовпадении. Одновременно производится сдвиг содержимого регистра мн жителя в сторону старших разрядных ячеек до тех пор, пока в старшей разрядной ячейке не появится старша значащая цифра множителя. 2.Производится одновременное сравнение цифры старшего разряда множителя и номера каждого кратного множимого. 3.При совпадении цифры старшего разряда множителя и данного номера одного из кратных множимого осуществляется суммирование соответствующего кратного множимого с содержа0нием сумматора и последующий сдвиг в сторону старших разрядных ячеек содержимого сумматора и регистра множителя. 4. Для каждого разряда множителя повторяются действия пунктов 2 и 3 до тех пор, пока не будет произведено умножение на всех разрядах множителя. Устройство для умножения десятичных чисел работает следующим образом. Множимое А записывается в регистр 3 множимого, множитель В - в регистр 2 множителя. Одновременно с записью сомножителей по управляющим сигналам, поступающим по второму управляющему входу 23 на управляющие входы регистров 5 и б, производится подсчет и запись разрядности сомножителей. Количество разрядов регистров 5 соответствует количеству десятичных разрядов регистра 2 множителя, а количество разрядов регистра б - суммарному количеству десятичных разрядов регистра 3 множимого и сумматора 4. Подсчет разрядности сомножителей выполняется по количеству сработавших десятичных разрядов регистров 2 и 3. При этом счетчиками 8 и 9 разрядности учитывается возможность появления значащих нулей в десятичных разрядах регистров 2 и 3, а равенство сомножителей нулю определяет наличие единицы в младшем разряде регистров 5 и 6 (признак Р). В этом случае операция умножения прекращается. В случае, когда ни один из сомножителей не равен нулю (Р-, 0), происходит формирование девяти кратных множимого на соответствующих регистрах 1 и знака произведения элементом И 11; знак произведения записывается по входу 25 в знаковый разряд регистра 3. Процесс формирования девяти кратных ножимого за пять тактов можно проиллюстрировать следующей таблицей, где проставляется кратность формируемых на регистрах 1 кратных множимого. первом такте во все девять регистров 1 по входам 17 записывается множимое А (его кратность равна 1 ) с выходов регистра 3, все десятичные разряды которого осле этого устанавливаются в ноль.

кроме знакового, по управляющей последовательности, поступающей по. входу 21. Во втором такте происходит суммирование содержимого регистра 1, номера которых являются чгетными, с содержимым соответствующего предыдущего регистра 1 и получение удвоенного значения множимого А ( кратностью 2 ). Во время третьего такта происходит суммирование содержимого третьего, четвертого, седьмого и восьмого регистров 1 с информацией, поступающей с выхода 19 второго и шестого регистров 1 и т.д. Суммирование на регистрах 1 осуществляется при поступлении сигналов на управляющие входы 12 соответствующих регистров 1 по шине 20 суммирования. Одновременно с образованием в массиве регистров 1 девяти кратных множимого осуществляется сдвиг множителя В в регистре .2 множителя в сторону старших разрядов по сигналу, поступающему на управляющий вход по входу 21, Сдвиг осуществляется до тех пор, пока в самом старшем К-ом десятичном разряде регистра 2 не появится старшая значащая цифра множителя В, что фиксируется сигналом Р / сн 1маемым со старшего разряда регистра 5 фиксации разрядности множителя. После этого при условии, что в массиве регистров 1 сформированы кратные множимого, и при наличии сигнала, поступающего на вход модуляции 24 блока 7, производится преобразование десятичной цифры, записанной в старшем К-ом десятичном разр:аде регистра 2 в единичном нормальном коде, в единичный позиционный код, особенностью которого является наличие единицы в той позиции, вес которой соответствует значению цифры, а нуль кодируется единицей в нулевом разряде. Информационные выходы блока 7 соединены с соответствующими управляющими входами 12 регистров 1 таким образом, что наличие единицы в определенной весовой позиции, соответствующей значению десятичной цифры в К-ом разряде регистра 2, вызывает считывание информации из соответствующего регистра 1 по выхсэдам 18 в сумматор 4с сохранением записанной в данном регистре 1 информации. Например, нахождение цифры 6 в К-ом разряде регистра 2 приведет при наличии сигнала на входе 24 модуляции блока 7 преобразования к появлению единицы в б-ом разряде блока 7, которая, в свою очередь, вызовет считывание информации в сумматор 4 из шестого регистра 1, где хранится шестикратное множимое А, Длительность управляющего сигнала, поступающего на вход 24 модуляции блока 7 преобразования, соответствует времени считывания информации из соответствующего регистра 1 и сдвига информации на один разряд, которое не зависит от разрядности записанной в регистрах информации, а определяется временем, необходимым для считывания наибольшей цифры, которой в десятичной системе счисления является 9. Таким образом осуществляется умножение на любую десятичную цифру. По

0 окончании перезаписи информации из соответствующего регистра 1 в сумматор 4, т,е, после прекращения действия управляющего сигнала на входе 24 блока 7 по сигналу, посту5пающему по входу 21 на .управляющие входы регистра 2 и сумматора 4, в последних происходит сдвиг содержимого в сторону старших десятичных разрядов. Затем вновь осуществляется умножение на очередную деся0тичную цифру множителя В. В случае, если в К-ом разряде регистра 2 десятичная цифра является нулем, наличие единицы в нулевом разряде блока 7 приводит лишь к сдвигу влй5во содержимого сумматора 4 и регистра 2, Поскольку уменьшение разрядности множителя В фиксируется на регистре 5 после каждого сдвига влево,содержимого регистра 2, то

0 появление единицы в нулевом разряде регистра 5 (Р 1 свидетельствует об окончании операции умножения. В какой-то момент при умножении возможно переполнение разрядной сетки

5 сумматора 4, Этот момент фиксируется регистром 6, сигнгш с выхода 16 которого на выходэлемента И 10 разрешает, связь с выхода старшего К-го десятичного разряда сумматора 4 на вход младшего десятичного разряда

0 регистра 3 таким образом, что дальнейшая перезапись информации из соответствующего регистра 1 производится в сумматор с удвоенной разрядной сеткой, состоящей из сумматора 4

5 и регистра 3, Информация, зафиксированная в .регистре б, дает представление о разрядности результата умножения,

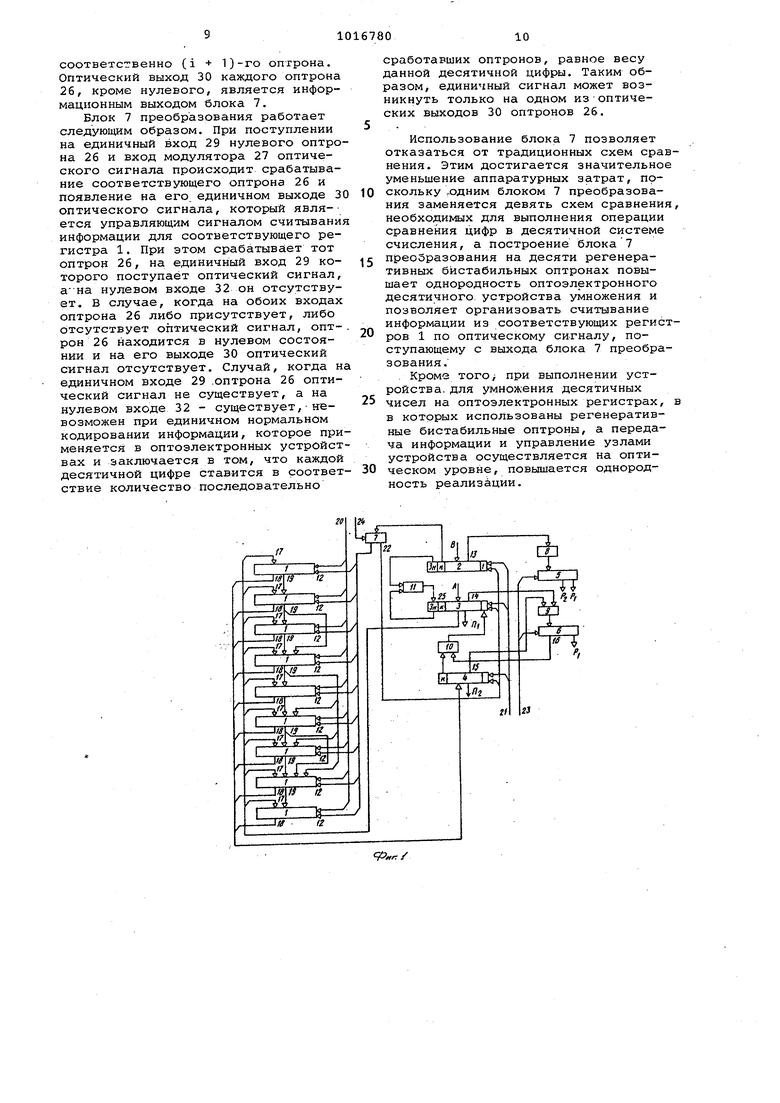

БЛОК 7 преобразования может .быть

0 реализован на десяти регенеративных бистабильных оптронах 26 с нсмергили позиций от О до 9 и модуляторе 27, выход 28 которого подключен к электрическим входам всех оптронов 26. Еди5ничный оптический вход 29 нулевого оптрона 26 и вход модулятора 27 подг ключены к управляющему входу блока 7, а единичный оптический выход 30 нулевого оптрона 26 является выходом 22 блока 7 преобразования. Единичный

0 оптический вход 29 каждого i-ro оптрона 26, кроме нулевого, является информационным входом 31 блока 7, нулевой оптический вход 32 соединен с единичным оптическим входом 29

5

соответственно (i + 1)-го оптрона. Оптический выход 30 каждого оптрона 26, кроме нулевого, является информационным выходом блока 7.

Блок 7 преобразования работает следующим образом. При поступлении на единичный вход 29 нулевого оптрона 26 и вход модулятора 27 оптического сигнала происходит срабатывание соответствующего оптрона 26 и появление на его. единичном выходе 30 оптического сигнала, который явля- ется управляющим сигналом считывания информации для соответствующего регистра 1. При этом срабатывает тот оптрон 26, на единичный вход 29 которого поступает оптический сигнал, а-на нулевом входе 32 он отсутствует, В случае, когда на обоих входах оптрона 26 либо присутствует, либо отсутствует оптический сигнал, оптрон 26 находится в нулевом состоянии и на его выходе 30 оптический сигнал отсутствует. Случай, когда на единичном входе 29 .оптрона 26 оптический сигнал не существует, а на нулевом входе 32 - существует,невозможен при единичном нормальном кодировании информации, которое применяется в оптоэлектронных устройствах и заключается в том, что каждой десятичной цифре ставится в соответствие количество последовательно

сработавших оптронов, равное весу данной десятичной цифры. Таким образом, единичный сигнал может возникнуть только на одном из оптических выходов 30 оптронов 26,

Использование блока 7 позволяет отказаться от традиционных схем сранения. Этим достигается значительно уменьшение аппаратурных затрат, поскольку .одним блоком 7 преобразования заменяется девять схем сравнени необходимых для выполнения операции сравнения цифр в десятичной системе счисления, а построение блока 7 преобразования на десяти регенеративных бйстабильных оптронах повышает однородность оптоэлектронного десятичного устройства умножения и позволяет организовать считывание информации из соответствующих регисров 1 по оптическому сигналу, поступающему с выхода блока 7 преобразования.

Кроме ТОГО; при выполнении устройства, для умножения десятичных чисел на оптоэлектронных регистрах, в которых использованы регенеративные бистабильные оптроны, а передача информации и управление узлами устройства осуществляется на оптическом уровне, повышается однородность реализации.

7J

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для умножения десятичных чисел | 1976 |

|

SU652560A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| и др | |||

| О реали:зации алгоритмов умножения и вычитания десятичных чисел на оптоэлектронных сумматорахi - Известия зузов | |||

| Планшайба для точной расточки лекал и выработок | 1922 |

|

SU1976A1 |

| Способ крашения тканей | 1922 |

|

SU62A1 |

Авторы

Даты

1983-05-07—Публикация

1981-12-18—Подача