го- подключен к выходу генератора кратных множимого, а выход соединен с информационным входом накапливающего сумматора, выход старшего информационного разряда регистра множителя соединен с входом дешифратора, нулевой выход которого подключен

к третьему входу программного блока управления, а остальные выходы - к управляющим входам коммутатора, выход регистра разрядности множителя соединен с четвертым вхо-. дом программного .блока управления.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1984 |

|

SU1249507A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1198514A1 |

| Устройство для умножения десятичных чисел | 1981 |

|

SU1016780A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Устройство для умножения | 1981 |

|

SU1012245A1 |

| Устройство для умножения чисел | 1990 |

|

SU1714595A1 |

| Устройство для умножения и деления с плавающей точкой | 1985 |

|

SU1278837A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

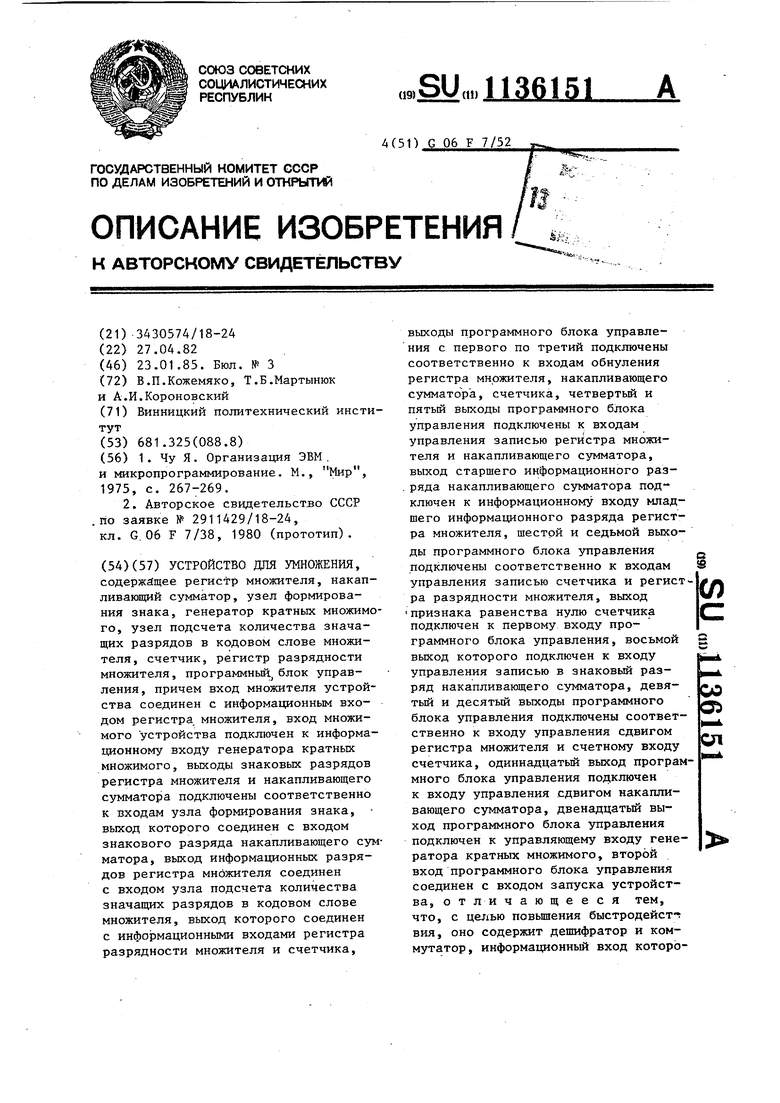

УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ, содержащее регистр множителя, накапливающий сумматор, узел формирования знака, генератор кратных множимого, узел подсчета количества значащих разрядов в кодовом слове множителя, счетчик, регистр разрядности множителя, программный, блок управления, причем вход множителя устройства соединен с информационным входом регистра, множителя, вход множимого устройства подключен к информационному входу генератора кратных множимого, выходы знаковых разрядов регистра множителя и накапливающего сумматора подключены соответственно к входам узла формирования знака, выход которого соединен с входом знакового разряда накапливающего сумматора, выход информационных разрядов регистра множителя соединен с входом узла подсчета количества значащих разрядов в кодовом слове множителя, вькод которого соединен с информационными входами регистра разрядности множителя и счетчика. выходы программного блока управления с первого по третий подключены соответственно к входам обнуления регистра множителя, накапливающего сумматора, счетчика, четвертьй и пятый выходы программного блока управления подключены к входам управления записью регистра множителя и накапливающего сумматора, выход старшего информационного раз. ряда накапливающего сумматора подключен к информационному входу младшего информационного разряда регистра множителя, шестой и седьмой выходы программного блока управления подключены соответственно к входам управления записью счетчика и регист(Л ра разрядности множителя, выход признака равенства нулю счетчика подключен к первому входу программного блока управления, восьмой выход которого подключен к входу управления записью в знаковый разряд накапливающего сумматора, девясо а тый и десятый выходы программного блока управления подключены соответственно к входу управления сдвигом ел регистра множителя и счетному входу счетчика, одиннадцатьй выход программного блока управления подключен к входу управления сдвигом накапливающего сумматора, двенадцатьй выход программного блока управления подключен к управляющему входу генератора кратных множимого, второй вход программного блока управления соединен с входом запуска устройства, отличающееся тем, что, с целью повышения быстродейстВИЯ, оно содержит дешифратор и коммутатор, информационный вход которо

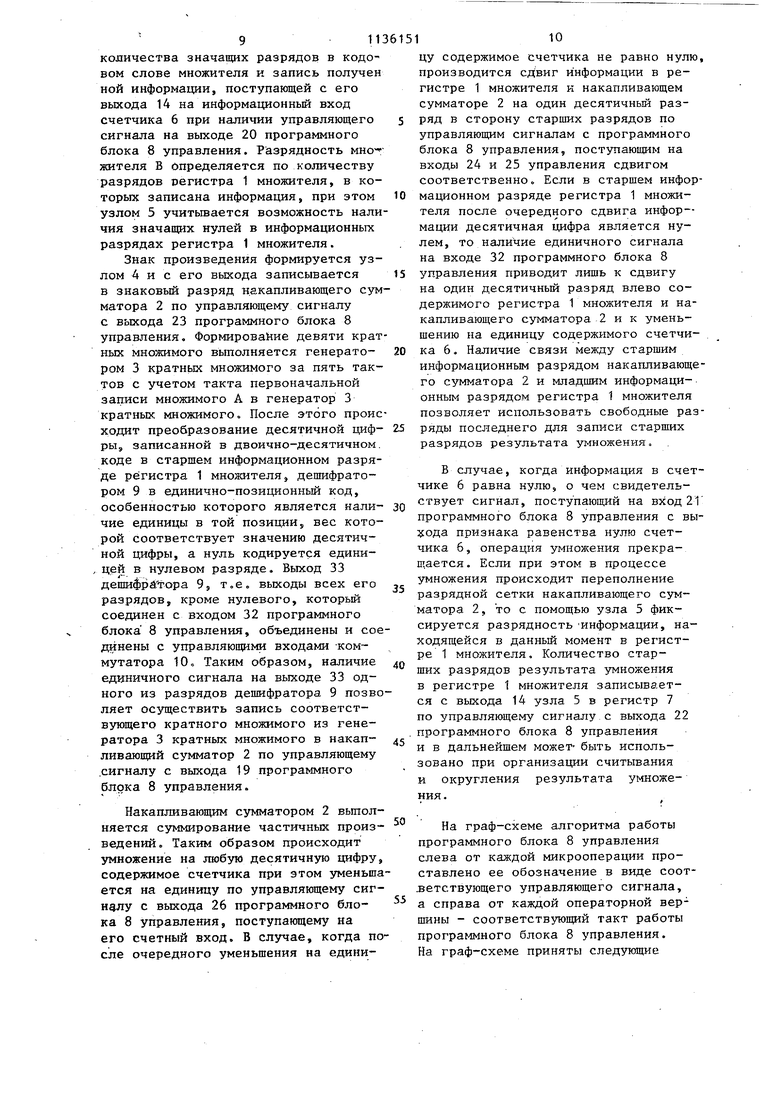

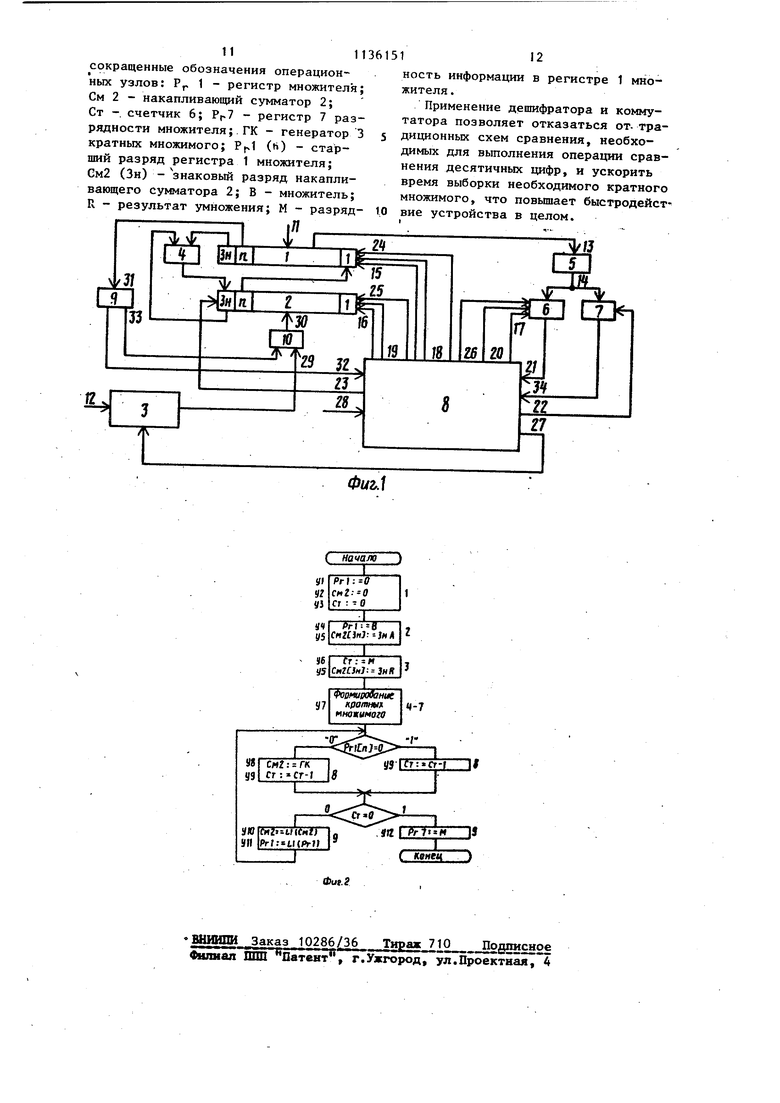

Изобретение относится к вычислительной технике и может быть исполь зовано в арифметических устройствах выполняющих операции над десятичными числами. Известно последовательное десяти ное устройство умножения, содержащее девять регистров хранения кратных множимого, сумматор, регистр управления-сложением, регистр множи теля, Регистр результата, селекторкомпаратор, регистр переноса и девять схем равнозначности, первые входы которых соединены с выходами соответствующих регистров хранения кратных множимого, вторые входы с выходом селектора-компаратора, а выходы схем равнозначности через регистр управления сложением соединены с первым входом параллельного двоично-десятичного сумматора, второй вход которого связан с выходом регистра результата, третий вход с выходом регистра переноса, вьрсод переноса - с входом регистра перено са, а выход - с входом регистра.результата, выход регистра множителя соединен с входом селектора-компара тора Ci 3. Недостатком этого десятичного устройства умножения является невысокое быстродействие вследствие тог что в цикле формирования кратных множимого процесс их формирования осуществляется последовательно для каждого кратного множимого путем суммирования с использованием одног сз мматора и регистра результата . с последукщей перезаписью результат в соответствующие регистры хранения кратных множимого. Наиболее близким к изобретению по технической сущности является арифметическое устройство, предназначенное, в частности, для умножения, содержащее регистры первого и второго операндов, сумматор, блок программного управления, входы которого с первого и по четвертый соединены соответственно с входами признаков операций сложения, вычитания, умножения и деления устройства, выход сумматора соединен с информационным входом регистра второго операнда, группу из К сумматоров-вычитателей .(К+1) - основание системы счисления), группу из К схем сравнения, К регистров значения кратности, компаратор, схему сравнения знаков, схему сравнения старших информационных разрядов операндов, два коммутатора, два счетчика, регистры разрядности пер.вого и второго операндов, регистры |целой и дробной частей частного, причем выходы знаковых разрядов регистров первого и второго операндов подключены к входам схемы сравнения знаков, выход которой соединен с пятым входом блока программного управления, первьш выход которого соединен с входом управления операцией первого сумматора-вычитателя группы и с управляющим входом первого коммутатора, первьй и второй вькоды которого подключены соответственно к CJTMмирующему входу первого сумматоравычитателя группы и к вычитающим входам всех сумматоров-вычитателей rpjmпы, второй и третий выходы блока программного управления подключены к входам управле.ния чтением регист- ров первого и второго операндов, выход регистра второго операнда подключен к первому информационному входу первого коммутатора, вход обнуления регистра первого операнда подключен 31 к четвертому выходу блоКа программно го управления, шестой вход которого соединен с выходом знакового разряда первого сумматора-вычитателя группы, пятьй выход блока программного управления подключен к входу управления инверсией знакового разря да регистра первого операнда, шестой выход блока программного управления подключен к установочному входу знакового разряда регистра второго операнда, выход регистра разрядности первого операнда подключен к информационному входу первого счетчика, входы управления записью регистров разрядности первого и второго операндов подключены к седьмому и восьмому выходам блока программного управления, выходы регистров разрядности первого и второго oneрандов подключены соответственно к второму и третьему информацио ным входам первого коммутатора, вход управления записью регистра первого операнда соединен с девятым выходом блока программного управления, десятый и одиннадцатьш выходы которого подключены к входам управления чтением регистров разрядности первого и второго операндов соответственно, второй выход первого сумматоравычитателя группы подключен к седьмо му входу блока программного управления, двенадцатый выход которого соединен с входом обнуления первого сумматора-вычитателя группы, тринадцатый выход блока программного управ ления подключен к входу обнуления регистра второго.операнда, суммирующий вход каждого сумматора-вычитателя группы, начиная с второго, соединен с первым выходом предыдущего сум матора-вычитателя группы, выход каждого регистра значения кратности подключен к первому входу соответствующей схемы сравнения группы, вторы входы схем сравнения группы подключе ны к выходу старшего информационного разряда регистра первого операнда, выход каждой схемы сравнения группы подключен к входу управления чтением соответствующего сумматора-вычитателя группы, первые выходы сумматоров-вычитателей группы подключены к информационному входу сумматора, вход управления записью которого под ключен к четырнадцатому выходу блок программного управления, пятнадцаты 14 и шестнадцатьм выходы которого подключены к входам управления сдвигом регистра первого операнда и сумматора, входы первого и второго счетчиков соединены с семнадцатым и восемнадцатым выходами блока программного управления, выход старшего разряда сумматора подключен к информационному входу младшего информационного разряда регистра второго операнда, вход управления сдвигом которого соединен с девятнадцатым выходом блока программного управления, выход признака нуля первого счетчика с восьмым входом блока программного управления, двадцатый выход которого соединен с информационным входом знакового разряда регистра целой части частного, выходы старших информационных разрядов регистров первого и второго операндов подключены к входам схемы сравнения старших информационных разрядов операндов, выход которой подключен к девятому входу блока программного управления, двадцать первый выход которого соединен с информационным входом младшего разряда регистра целой части частного, вторые выходы сумматороввьгчитателей группы соединены с вхо-, дами компаратора, выход которого подключен к управляющему входу второго коммутатора, информационный вход которого соединен свыходами регистров значения кратности, а выход соединен с вторыми входами схем сравнения группы и с информационными входами младитх разрядов регистров целой и дробной частей частного, входы управления записью которых соединены с двадцать вторым и двадцать третьим выходами блока программного управления, двадцать четвертый и двадцать пятый выходы которого соединены с входами управления сдвигом регистров целой и дробной частей частного соответственно, выход регистра первого операнда соединен с информационным входом регистра второго операнда, двадцать шестой и двадцать седьмой выходы блока программного управления подключены ко входу управления записью регистра второго операнда и входом выдачи второго коммутатора соответственно, двадцать восьмой и двадцать девятый выходы блока программного управления соединены с входом обнуления и вхо51дом управления чтением сумматора соответственно, выход признака нуля второго счетчика соединен с десятым входом программного блока управления тридцатый и тридцать первый выходы которого подключены соответственно к входам обнуления и входам управлекия операций сумматоров-вьтитателей группы, начиная с второго, а первые выходы всех сумматоров-вычитателей группы соединены также с информацион ным эходом регистра первого операнда Г23. : К недостаткам известного устройства можно отнести необходимость использования группы из К схем срав нения (где (К+1) - основание систем счисления) для определения одного из кратных множимого, соответствующего цифре в старшем разряде множителя, а также последовательное формирование необходимых кратных в гру пе из К сумматоров-вычитателей. Цель изобретения - повышение быстродействия устройства для умножения. Поставленная цель достигается тем, что устройство для умножения, содержащее регистр множителя, накап ливающий сумматор, узел формирования знака, генератор кратных множимого, узел подсчета количества значащих разрядов в кодовом слове множ теля, счетчик, регистр разрядности множителя, программный блок управле ния, причем вход множителя устройс информационным вхоства Соединен дом регистра множителя, вход множимого устройства подключен к информа ционному входу генератора кратных множимого, выходы знаковых разрядов регистра множителя и накапливающего сумматора подключены соответственно к входам узла формирования знака, выход которого соединен с входом зн кового разряда накапливающего сумматора, выход информационных разрядов регистра множителя соединен с входом узла подсчета количества значащих разрядов в кодовом слове множителя, выход которого соединен с информационными входами регистра разрядности множителя и счетчика, выходы программного блока управлени с первого по третий подключены соот ветственно к входам обнуления регис ра множителя, накапливающего сумматора, счетчика, четвертый и пятый 1 выходы программного .блока управления подключены к входам управления записью регистра множителя и накапливающего сумматора, выход старшего информационного разряда Накапливающего сумматора подключен к информационному входу младшего информационного разряда регистра множителя, шестой и седьмой выходы программного блока управления подключены соответственно к входам управления записью счетчика и регистра разрядности множителя, выход признака равенства нулю счетчика подключен к первому входу программного блока управления, восьмой выход которого подключен к входу управления записью в знаковый разряд накапливающего сумматора, девятый и десятый выходы программного блока управления подключены соответственно к входу управления сдвигом регистра множителя и счетному входу счетчика, одиннадцатый выход программного блока управления подключен к входу управления сдвигом накапливающего сумматора, двенадцатый вькод программного блока управления подключен к управляющему входу генератора кратных множимого, второй вход программного блока управления соединен с входом запуска уст1ройства, содержит дешифратор и коммутатор , информационный вход которого подключен.к выходу генератора кратных множимого, а выход соединен с информ ционным входом накапливающего сумматора J, выход старшего информаци- . оняого разряда регистра множителя соединен с входом дешифратора, нулевой выход которого подключен к третьему входу программного блока управления, а остальные выходы - к управляющим входам коммутатора, выход регистра разрядности множителя соединен с четвертым входом программного блока управления. На фиг. 1 представлена блок-схема устройства для умножения; на фиг. 2 граф-схема алгоритма работы программного блока управления. Устройство для умножения содержит регистр 1 множителя, накапливающий сумматор 2, генератор 3.кратных мно-г жимого, узел 4 формирования знака, узел 5 подсчета количества значащих разрядов в кодовом.слове множителя, счетчик 6, регистр 7 разрядности множителя , программный блок 8 управления, дешифратор 9 и коммутатор 10. Вход 11 множителя устройства соединен с информационным входом регистра 1 множителя, вход 12 множимого устройства подключен к информационному входу генератора 3 кратных множимого, выходы знаковых разрядов регистра 1 множителя и накапливающего сумматора 2 подключены соответственно к входам узла 4 формирования знака, выход которого соединен с входом знаковог разряда накапливающего сумматора 2. Выходы информационных разрядов реги стра 1 множителя соединены с входом 13 узла 5 подсчета количества значащих разрядов в кодовом слове множителя, выход 14 которого соединен с информационными входами счетч ка 6 и регистра 7 разрядности множи теля соответственно. Входы 15-17 обнуления регистра 1 множителя, накапливающего сумматора 2 и счетчика 6 подключены к соответствующим выходам программного блока 8 управления , выходы 18 и 19 которого подключены к входам управления записью соответственно регистра1 мно жителя и накапливающего сумматора 2 выход старшего информационного разряда которого соединен с информационным входом младшего информационного разряда регистра 1 множителя Выход 20 программного блока В управ ления подключен к, входу управления записью счетчика 6, выход признака равенства нулю которого соединен с входом 21 программного блока 8 управления, выход 22 .которого подкл чен к входу управления записью реги стра 7 разрядности множителя, а выход 23 - к входу управления записью в знаковый разряд накапливающего су матора 2. Входы 24 и 25 управления сдвигом регистра 1 множителя и накапливающего :умматора 2 подключены к соответствующим выходам программн го блока 8 управления, выход 26 кот рого соединен со счетным входом счетчика 6, выход 27 - с управляющи входом генератора.3 кратных множимо го, а вход 28 - с входом запуска устройства. Информационный вход 29 - коммутатора 10 подключен к выходу генератора 3 кратньк множимого, а выход 30 соединен с информационным входом накапливающего сумматора 2, выход старшего информационного разряда регистра 1 множителя соединен

с входом 31 дешифратора 9, нулевой выход которого подключен к входу 32 программного блока 8 управления, а остальные выходы 33 - к управляющим входам коммутатора 10. Выход регистра 7 подключен ко входу 34 программного блока 8 управления.

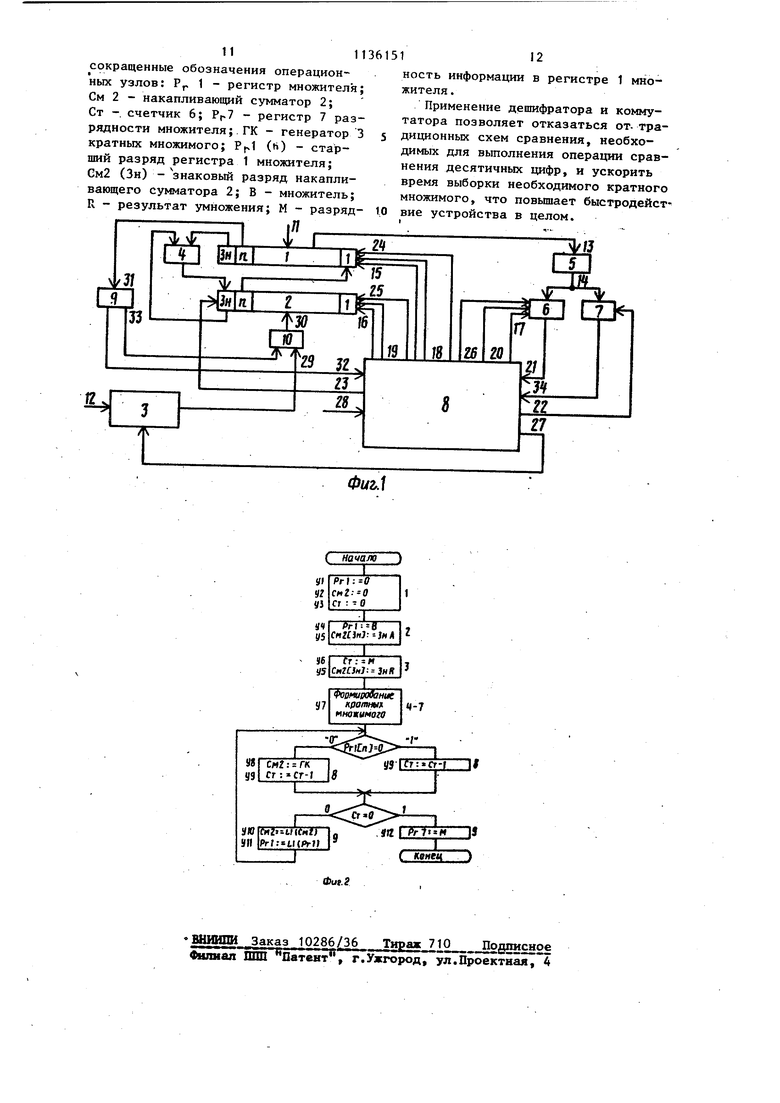

Устройство для умножения реализует следующий алгоритм умножения десятичных чисел, 1.Множитель записывается в регистр множителя, множимое - в генератор кратных множимого, где формируются кратные множимого. Определяется с помощью узла формирования знака знак результата, которьй положителен при совпадении знаков сомножителей и отрицателен при их несовпадении. 2.Производится одновременное сравнение цифры старшего разряда множителя и номера каждого кратного множимого. 3.При совпадении цифры старшего разряда множителя и номера одного |ИЗ кратных множимого осуществляется суммирование соответствующего кратного мно;кимого с содержимым накапливающего сумматора и последующий сдвиг на один десятичный разряд в сторону старших разрядов содержимого накапливающего сумматора и регистра множителя. При несовпадении цифры старшего разряда множителя с номером одного из кратных множимого, а это возможно в случае, когда цифра множителя является нулем, происходит лишь сдвиг на один десятичный разряд в сторону старших разрядов содержимого накапливающего сумматора и регистра множителя. 4.Для каждого десятичного разряда множителя повторяются действия пп. 2 и 3 до тех пор, пока не будет произведено умножение на все разряды множителя. Устройство для умножения работает следующим образом. Множимое А и множитель В записываются в генератор 3 кратных множийого и регистр 1 множителя по входам 12 и 11 соответственно. Знак множимого А записывается в знаковый разряд накапливающего сумматора 2 по управляющему сигналу с выхода 23 программного блока 8 управления. После окончания записи сомножителей производится определение разрядносги М множителя В узлом 5 подсчета 911 количества значащих разрядов в кодовом слове множителя и запись получен ной информации, поступающей с его выхода 14 на информационньй вход счетчика 6 при наличии управляющего сигнала на выходе 20 программного блока 8 управления. Разрядность мно- жителя В определяется по количеству разрядов регистра 1 множителя, в которых записана информация, при этом узлом 5 учитьтается возможность нали чия значапщх нулей в информационных разрядах регистра 1 множителя. Знак произведения формируется узлом 4 и с его выхода записывается в знаковый разряд накапливающего сум матора 2 по управляющему сигналу с выхода 23 программного блока 8 управления. Формирование девяти крат ных множимого выполняется генератором 3 кратных множимого за пять тактов с учетом такта первоначальной записи множимого А в генератор 3 кратных множимого. После этого проис ходит преобразование десятичной цифры, записанной в двоично-десятичном, коде в старшем информационном разряде регистра 1 множителя, дешифратором 9 в единично-позиционный код, особенностью которого является наличие единицы в той позиции„ вес которой соответствует значению десятичной цифры, а нуль кодируется едини, цей в нулевом разряде. Выход 33 деши$рйтора 9, т.е. выходы всех его разрядов, кроме нулевого, который соединен с входом 32 программного блока 8 управления, объединены и сое динены с управляющими входами -коммутатора 10, Таким образом, наличие единичного сигнала на выходе 33 одного из разрядов депшфратора 9 позво ляет осуществить запись соответствующего кратного множимого из генератора 3 кратных множимого в накапливающий сумматор 2 по управляющему сигналу с выхода 19 программного блока 8 управления. Накапливающим сумматором 2 выполняется суммирование частичных произведений. Таким образом происходит умножение на любую десятичную цифру, содержимое счетчика при этом уменьша ется на единицу по управляющему сигналу с выхода 26 программного блока 8 управления, поступающему на его счетный вход. В случае, когда по сле очередного уменьшения на единиI10цу содержимое счетчика не равно нулю, производится сдвиг информации в регистре 1 множителя и накапливающем сумматоре 2 на один десятичный разряд в сторону старших разрядов по управляющим сигналам с программного блока 8 управления, поступающим на входы 24 и 25 управления сдвигом соответственно. Если в старшем информационном разряде регистра 1 множителя после очередного сдвига инфор-мации десятичная цифра является нулем, то наличие единичного сигнала на входе 32 программного блока 8 управления приводит лишь к сдвигу на один десятичный разряд влево содержимого регистра 1 множителя и накапливающего сумматора 2 и к уменьшению на единицу содержимого счетчика 6. Наличие связи между старшим информационным разрядом накапливающего сумматора 2 и г«шадшим информационным разрядом регистра 1 множителя позволяет использовать свободные разряды последнего для записи старших разрядов результата умножения. Б случае, когда информация в счетчике 6 равна нулю, о чем свидетельствует сигнал, поступающий на вход 2Г программного блока 8 управления с вы2{ода признака равенства нулю счетчика 6, операция умножения прекращается. Если при этом в процессе умножения происходит переполнение разрядной сетки накапливающего сумматора 2, то с помощью узла 5 фиксируется разрядность Информации, находящейся в данный момент в регистре 1 множителя. Количество старших разрядов результата умножения в регистре 1 множителя записывается с выхода 14 узла 5 в регистр 7 по управляющему сигналу с выхода 22 программного блока 8 управления и в дальнейшем может- быть использовано при организации считывания и округления результата умножения. На граф-схеме алгоритма работы программного блока 8 управления слева от каждой микрооперации проставлено ее обозначение в виде соот.ветствующего управляющего сигнала, а справа от каждой операторной вершины - соответствующий такт работы программного блока 8 управления. На граф-схеме приняты следующие сокращенные обозначения операционных узлов: Рр 1 - регистр множителя; См 2 - накапливающий сумматор 2; Ст - счетчик 6; - регистр 7 разрядности множителя; ГК - генератор 3 кратных множимого; Pfsl (н) - старший разряд регистра 1 множителя; См2 (Зн) - знаковый разряд накапливающего сумматора 2; В - множитель; R - результат умножения; М - разрядГ начало ность информации в регистре 1 множителя . Применение дешифратора и коммутатора позволяет отказаться от-традиционных схем сравнения, необходимых для вьтолнения операции сравнения десятичных цифр, и ускорить время выборки необходимого кратного множимого, что повышает быстродействие устройства в целом.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Чу Я | |||

| Организация ЭВМ | |||

| и микропрограммирование | |||

| М., Мир, 1975, с | |||

| Тепловой измеритель силы тока | 1921 |

|

SU267A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Авторское свидетельство СССР .по заявке № 2911429/18-24, кл | |||

| G | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-01-23—Публикация

1982-04-27—Подача