первого элемента запрета, прямой вход которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен с выходом третьего элемента ИЛИ и первым-информационньзм входом суммирующего блока, второй информационный вход которого соединен с вторым входом второго элемента ИЛИ и выходом четвертого элемента ИЛИ, выход первого элемента aanpeTia соединен с третьим информационным входом суммируквдего блока и с входом выдачи обратного кода сдвигающего регистра, прямые выходы которого соединены соответственно с информационными входами первых и вторых регистров множимого и множителя, прямые и обратные вькоды регистра сдвига соединены соответственно с пятой группой информационных входов суммирующего блока., шестая группа инфоЕмадионнык й сдо« с 1 мирую1Дего блока соединена с икфср-;ационными .выходами второго регистра множимого, седьмая группа информационных входов суммир- тощего блока соединена с информационными выходами второго регистра множителя, входы регистра суммы соединены соответственно с выходами суммы суммирующего блока, выход старшего разряда суммы суммиругацего блока соединен с прямым входом второго элемента запрета и инверсным входом третьего элемента запрета, прямой вход которого соединен с вькодом пятого элемента ИЛИ первый и второй входы которого соединены соответственно с рторым и третьим старшими разрядами сунг/1Ы суммирующего блока и первым и BTOpbHvi входами третьего элемента и, которого соединен с инверстным ззходом второго элемента запрета, выходы второго и третьего элементов запрета соединены соответственно с выходами устройства, вход сдвига с.цвигающего рбгистра соединен с тактовым входом устройства.

2. Устройство ПОП.1, отличаю щ ее с я тем, что,суммирующий блок содержит первый, второй, третий четвертый и пятый сумматоры, причем первая, вторая и шестая- группы информацион 1ых входов суммирующего блока подключены соответственно к входам первого .сумматора, выходы суммы и переносов которого, соединены соответственно с первой, и второй группами . входов второго сумматора, третья группа информационных входов которого соединена с выходами суммы третьего сумматора, первая, вторая и третья информационные группы входов которого соединены соответственно с третьей, пятой и седьмой гр шпами информационных входов су1 Мирующего блока, первый информационный вход которого соединен с пёрвьии.входами пяти старших разрядов третьего сумматора и первым входом младшево разряда четвертого сумматора, третий информационный вход суммирующего блока соединен соответственно с вторыми входами пяти старших разрядов третьего суюла-тора и вторьм входом младшего разряда четвертого сумматора, второй информационный вход суммиругацего блока соединен соответ-, ственно с первы.да входами пяти старших разрядов второго сутлматора и первьм входом младшего разряда второго сумматора первая , вторая и третья группы .входов четвертого сумматора соединены соответственно с выходами суммы и переносов второго сумматора и выхода ми переносов третьего суг.-матора, выходы суммы и переносов четвертого суг/матора соединены соответственно с первой и второй группами инфорШ ционных входов пятого сумматора, третья Группа входов которого соединена с четвертой группой информационных входов суммируквдего блока, выходы суммы к переносов пятого сумматора соединены соответственно с выходами суммы к переносов суммирукщего блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1986 |

|

SU1427361A1 |

| Устройство для умножения | 1981 |

|

SU1007101A1 |

| Устройство для умножения чисел в @ -кодах Фибоначчи | 1980 |

|

SU1137459A1 |

| Устройство для умножения | 1981 |

|

SU1018115A1 |

| Последовательное множительное устройство | 1981 |

|

SU987620A1 |

| Арифметическое устройство | 1984 |

|

SU1236473A1 |

| Устройство для умножения | 1976 |

|

SU603989A1 |

| Вычислительное устройство | 1980 |

|

SU957203A1 |

| Устройство для умножения | 1976 |

|

SU651341A1 |

| Параллельный сумматор | 1981 |

|

SU1018114A1 |

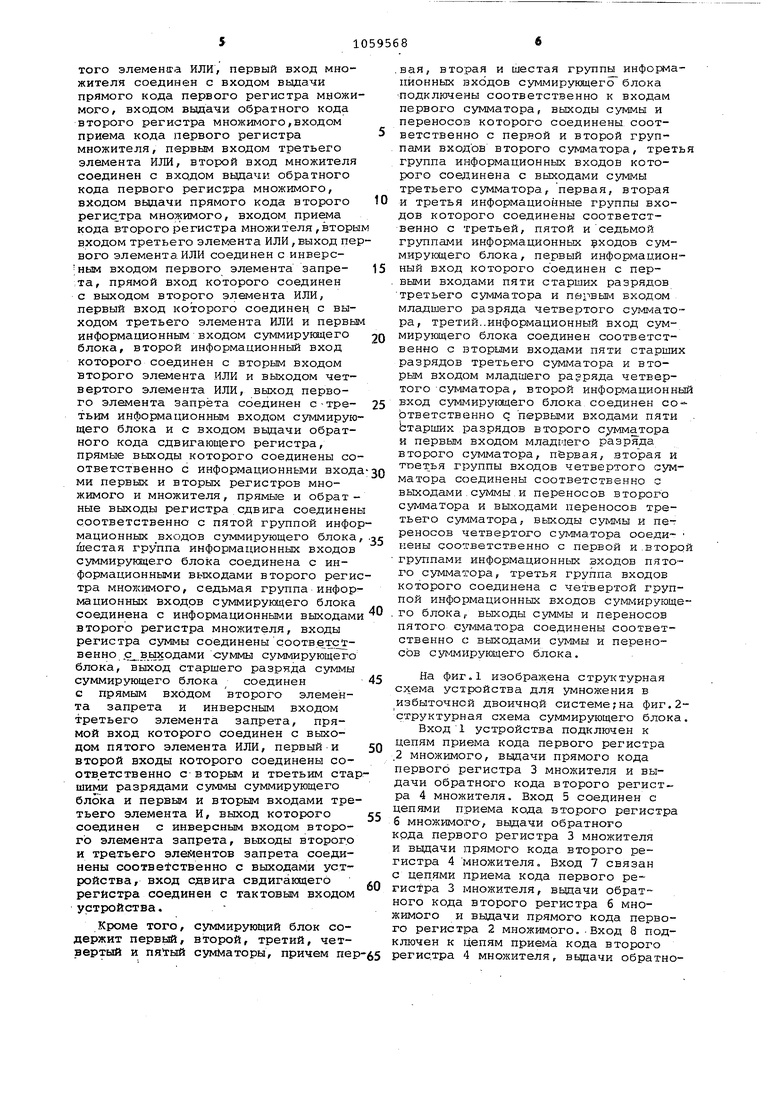

1. УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ В ИЗБЫТОЧНОИ ДВОИЧНОЙ СИСТЕМЕ, содержащее сдвигающий регистр, первый, второй и третий элементы И, первый, второй, третий, четвертый и пятый элементы ИЛИ, суммирующий блок, а также регистр множимого, регистр множителя и регистр суммы,.информационные выходы которых подключены соответствен но к первой, второй и третьей группам информационных входов суммирующего блока, первая группа информационных выходов которого соединена соответственно с инфо1жационныМи входами регистра суммы, тактовый вход которого соединен с тактовым1-шходом устройства и входом сдвига сдвигающего регистра, вход выдачи прямого кода которого соединен с выходом первого элемента ИЛИ, первый и второй входы которого подключены соответственно к выходам первого и второго элементов И, первые входы которых соединены соответственно с первьми .входами множителя и множимого, отличающееся тем, что, с целью повышения быстродействия, в него введены второй регистр множителя, второй регистр множимого, первый, второй и третий элементы запрета, второй, третий-, четвертый и пятый элементы ИЛИ и регистр переносов, информационные выходы которого подг: ключены соответственно к четвертой группе информационных входов суммлрукщего блока, выходы переносов которого соединены соответственно с информационными входами регистра переносов, вход сдвига которого соединен с управляквдим входом приема такто- регистра суммы и кода вым входсМ устройства,, первый вход множимого которого соединен с входом (О приема кода .первого регистра множимого , входом выдачи прямого кода первого регистра множителя, входом выдачи обратного кода в торого ре гистра множителя, с первым входом четвертого элемента ИЛИ, второй вход множимого устройства соединен с входом приема кода второго регистра СП множимого, входом выдачи обратного кода первого регистра множителя, вхоСО СП дом выдачи прямого кода второго регистра множителя, вторым входом четвертого элемента ИЛИ, -первый О) вход множителя соединен с входом 00 выдачи прямого кода первого регистра множимого, входом выдачи обратного кода второго регистра множимого, входом рриема кода первого регистра множителя, первым входом третьего элемента ИЛИ, второй вход множителя соединен с входом выдачи обратного кода первого регистра множимого, входом выдачи прямого кода второго регистра множимого, вхо. дом приема кода второго регистра,множителя, вторым входом третьего элемента ИЛИ, первого элемента ИЛИ соединен с инверснал входом

Изобретение.относится к вычислительной технике и может быть ррименено в цифровых вычислительных машинах и приборах для умножения чисел с фиксированной запятой.

Известны устройства для умножения, .предназначенные .для умножения чисел с фиксированной запятой. В их состав входят регистры, сумматоры и схема

управления. В некоторых случаях для ускорения вычислений применяются матричные схемы деревья сумматоров 11 1 и 2 .

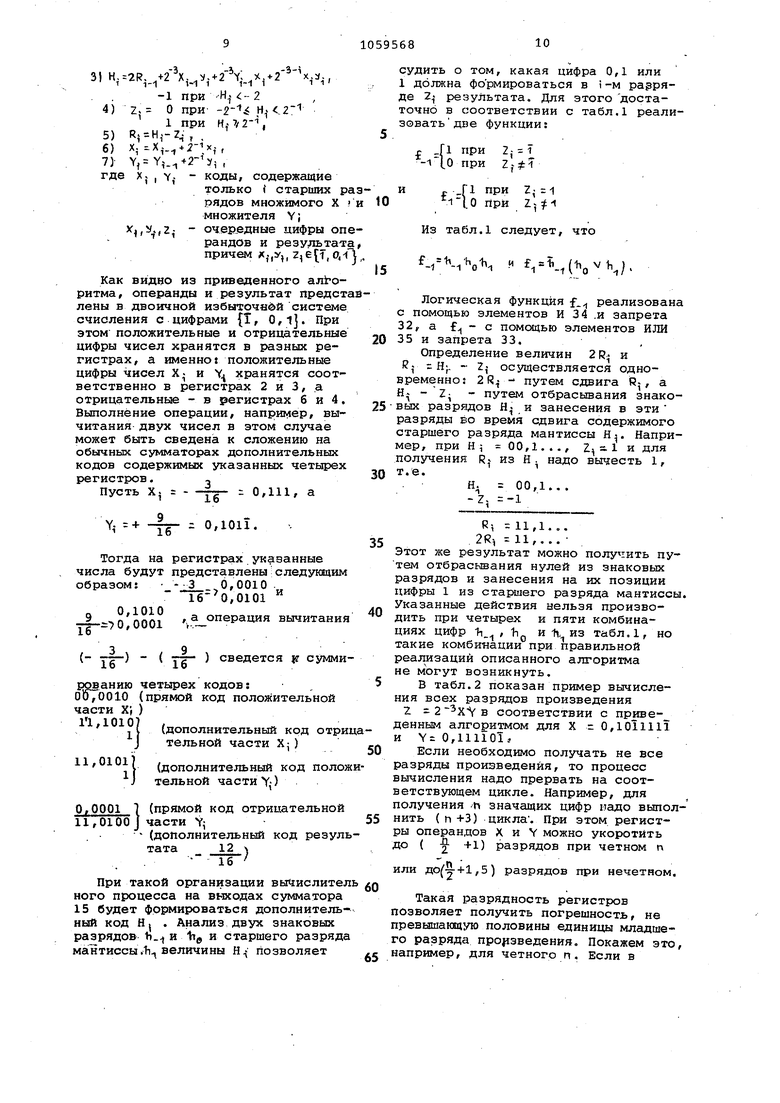

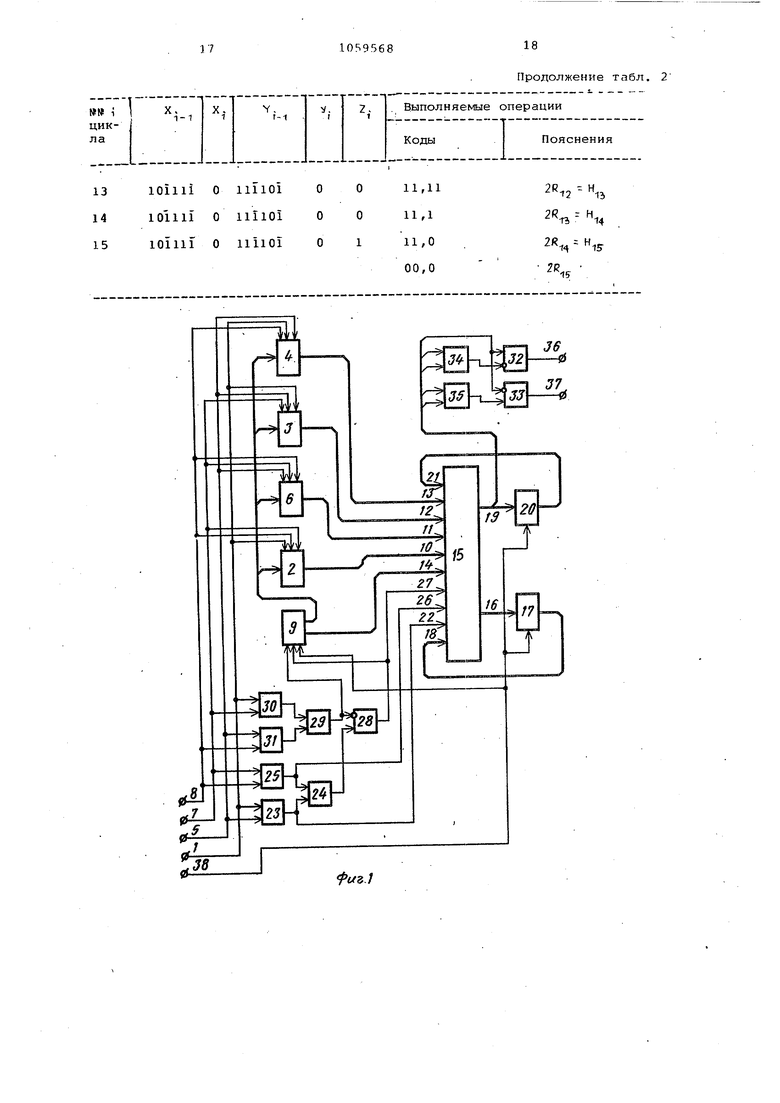

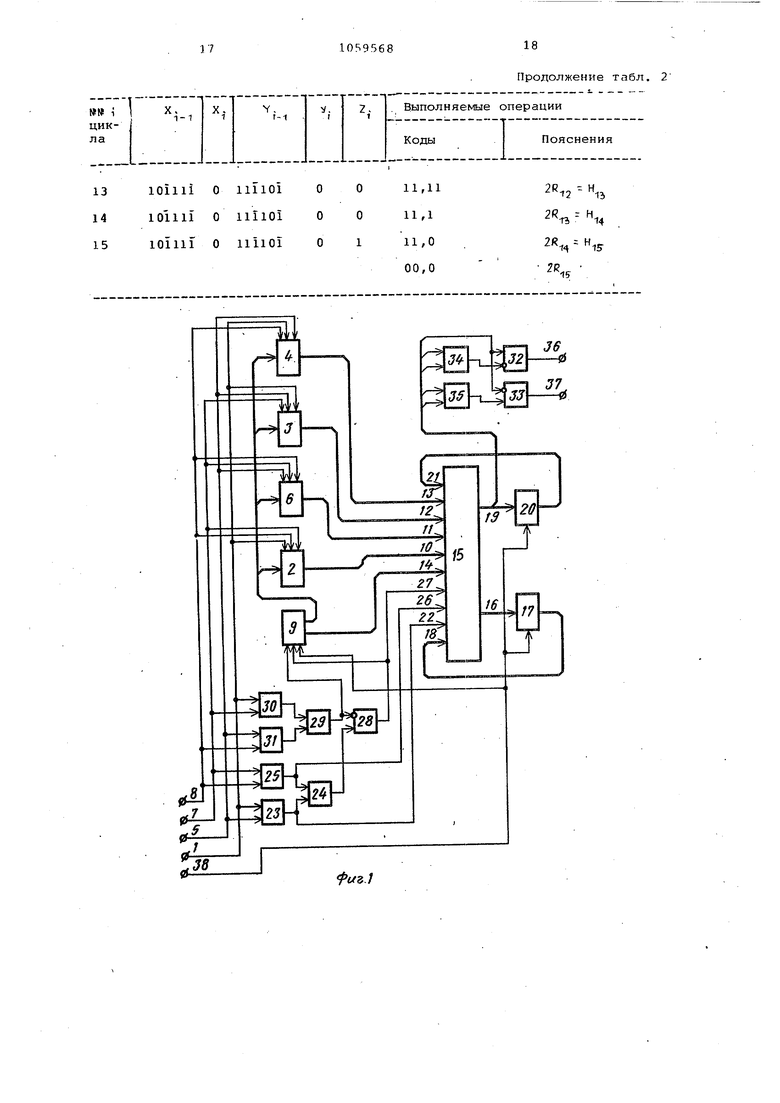

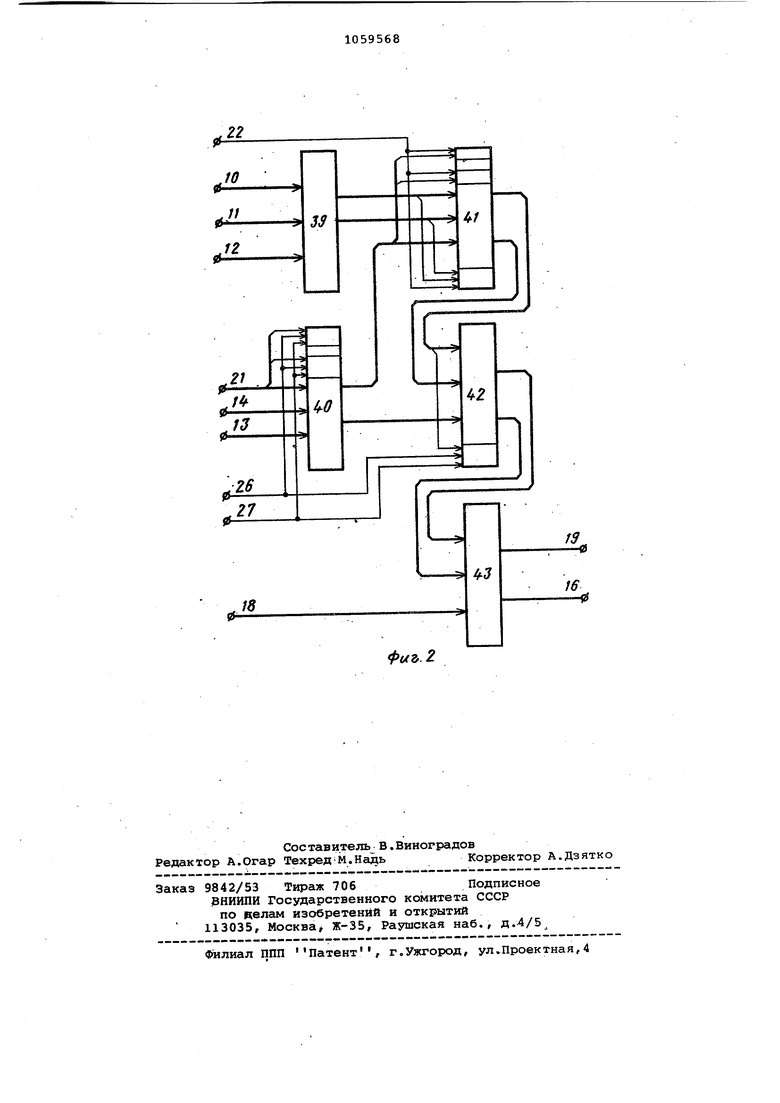

5 Однако указанные устройства обладают низким быстродействием в тех случаях, когда информация посХУ пает на юс входы последовательниц кодом начиная со старших разрядов. Это не позволяет эффективно использовать устройства в системах управления процессами в реальном масштабе времени, когда информация поступает на вход устройства, например, с преобразователей аналог,-код или цифровых измерительных приборов поразрядного уравновешивания.В этом случае в устройствах необходимо вре мя для накопления всех цифр операндов и общее время вычисления резуль тата составляет -tr-t t , где t - время накопления операндо tg - время вычислений в устройства. Да протяжении времени t нельзя фор мировать управлякщее воздействие для исполнительного органа системы управления, так как информация о его величине отсутствует. Известно также множительное устройство, которое позволяет совмещат процессы поразрядного ввода операндов (начиная со старших разрядов) с их обработкой. В егр состав входят последовательно соединенные блоки суммирования, подключенные к их входам блоки умножения, блоки кодирования, блок декодирования и элеме задержки СЗ Однако данное устройство обладае малым быстродейссгв лем. Наиболее близким техническим решением к предлагаемому является уст ройство, содержащее регистры множимого, множителя, суммы и сдвига, сумматор результата (суммирующий блок), элементы И и элементы ИЛИ, причем выходы регистров множимого, множителя и суммы подключены к вход сумматора результата, выходы которого подключены к входам регистра суммы. Входы первого и второго элементов И соединены с входами устройства, а выходы - с входами первого элемента ИЛИ, выход которого подключен к цепи прямого кода регис сдвига. Второй элемент ИЛИ соединен с одним из входов сумматора результ та. Управляющий вход устройства свя зан с управляющим входом регистра суммы и с цепью сдвига регистра сдвига. Кроме того, устройство соде жйт блок- анализа разрядов, KOTOptffi может быть построен на основе двух элементов запрета, третьего элемента И и тратье -о элемента ИЛИ, Выход Третьего элемента И связан с инверс ным входом первого элемента запрета а выход третьего элемента ИЛИ связа с прямым входом эло 1ента запрета. Выходы первого и второго элемента запрета подключены к выходам устрой ства С4 . Недостатком известного устройства является невысокое быстродействи вследствие большого времени вычислений в каждом цикле. Время цикла в устройстве составляет t -fc - + , где i- ( j : 1,2,3)время выполнения j-ro такта. Здесь t и tj равны времени суммирования в (п+2)-разрядном сумматоре или t, . Бремя, необходимое для выполнения третьего такта, равно времени сдвига на один разряд, tj -t сдБ Тогда в общем случае время, необходимое для выполнения цикла вычислений в устройстве составляет t сдв Цель изобретения - повышение быстродействия устройства. Поставленная цель достигается тем. что в устройство для умножения в избыточной двоичной системе,содержащее сдвигающий регистр,первый,второй и третий элементы И,первый второй, третий, четвертый и пятый элементы ИЛИ, сумг.ирующий блок, а также регистр множимого, регистр множителя и регистр суммы, информационные выходы которых подключены соответственно к первой,второй и третьей группам информационных входов суммирующего блока, первая группа информационных выходов которого соединена соответственн9 с информационными входами регистра суммы, тактовый вход которого соединен с тактовым входом устройства и входом сдвига сдвигакадего регистра, вход выдачи прямого кода которого соединен с выходом первого элемента ИЛИ, первый и второй входы которого подключены соот етственно к выходам первого и второго элементов И, первые входы которых соединены соответственно с первыми входами множителя и множимого, введены второй регистр множителя, второй регистр множимого, первый, второй и третий элементы запрета, второй, третий, чегвертый и пятый элементы ИЛИ и регистр переносов, информационные выходы которого подключены соответственно к четвертой группе информационных входов суммирующего блока, выходы переносов которого соединены соответственно с информационными входами регистра переносов, вход сдвига которого соединен с управляющим входом приема кода регистра суммы и с тактовым входом устройства, первый вход множимого которого соединен с входом приема кода первого регистра множимого, входом выдачи прямого кода первого регистра множителя,входом выдачи обратного кода второго регистра множителя, с первым входом четвертого элемента ИЛИ, второй вход множимого устройства соединен с входом приема кода второго регистра множимого , входом выдачи обратного кода первого регистра множителя, входом вьэдачи прямого кода второго регистра множителя, вторьм входом чвтвертого элемента ИЛИ, первый вход множителя соединен с входом выдачи прямого кода первого регистра множи мого, входом выдачи обратного кода второго регистра множимого,входом приема кода первого регистра множителя, первым входом третьего элемента ИЛИ, второй вход множителя соединен с вхрдом выдачи обратного кода первого регистра множимого, входом вьщачи прямого кода второго регис тра множимого, входом приема кода второго регистра множителя,вторы входом третьего элемента ИЛИ, выход пе вого элемента ИЛИ соединен с инверс ным входом первого элемента запре.та, прямой вход которого соединен с выходом второго элемента ИЛИ, первый вход которого соединен, с выходом третьего элемента ИЛИ и первы информационным входом суммиругадего блока, второй информационный вход которого соединен с вторым входом второго элемента ИЛИ и выходом четвертого элемента ИЛИ, выход первого элемента запрета соединен с-третьим информационным входом суммирую щего блока и с входом вьщачи обратного кода сдвигающего регистра, прямые выходы которого соединены со ответственно с информационными вход ми первых и вторых регистров множимого и множителя, прямые и обратные выходы регистра сдвига соединен соответственно с пятой группой инфо мационных входов суммирующего блока йестая группа информационных входов суммирующего блока соединена с информационными выходами второго реги тра множимого, седьмая группа инфор мационных входов суммирукхдего блока соединена с информационными выходам второго регистра множителя, входы регистра суммы соединены соответственно с в ыходами суммы суммирующего блока, выход старшего разряда суммы суммирующего блока соединен с прямым входом второго элемента запрета и инверсным входом третьего элемента запрета, прямой вход которого соединен с выхоцом пятого элемента ИЛИ, первый и второй входы которого соединены соответственно с-вторым и третьим ста шими разрядами суммы суммирующего блока и первым и вторым входами тре тьего элемента И, выход которого соединен с инверсным входом второго элемента запрета, выходы второго и третьего элементов запрета соединены соответственно с выходами устройства, вход сдвига свдигающего регистра соединен с тактовым входом устройства. Кроме того, суммирующий блок содержит первый, второй, третий, четвертый и пяТый сумматоры, причем пе вая, вторая и шестая группы инфориационных входов суммируняцего блока -подключены соответственно к входам первого сумматора, выходы суммы и переносов которого соединены соответственно с первой и второй группами входов второго сумматора, третья группа информационных входов которого соединена с выходами суммы третьего сумматора, первая, вторая и третья информационные группы входов которого соединены соответственно с третьей, пятой и седьмой группами информационных -кодов суммирукщего блока, первый информационный вход которого соединен с первыми входами пяти старших разрядов третьего сумматора и первым входом младшего разряда четвертого сумматора, третий..информационный вход суммирующего блока соединен соответственно с вторыми входами пяти старших разрядов третьего сумматора и вторым входом младшего разряда четвертого сумматора, второй информационный вход сутда/тирувицего блока соединен соОтветственно с первыми входами пяти . Ьтарших разрядов второго сумма тора и первым входом младшего разряда второго сумматора, первая, вторая и тпетья группы входов четвертого сумматора соединены соответственно с выходами.суммы,и переносов второго cjMMaTopa и выходами переносов третьего сумматора, выходы суммы и переносов четвертого сумматора ооеди- кены соответственно с первой и .второй группами информационных входов пятого сумматора, третья группа входов которого соединена с четвертой группой информационных входов суммирующего блока,, выходы суммы и переносов пятого ciMMaTopa соединены соответственно с выходами суммы и переносов суг-мирующего блока. На фиг.1 изображена структурная устройства для умножения в избыточной двоичной системе;на фиг.2структурная схема суммирующего блока. Вход1 устройства подключен к цепям приема кода первого регистра 2 множимого, ВБдачи прямого кода первого регистра 3 множителя и выдачи обратного кода второго регистра 4 множителя. Вход 5 соединен с цепями приема кода второго регистра б множимого, вьщачи обратного рда первого регистра 3 множителя выдачи прямого кода второго реистра 4 множителя. Вход 7 связан цепями приема кода первого реистра 3 множителя, вьщачи обратного кода второго регистра 6 мноимого и вьщачи прямого кода первоо регистра 2 множимого..Вход 8 подлючен к цепям приема кода второго егис.тра 4 множителя, вьщачи обратного, кода первого регистра 2 множимого и выдачи прямого кода второго регист ра б множимого. Первая группавыходов сдвигающего регистра 9 подключена к входам регистров 2, 6, 3 и 4 выходы которых, а также вторая группа выходов сдвигающего регистра 9 связаны с входами 10-14 суммирукадего блока 15. Выходы 16 суммирующего блока 15 подключены к- входам регистра 17 переносов, выходы которого подключены к входам 18 суммирукадего блока 15, выходы 19 которого соедине ны с входами регистра 20 :сумы. При этом к входам двух старших разрядов регистра 20 подключены выход 3-го разряда, и далее к входу каддого i-r разряда регистра 20 подключен выход (4,+1)-го разряда суммирукщего блока 15. Выходы регистра 20 соединены с входами 21 суммирующего блока 15, вход 22 которого соединен с выходок элемента ИЛИ входом элемента , второй вход которого связан с вьаходом элемента ИЛИ- 25 и с входо 26 суммирующего блока 15 вход 27 ко торого подключен к выходу эле1-1ента запрета 28 -и к цепи вьщачи обратного кода сдвигающего регистра 9. Прямой вход элемента запрета 28 связан с выходом элемента ИЛИ 24, а инверсны с цепью ВЕщачи прямого кода сдвигаю |щего регистра 9 и с выходом элекаент ИЛИ 29, входы которого подключены к рыходам Элементов И 30 и 31. Вход 1 устройства подключен к входа элемй&та И 30 и.элемента ИЛИ 23, Вход 5.связан с входами элементо« И 31 и ИЛИ 23 7 соединен с входа элементов И 30 и ИЛИ 25, Вход 8 соединен с входами элементов И 31 и ИЛИ 25. Первый (старший) разряд груп пы выходов 19 суммирукадего блока 15 подключен-.к прямому входу элемента запрета 32 и к инверсному входу элемента запрета 33. Второй и третий выходы группы 19 связаны с входаг4И элементов И 34 и ИЛИ 35, Выход элемента И 34 подключен к инверсному входу элемента запрета 32, выход которого соединен с выходом 36 устройства. Выход элемента ИЛИ 35 связан с прямьм входом элемента запрета 33, выход которого подключен к выходу 37 устройства. Управляющий вход 38 связан с цепью сдвига сдвигающего регистра 9 и с цепями приёма кода регистра 17 переносов и регистра ЙО суммы. Регистры 2, 3, 4 и 6-/ содержат ( --5- +1) разрядов, где .п - разрядность операндо.в, регистр 20 суммы содержит ( у +5) разрядов, а регистр 17 переносов содержит (- -1) разрядов.. . Суммирующий блок 15 (фиг.2) содержит сумматоры 39-43. Сумматоры 39-42 построены по схеме сумматоров без распространения переноса. Каждый разряд этих сумматоров представляет собой двоичный сумматор, имеющий три входа и два выхода - суммы и переноса. Су № аторы jy-42 имеют, таким образом, две группы выходов - выходы суьшы и выходы переносов/ С гмь1атор 43 построен аналогично за исключением того, что в пяти его старших разрядах происходит .распространение переноса. Сумматор 39 содержит ( +1) разрядов, сумматоры 40-43 содарж&т (-J +6) разрядов, К входам су-рматора 39 подключены группы входов 10-12 К первой группе сугсштсра 40 подключены входы 21 и к дpyги J группам (гу-+1) .младших разрядов сумматора 40 подключены группы входов 13 и 14. Вторые и третьи вхо-ды пяти старших разрядов сумматора 40..подключены соответственно к .г4 26 и 27, Выходы суммы и переноса сумматора 39 и выходы суммы cyi iMaтора 40 подключены к входам cyMKiaTopa 42, Кроме того, к входам пяти старших разрядов и к одному входу младшего разряда сумматора 41 подключен вход 22, На фиг.2 это подключение показано для выделенных младшего и двух старших разрядов сумматора 41 Выходы н переноса суг.1матора 41 и выходы пере«оса .матора 40 подключены к входам cyvt aтора 42f к первому ивторому ьход. двух младшйх разрядов которого подкллчены входы 26 и 27,, Входы 18 г, выходы суммы и переноса сумматора 42 подключены к входам сумматора 43. Выходы cyMTviH н переноса сумь атора 43 связаны соответственно с выхода .: 19 и 16, Рег-кстрса 2, 3, 4, 6, 17 и 20 построены на основе триггеров с внутренней задержкой, например, по MS ссхеме, в которой каждый разряд содержит два триггера основной и вспомогательный. При этом в состав регистров 2, 3, 4 и 6 входят Rs -триггеры, 5-входы которых подключены квыходам сдвигакэдего регистра 9, а R-входы к цепи сброса (не показана)е Регистры 20 к 17 суммы и переносов могут быть построены- на основэ С-тоиггеров. Устройство предназначено для выисления произведения работает в соответствик оо следуюим алго.ритмом S 1) У„., 2)для ,(п+3)выполнить пп.З- 31 Н.2Р..+2Л...2-%/,..:/.. -1 При - 2 2. О при ,HI- 1 при Н.-7/2-. ,. 6) Х; . + г-.х,. , ) Y, Y,..,,, где X; , Y.- - коды, содержащие только старших р рядов множимого X множителя Y; f|,X.,2,- - очередные цифры оп рандов и результат причем X,,у,, Z, 6 1, о, Как видно из приведенного ал оритма, операнды и результат предст лены в двоичной избыточней системе счисления с цифрами {Т, 0,1. При этом положительные и отрицательные цифры чисел хранятся в разных регистрах, а именно положительные цифры чисел Х- и Xj хранятся соответственно в регистрах 2 и 3, а отрицательные - в регистрах б и 4 Выполнение операции, например, вычитания двух чисел в этом случае может быть сведена к сложению на обычных сумматорах дополнительных кодов содержимых указанных четырех регистров. : 0,111, а Пусть Х - 0,1011. Тогда на регистрах указанные числа будут представлены:следуквдим образом; - 3 6,0010 1 с - п П1 n-i ,0101 0,1010 ,а операция вычитани Yf--- o,oooi -) - ( ) сведется к сумм рованию четырех кодов: (прямой код положительной части X)) 11,1010 (дополнительный код отр тельной части Х ) 11,0101 (дополнительный код поло тельной час THY;) (прямой код отрицательной 0,0001 1 11,0100J части YJ (дополнительный код резул тата 12 Тб При такой организации вычислите ного процесса на выходах сумматора 15 будет формироваться дополнитель ный код Hj . Анализ двух знаковых разрядов h и Vig и старшего разряд ма нтиссы.-, величины позволяет судить о том, какая цифра 0,1 или 1 должна формироваться в i-м разряде 2,- результата. Для этого достаточно в соответствии с табл.1 реализовать две функции - - Г1 при Z- 1 Н-|0 при 2,1 Из та6л.1 следует, что f-rS-bo И ,(4b Логическая функция f. реализована с помощью элементов И 34 .и запрета 32, а f - с помощью элементов ИЛИ 35 и запрета 33. Определение величин 2R- и Р,- Н - 2,- осуществляется одновременно 2R,- - путем сдвига R-, а Н - Z - путем отбрасывания знаковых разрядов Н,- и занесения в эти разряды во время сдвига содержимого старшего разряда мантиссы Н. Например, при Hi 00,1..., Z 1 и для получения R из Н. надо вычесть 1, т.е. Н. 00,1... -Z: -1 R; 11,1.,. 2Ri 11,... Этот же результат можно получить путем отбрасывания нулей из знаковых разрядов и занесения на их позиции цифры 1 из старшего разряда мантиссы. Указанные действия нельзя производить при четырех и пяти комбинациях цифр -h. , lip и -h, из табл.1, но такие комбинации при правильной реализаций описанного алгоритма не могут возникнуть. В табл.2 показан пример вычисления всех разрядов произведения 2. соответствии с приве- денным алгоритмом для X 0,1011111 и Y 0,111101 Если необходимо получать не все разряды произведения, то процесс вычисления надо прервать на соответствующем цикле. Например, для получения -h значащих цифр надо выполнить ( h+3) цикла. При этом регистры операндов X и V можно укоротить до ( - +1) разрядов при четном п или ,5) разрядов при нечетном. Такая разрядность регистров позволяет получить погрешность, не превышающую половины единицы младшего разряда произведения. Покажем это, например, для четного п. Если в регистрах операндов не хранятся () младших разрядов X и Y , то абсолютная величина погрешности не превышает произведения двух (гт/2-1) разрядных чисел,состоящих из одних единиц. т.e.|лU(, -2п-3 вес младшего разряда произведения. Отсюда /л| « 2. Таким образом, в результате вычислений получаем ( п+3) точных разрядов про изведения , Для представления Н необходимо (п.З алгоритма)на пять разрядов больше, чем для представления X и Y,. т.е. (п/2+б) разрядов, а регис 20 суммы содержит (п/2+5) разрядов, так как информация с выходов 19 суммирунвдего блока в регистр 20 передается со сдвигом на один разряд влево. При нечетном п здесь и далее STcasaHHHe количества разрядов еледует округлять до ближайшего большего целого числа. Суммирование кодов с выходов регистров 2, 3, 4, 6, 9, 17 и 20, а также с выходов элементов ИЛИ 23 и 25 и запрета 28 производится без распространения переноса, что позволяет существенно ускорить вычисления. Однако в этом случае усло няется определение 2 с помощью ана лиза старших разрядов Н , что приводит к усложнению функций f и , . Чтобы избежать этого, сумматр 43 построен с распространении переноса в пяти старших разрядах, что позволяет производить анализ старших разрядов Н; с помощью табл.1. Вычисление произведения в предлагаемом устройстве осуществляется за ()-циклов. К началу , каждого -гo цикла на входах 1 и 5 устройства присутствует очередная цифра х,-,а на входах 7 и 8 - очеред ная цифра . При этом единица в очередном разряде сомножителя кодируется единичным сигналом на входах 1 и 7, минус единица - единичным сигналом на входах 5 и 8,а нуль кодируется отсутствием сигналов на обоих входах, представляющих данный сомножитель. В суммлрующем блоке 15 производится сложение кодов, присут ствугацих на его входах. Рассмотрим,например, случай, когда к. 1, а S 1 (единичные сигналы поступают на входы 1 и 8). Тогда на входы суммирующего блока поступят обратные коды содержимого регистров 2 4 и прямые коды содержимого регистров б и 3. Кроме того, единицы с вы ходов элементов ИЛИ 23 и 25, поступакщие на входы 22 и 26 суммирующег блока 15, дополнят { -О- +1) -разрядн коды регистров 2 и 4 до ()-разрядных единицами в старших разрядах а также прибавят единицы в младюте разряды для образования дополнительного кода. На входы 14 суммирующего . блока 15 поступит также обратный код сдвигающего регистра 9, а единица с выхода элемента запрета 28 дополнит этот код единичными старшими разрядами и добавит единицу в младший разряд. После окончания суммирования в суммирующем блоке 15 на выходах 36 и 37 присутствует значение очередного разряда результата 2, причем, если единица присутствует на выходе 37, то 1, если на выходе 36, то Z: г1, в противнем случаб .Zv 0. По единичньм сигналам с входов 1 и 8, поступающим на цепи приема кода . первого регистра 2 множимого и втр рого регистра 4 множителя, во вспомогательные триггеры регистров 2 и 4 записывается-содержимое сдвигающе- . го регистра 9, а именно единица в ч-е разряды. Затем на вход 38 поступает управляющий сигнал, по которому во : вспомогательные триггеры регистров 20 и 17 суммы и переносов записываются слова с выходов 19 и 16, суммирующего блока 15, а также производится подготовка сдвига сдвигающего регистра 9. После этого с входов 1, 5, 7 и 8 снимаются сигналы, соответствующие значениям у и у, и информация из вспомогательных триггеров регистров 2 и 4 переписывается в основные. По окончании управляющего сигнала на входе 38 происходит прием кода на основные триггера в регистры 17 и 20 переносов и суммы, а также сдвиг содержимого сдвигающего регистра 9 на один разряд вправо. Передача кодов с выходов суммирующего блока 15 на входы регистров 17 и 20 производится со сдвигом. В два старших разряда регистра 20 суммы записывается информация с выхода третьего разряда выходов 19. В каждый -(-и разряд регистра 17 информация записывается соответственно с ( i+l)-x разрядов выходов 19 и 16. На этом заканчивается один цикл вычислений. В результате выполнения (п+3)-х циклов на выходах устройства последовательным кодом начиная со старших разрядов формируется значение произведения 2 2-3xY, где Z,-6fl, О, 1. В каждом J-M цикле { j п/2+1) регистр 9 будет находиться в нулевом состоянии и содержимое регистров 2, 3, 4 н б меняться не будет. Время(Необходимое для выполнения одного цикла вычислений в предлагаемом устройстве, состоит из времени tp суммирования в суммирующем Ьлоке 15 уИ. времени сдвига i.в регистре 9.

Время приема информации на регис ры применяют равньм Составляющая -t состоит из времени, необходимго для сложения слов на пяти суммаггорах без распрострг нения переноса, НТО составляет 5 t. ( -t задержка (сигнала в одноразрядном сумматоре) , и времени, необходимого для распространения переноса в пяти старцшх

разрядах сумматора 43. Это время при последовательной организации цепей переноса можно принять равным 51.

Тогда

..Ч сАв + СА Таким образом, быстродействие предлагаемого устройства в

t,2(n.Mt,n, Ч .

раз Bfcmie быстродействия известного устройства, если в последнем используются С5 мматоры с последовательные переносом Например, при Н :; 48 получим р 10.

В устройстве можно также уменьшить tjj введением цепей ускоренного распространения переноса в пяти

0 старших разрядах суьшатора 43« Причем это -.не приведет к существенному, увеличению аппаратурных затрат, как в известном устройстве, где перенос распространяется через /

g весь сумматор, имекщий (п+2) разрядов .

Таким образом, введение новых . элементов и конструктивньк связей позволяет увеличить быстродействие предлагаемого устройства

Таблица 1

Т а б л и ц а 2,

,Y.,

00,000100000

Продолжение табл. 2

13loiiii о 111101 о о

14101111 о 111101о о

15101111 о iiiioi о 1

риг.

Продолжение табл. 2

2«14 l

7Р

36

ф1Аъ.г

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ОГРАНИЧИТЕЛЬ НАПРЯЖЕНИЯ ХОЛОСТОГО ХОДА ИСТОЧНИКА ПИТАНИЯ СВАРОЧНОЙ ДУГИ | 2004 |

|

RU2276634C1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Дверной замок, автоматически запирающийся на ригель, удерживаемый в крайних своих положениях помощью серии парных, симметрично расположенных цугальт | 1914 |

|

SU1979A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| G, 06 7/39, опублик | |||

| Шеститрубный элемент пароперегревателя в жаровых трубках | 1918 |

|

SU1977A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-12-07—Публикация

1982-02-10—Подача