Изобретение относится к вычислительной технике и может быть использовано в опто- электронных вычислительных устройствах, выполняющих операции над десятичными числами с естественным положением запятой.

Целью изобретения является расширение области применения за счет возможности обработки информации с естественным положением запятой.

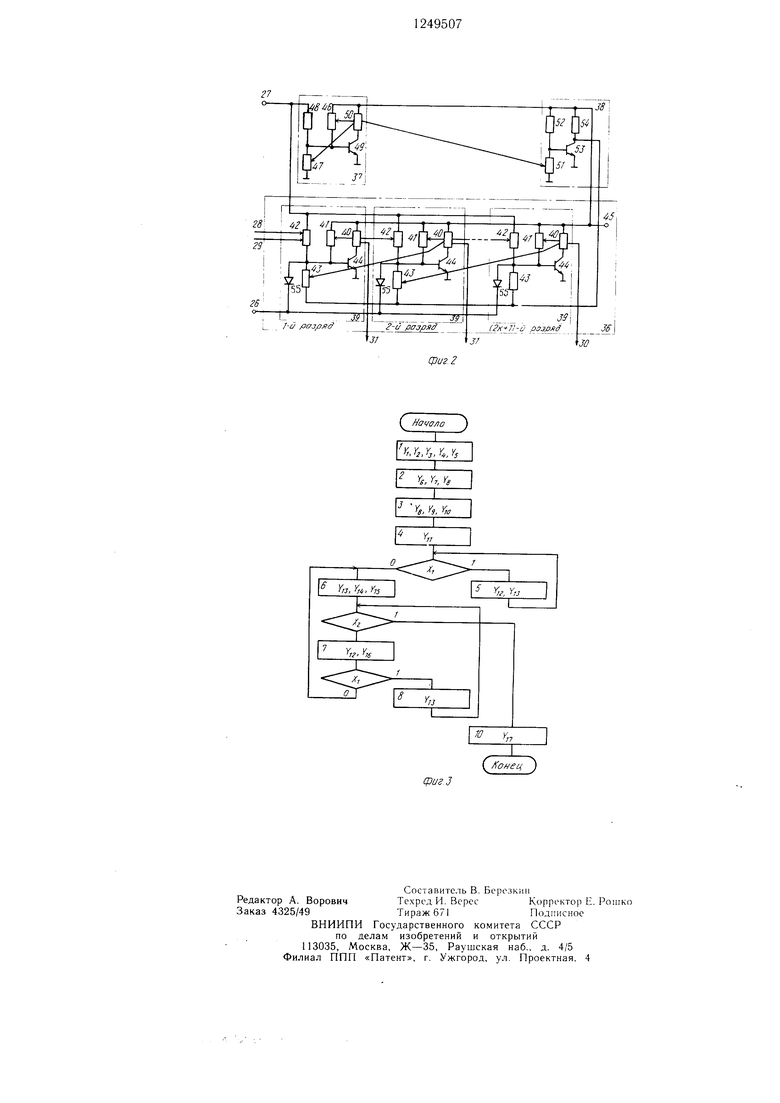

На фиг. 1 представлена блок-схема устройства для умножения; на фиг. 2 - принципиальная схема сумматора анализа положения запятой; на фиг. 3 - алгоритм работы программного блока управления.

Устройство умножения (фиг. Г) содержит регистр 1 множителя, сумматор 2, генератор 3 кратных множимого, сумматор 4 анализа положения запятой, счетчик 5 разрядности множителя, программный блок 6 управ- ления и узел 7 анализа знаков. Управляющие входы 8 и 9 регистра множителя соединены с выхода.ми программного блока 6 управ;1ения и являются соответственно входами управления записью множителя, осу- 1цествляющейся по информационному входу 10 регистра i, и сдвигом влево содержимого регистра 1 м 1ожителя. Выход старшего (fe + l)-ro разряда сумматора 2 соединен с информационным входом младшего разряда регистра 1, а управляющий вход 11 регистра 1 множителя и управляюший вход 12 знакового разряда регистра соединены с выходами программного блока 6 управления и являются соответственно входом обну- лепия регистра 1 и входом управления за- шсью знака произведения в знаковый разряд регистра 1. Информационный вход знакового разряда регистра 1 соединен с выходом узла 7 анализа знаков, один из входов которого соединен с выходом знакового разряда регистра 1, а на второй вход поступает знак множимого. Управляющий вход 13 старшего k-ro разря;1,а регистра 1 соединен с соответствующим выходом программного блока 6 управления. Информационный многоразрядный выход старшего fe-i O разряда регистра 1 множителя соединен с информационным входом 14 генератора 3 кратных множимого, а выход 15 признака нуля в -м разряде регистра 1 соединен с соответствук,)- П1ИМ входом программного блока 6 управления.

Управляюший вход 16 сумматора 2 соединен с выходом программного блока 6 управлепия и является входом управления записью информации в сумматор 2, а информационный вход 17 сумматора 2 соединен с информационным выходом генератора 3 кратных множимого.

Управляющие входы 18 и 19 сумматора 2 соединены с выходами программного блока 6 управления и являются соответственно входом обнуления и входом управлепия сдвигом влево информации в сумматоре 2. Bxozi

0

0

0

0

5

20 запуска программного блока 6 управления является входом запуска устройства.

Управляющий вход 21 генератора 3 кратных множимого соединен с соответствующим выходом программного блока 6 управления и является входом управления записью множимого. Информационный вход 22 генератора 3 кратных множимого является входом множимого А. Управляющие входы 23-25 соединены с выхода.ми программного блока 6 управления и являются управляющим входом управления считыванием соответствующего кратного множимого в сумматор 2, входом установки в начальное состояние генератора 3 кратных множимого и входом унравления формированием кратных множимого в генераторе 3-соответственно.

Управляющие входы 26 и 27 сумматора 4 анализа положения запятой соединены с соответствуюн1ими выходами программного блока 6 управления и являются входом обнуления и входом управлепия записью соответственно.

Информационные входы 28 и 29 сумматора 4 анализа положения запятой являются входами записи разрядности дробной части множимого и мпожи.мого соответственно, а выходы соединены с выходами 30 и 31 индикации положения запятой устройства соответственно.

Управляющий вход 32 счетчика 5, соединенный с выходом программного блока 6 унравления, является входом управления записью разрядности множителя по инфор- мациопому входу 33 счетчика 5. Управляю- П1ие входы 34 и 35 счетчика 5 соединены с соответствующими выходами програм.мно- го блока 6 управления и яв.чяются соответственно входом обнуления и вычитающим входом счетчика 5. Выход нризпака нуля Ро счетчика 5 соединен с соответстующим входом програм.много блока 6 унравления. С выходов pei-истра 1 и сумматора 2 снимаются значения И-, и Па соответственно старших и младших разрядов нроизведения.

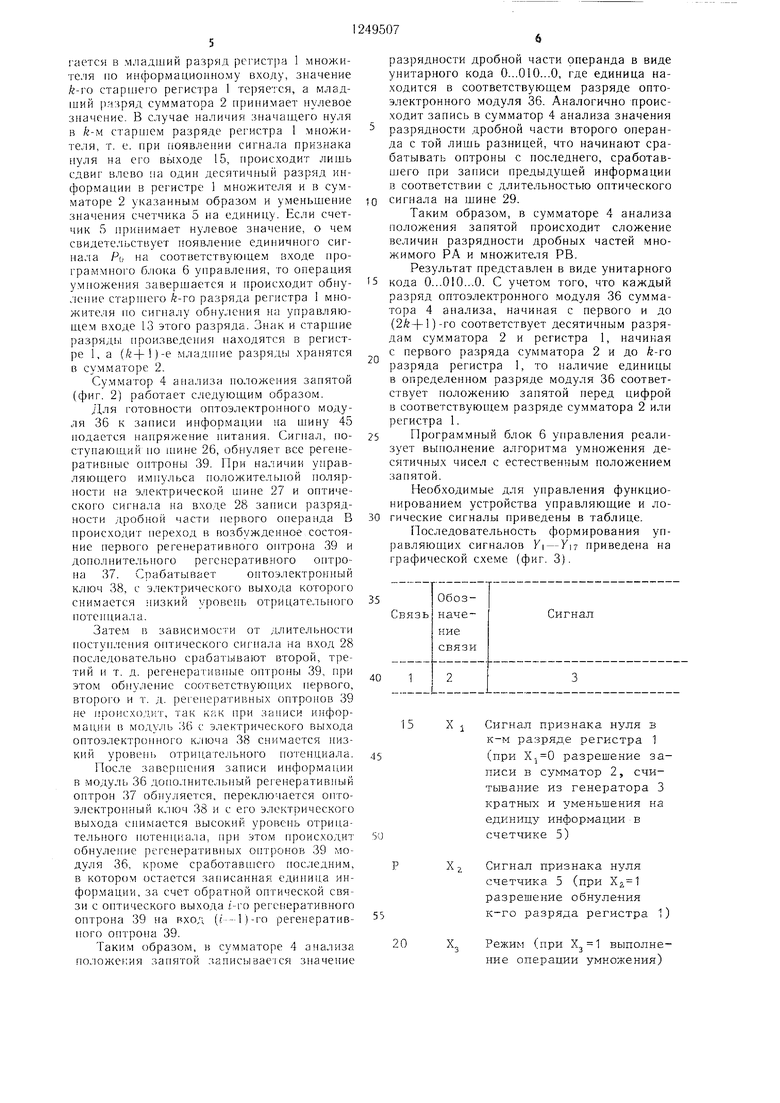

Сумматор 4 анализа ноложения запятой (фиг. 2) состоит из собственного оптоэлект- ронпого (2fe-i-l)-ro разрядного модуля 36, дополнительпого регенеративного оптрона 37 и оптоэлектронпого ключа 38. Каждый из ()-x разрядов оптоэлектронного модуля 36 представляет собой регенеративный оптрон 39, состоящий из источника 40 света, первого 41, второго 42 и третьего 43 фото- приемников, объединенные выводы которых 1Юдключепы к базе транзистора 44. Первый ({)отонрнемник 41 каждого регенеративного онтрона 39 оптически связан с источником 40 света того же регенеративного оптрона 39, второй фотоприемник 42 всех регенеративных оптронов 39, кроме первого, оптически связан с источником 40 света предыдущего разряда, второй фотоприемник 42 первого регенеративного оптрона 39 оптически связан с информационными входами 28 и 29

сумматора 4 анализа положения запятой, которые являются входами записи разрядности дробной части множителя РВ и множимого РА соответственно, третий фотоприемник 43 оптически соединен с источником 40 света последующего разряда. База транзис- тора 44 в каждом разряде подключена через первый фотоприемник 41 к шине 45 положительного полюса источника питания, через второй фотоприемник 42 - к электрической управляющей шине 27, а через третий фото- ю приемник 43 - к выходу оптоэлектронного ключа 38.

Кроме того, база транзистора 44 подключена к аноду диода 55, катод которого подключен к щине 26 обнуления. Коллектор

регистра 1 находится его старщая значащая цифра. Одновременно в счетчик 5 по информационному входу 33 записывается значение разрядности М множителя при наличии сигнала на его управляющем входе 32. В сумматор 4 анализа положения запятой результата по информационному входу 28 записывается значение разрядности РВ дробной части множителя. Затем записывает ся второй операнд А параллельно по разрядам в генератор 3 кратных множимого, поступая на его информационный вход 22. В сумматор 4 анализа по информационному входу 29 поступает запись значения разрядности РА дробной части множимого А. Одновременно с записью второго операнда А знаки множитранзистора 44 через источник 40 света под- 5 теля В и множимого А поступают на входы

ключен к щине 45, а эмиттер - к общей шине. Оптические выходы источников 40 света первых (Л+1)-х регенеративных оп- тронов 39 являются выходами 31 сумматора 4 анализа, а оптические выходы регенеративных оптронов 30, начиная с (й+2)-го и до (2/fe- -l)-ro, являются выходами 30 сумматора 4.

Дополнительный регенеративный опт- рон 37 состоит из первого 46 и второго 47

узла 7 анализа знаков, который формирует знак произведения, поступающий в знаковый разряд регистра 1 множителя при наличии разрешающего сигнала на его управляющем входе 12. Формирование кратных множимого происходит в генераторе 3 при наличии сигналов, поступающих из программного блока 6 управления на управляющий вход 25 генератора 3 кратных множимого. Умножение происходит, начиная со старщих разряфотоприемников, резистора 48, первые объ- 25 дов множителя. В случае, если множитель В

единенные выводы которых подсоединены к базе транзистора 49, и источника 50 света, первый вывод которого подключен к коллектору транзистора 49. Второй вывод резистора 48 подключен к электрической управявляется неправильной дробью, т. е. когда после запятой и перед старшей значащей цифрой множителя находится некоторое число нулей, то выполняется нормализация дроби путем последовательного сдвига влево

ляющей шине 27. Эмиттер транзистора 49 30 информации в регистре 1 на один десятичный

и второй вывод второго фотоприемника 47 подключены к общей щине, источник 50 света оптически связан с первым фотоприемником 46, вторым фотоприемником 47, а также с фотоприемником 51 оптоэлектронного ключа 38. Вторые выводы источника 50 света 35 и первого фотоприемника 46 подключены к шине 45. Оптоэлектронный ключ 38 состоит из фотоприемника 51, режимного резистора 52, первые объединенные выводы которых подсоединены к базе транзистора 53, и нагрузочного резистора 54.

Коллектор транзистора 53 через нагрузочный резистор 54 подсоединен к шине 45, с которой соединен также второй вывод режимного резистора 52. Эмиттер транзистора 53 и второй вывод фотоприемника 51 соединены с общей шиной.

Устройство для умножения десятичных чисел работает следующим образом.

Происходит- установка в начальное состояние регистра 1 множителя, сумматора 2, генератора 3 кратных множимого, сумматора 4 анализа положения запятой и счетчика 5 по сигналам, поступающим на управляющие входы II, 18, 24, 26 и 34 этих блоков соответственно.

Производится запись первого операнда В в регистр 1 по информационному входу 10 при наличии сигнала управления записью на входе 8 регистра 1. Причем множите.ть В записывается так, что в старщем -м разряде

разряд и одновременного уменьшения содержимого счетчика 5 на единицу. Сдвиг продолжается до тех пор, пока в старшем ft-M разряде регистра 1 не появится старшая значащая цифра множителя, о чем свидетельствует появление соответствуюн его сигнала на его выходе 15.

С информационного многоразрядного выхода старшего /г-го разряда регистра 1 .множителя на вход 14 генератора 3 посту- ,Q пает информационный сигнал, выбирающий кратное, соответствующее значению десятичной цифры в й-м разряде регистра 1.

Соответствующее кратное множимого поступает на информационный вход 17 сумматора 2 при наличии сигнала управления 45 считыванием на управляющем входе 23 генератора 3 кратных множимого. Выбранное кратное суммируется с содержи.мым сумматора 2 при наличии сигнала управления записью на управляющем входе 16 сумматора 2. Значение счетчика 5 разрядности множителя при этом уменьшается на единип,у после прихода сигнала на его управляющий вход 35. Затем происходит сдвиг влево на один десятичный разряд информации в регистре 1 множителя и сумматоре 2 под действием сигналов управления сдвигом, поступающих на управляюн ие входы 9 и 19 регистра множителя и сумматора 2 соответственно. При этом информация из старшего (k-i-D-ro разряда сумматора 2 сдви50

55

регистра 1 находится его старщая значащая цифра. Одновременно в счетчик 5 по информационному входу 33 записывается значение разрядности М множителя при наличии сигнала на его управляющем входе 32. В сумматор 4 анализа положения запятой результата по информационному входу 28 записывается значение разрядности РВ дробной части множителя. Затем записывает ся второй операнд А параллельно по разрядам в генератор 3 кратных множимого, поступая на его информационный вход 22. В сумматор 4 анализа по информационному входу 29 поступает запись значения разрядности РА дробной части множимого А. Одновременно с записью второго операнда А знаки множи теля В и множимого А поступают на входы

узла 7 анализа знаков, который формирует знак произведения, поступающий в знаковый разряд регистра 1 множителя при наличии разрешающего сигнала на его управляющем входе 12. Формирование кратных множимого происходит в генераторе 3 при наличии сигналов, поступающих из программного блока 6 управления на управляющий вход 25 генератора 3 кратных множимого. Умножение происходит, начиная со старщих разряявляется неправильной дробью, т. е. когда после запятой и перед старшей значащей цифрой множителя находится некоторое число нулей, то выполняется нормализация дроби путем последовательного сдвига влево

5

разряд и одновременного уменьшения содержимого счетчика 5 на единицу. Сдвиг продолжается до тех пор, пока в старшем ft-M разряде регистра 1 не появится старшая значащая цифра множителя, о чем свидетельствует появление соответствуюн его сигнала на его выходе 15.

С информационного многоразрядного выхода старшего /г-го разряда регистра 1 .множителя на вход 14 генератора 3 посту- Q пает информационный сигнал, выбирающий кратное, соответствующее значению десятичной цифры в й-м разряде регистра 1.

Соответствующее кратное множимого поступает на информационный вход 17 сумматора 2 при наличии сигнала управления 5 считыванием на управляющем входе 23 генератора 3 кратных множимого. Выбранное кратное суммируется с содержи.мым сумматора 2 при наличии сигнала управления записью на управляющем входе 16 сумматора 2. Значение счетчика 5 разрядности множителя при этом уменьшается на единип,у после прихода сигнала на его управляющий вход 35. Затем происходит сдвиг влево на один десятичный разряд информации в регистре 1 множителя и сумматоре 2 под действием сигналов управления сдвигом, поступающих на управляюн ие входы 9 и 19 регистра множителя и сумматора 2 соответственно. При этом информация из старшего (k-i-D-ro разряда сумматора 2 сдви0

5

. ается в младший разряд регистра 1 множителя по ин{рормациоиному входу, значение k-ro старшего регистра 1 теряется, а младший разряд сумматора 2 принимает нулевое значение. В случае наличия значащего нуля в k-M старн1ем разряде регистра 1 множителя, т. е. нри Г1оявлении сигнала признака нуля на его выходе 15, происходит лишь сдвиг влево на один десятичный разряд информации в регистре 1 множителя и в сумматоре 2 указанным образом и уменьшение значении счетчика 5 на единицу. Если счетчик 5 принимает нулевое значение, о чем свидетельствует ноявление единичного сигнала Р(: на соответствующем входе программного блока 6 унравления, то операция умножения завершается и происходит обну- .чение CTapniero -го разряда регистра 1 множителя но сигналу обну;1ения на управляющем входе 13 этого разряда. Знак и старшие разряды произведения находятся в регистре 1, а (/г-(-1)-е млад1иие разряды хранятся в сумматоре 2.

Сумматор 4 анализа положения запятой (фиг. 2) работает следующим образом.

;1,ля готовности онтоэлектронного модуля 36 к записи информации па шину 45 подается напряжение питапия. Сигнал, поступающий по шине 26, обнуляет все регенеративные онтропы 39. При наличии угфав- ляюнхего импульса положительной поляр- пости на электрической шине 27 и оптического сигнала па входе 28 записи разрядности дробной части первого операнда В нроиеход,ит переход в возбужденное состояние первого регенеративного оптрона 39 и дополнительного реге} еративного огггро- на 37. Срабатывает оптозлектронпый ключ 38, с электрического выхода которого снимается Шзкий уровень отрицательного нотепциа.ла.

Затем в зависимости от д.лительпости ностунления оптического сигнала на вход 28 последовательно срабатывают второй, тре тий и т. д. регенеративные оптроны 39, при этом обнуление сос)тветствуюн).их нервого, второго и т. д. регенеративных онтропов 39 не пр()исхо;,ит, так как нри записи информации в модуль 36 с электрического выхода онтоэлектронного ключа 38 снимается низкий урове1п отрицательного потенциала.

После завершения записи информации в модуль 36 доно:1нительный регенеративный оптрон 37 обнуляется, нереключается онто- электронный ключ 38 и с его электрического выхода снимается высокий уровень отрицательного нотенц11а;1а, нри этом нроисходпт обнуле)и1е р4М енеративных оптронов 39 модуля 36, кроме сработавшего ное;1едпим, в котором остаетея занисанная: единица ип- фор.мацпи, за счет обратной оптической связи с онтического выхода J-ro регенеративного оптрона 39 на вход (г1}-го регенеративного онтрона 39.

Таким образом, в сумматоре 4 анализа нoлoл ;e ;ия запятой записывае 1ся значение

разрядности дробной части операнда в виде унитарного кода 0...010...0, где единица находится в соответствующем разряде опто- электронного модуля 36. Аналогично нроис- ходит запись в сумматор 4 анализа значения

разрядности дробной части второго операнда с той лищь разницей, что начинают срабатывать оптроны с последнего, сработавшего при записи предыдущей информации в соответствии с длительностью оптического

сигнала на шине 29.

Таким образом, в сумматоре 4 анализа положения запятой нроисходит сложение величин разрядности дробных частей множимого РА и множителя РВ.

Результат представлен в виде унитарного

кода 0...010...0. С учетом того, что каждый разряд оптоэлектронного модуля 36 сумматора 4 анализа, начиная с первого и до (2/г+1)-го соответствует десятичным разрядам сумматора 2 и регистра 1, начиная

с нервого разряда сумматора 2 и до k-ro разряда регистра 1, то наличие единицы в определенном разряде модуля 36 соответствует положению запятой перед цифрой в соответствующем разряде сумматора 2 или регистра 1.

Программный блок 6 угфавления реализует выполнение алгоритма умножения десятичных чисел е естественным положением запятой.

Необходимые для управления функционированием устройства управляющие и логические сигналы приведены в таблице.

Последовательность формирования уп- равляюп1их сигналов Y - /i приведена на графической схеме (фиг. 3).

15 X i Сигнал признака нуля в к-м разряде регистра 1 (при разрешение записи в сумматор 2, считывание из генератора 3 кратных и уменьшения на единицу информадии в счетчике 5)

Xj Сигнал признака нуля счетчика 5 (при Х2, 1 разрешение обнуления разряда регистра 1)

Х„ Режим (при X, выполнение операции умножения)

III

Продолжение таблицы 3

У;17 Обнуление к-го разряда регистра 1

15

20

25

состояние генератора 3 кратных множимого

Установка в начальное

состояние сумматора анализа положения запятой

Yj, Запись в регистр 1 У7 Запись в счетчик 5

УЗ Запись в сумматор 4 анализа положения запятой

Уд Запись в генератор 3 кратных множимого

УЮ Запись в знаковый разряд регистра 1

УЛ Формирование кратных

множимого в генераторе 3

Сдвиг влево в регистре 1 35

, Вычитание единицы в счетчике 5

У, Запись в сумматор 2

У15 Считывание из генератора кратных множимого

30

О

У16 Сдвиг влево в сумматоре 2 5

1.Устанавливаются в начальное состояние регистр 1 множителя, сумматор 2, сумматор 4 анализа положения запятой, генератор 3 кратных множимого и счетчик 5.

2.В регистр 1 множителя записывается значение первого операнда, в сумматор 4 анализа положения запятой - значение разрядности дробной части первого операн

да, в счетчик 5 - разрядность первого операнда.

3.В генератор 3 кратных множимого записывается значение второго операнда. в сумматор 4 анализа положения запятой значение разрядности дробной части второ1Ч) операнда, в знаковый разряд регистра I - значение знака результата.

4.Формируются кратные множимого в генераторе 3 кратных множимого.

5.Определяется равенство значения десятичной цифры в старшем k-м разряде регистра 1 множителя нулю. Если десятичная цифра в старшем k-м разряде регистра 1 множителя равна нулю, то происходит сдвиг влево на один десятичный разряд информации в регистре 1 и уменьшение содержимого счетчика 5 на единицу. Сдвиг выпо.лняется до тех пор, пока в старшем /г-м разряде регистра 1 не появится значащая цифра множителя.

6.Если десятичная цифра в старп1см k-M разряде регистра 1 множителя не равпа нулю, то происходит выборка соответствующего кратного из генератора 3 кратных, сложение содержимого сумматора 2 с выбранным кратным и уменьшение содержимого счетчика 5 на единицу.

7.Определяется равенство значения счетчика 5 нулю. Если значение счетчика 5 не равно нулю, то происходит сдвиг влево на один десятичный разряд информации в сумматоре 2 и регистре 1 множителя.

8.Определяется равенство ну;по :я1аче- ния десятичной цифры в старшем fe-м раз)я- де регистра 1 множителя. 1Если десятичная цифра в старшем k-м разряде регистра I равна нулю, то происходит уменьшение значения счетчика 5 на единицу, а затем выполняется п. 7.

9.Если значение десятичной цифры г, старшем й-м разряде регистра 1 не равло нулю, выполняется п. 6.

10.Если значение счетчика 5 равно ny;iK), то происходит обпуление ciapniero k-ro ря: ряда регистра 1. Операция у.мпожеппя завершена.

Формула изобретения

Устройство для умножеиия, содержащего регистр множителя, накапливающий сумма тор, генератор кратпых множимого, узс.1 формирования знаков, счетчик и программный блок управления, причем вход множителя устройства соединен с информациоппым входом регистра множителя, вход мпожнмо- го устройства подключен к информационному входу генератора кратных множимого, выход знакового разряда регистра множпюля подключен к первому входу узла фор.п1- рования знаков, выходы программного б.юкп управления с первого по третий подключены соответственно к входам обнуления регистра

множителя, накапливающего сумматора и счетчика, четвертый и штый выходы программного блока управления подключены к входам управления записью регистра множителя и накапливающего сумматора, выход старшего информационного разряда накапливающего сумматора подключен к информационному входу младшего информационного разряда регистра множителя, шестой выход программного блока управления подключен к входу управления записью счетчика, выход признака равенства нулю которого подключен к входу признака окончания счета программного блока управления, седьмой, восьмой и девятый выходы которого подключены соответственно к входу управления сдвигом регистра множителя, счетному входу счетчика, входу управления сдвигом накапливающего сумматора, двенадцатый выход программного блока управления подключен к управляющему входу геператора кратных множимого, вход запуска программного блока управления соединен с входом запуска устройства, информационный вход счетчика является входом разрядности множителя устройства, десятый и одиннадцатый выходы программного блока управления соединены с входами управления записью знака и обнуления старшего k-ro разряда регистра множителя соответственно, выход признака нуля старшего k-ro разряда регистра множителя подключен к входу признака выполнения сложения в данном такте программного блока управления, второй вход узла формирования знака соединен с входом знака множимого устройства, выход старшего k-ro

0

5

0

разряда регистра множителя подключен к входу управления значением кратности генератора кратных множимого, выход которого соединен с информационным входом накапливающего сумматора, выходы разрядов которого соединены с выходами млад- HJHX разрядов произведения устройства, выходы разрядов регистра множителя соединены с выходами старших разрядов произведения устройства, двенадцатый, тринадцатый, четырнадцатый и пятнадцатый выходы программного блока управления соединены с входом установки в начальное состояние, входом управления записью, входом управления считыванием и входом управления формированием кратных генератора кратных множимого соответственно, отличающееся тем, что, с, целью расп ирения области применения за счет обеспечения возможности обработки информа |ии с естественным положением запятой, устройство содержит сумматор анализа положения запятой, два информационных входа сумматора анализа положения занятой соединены с входами разрядности дробных частей множимого и множителя устройства соответственно, выходы сумматора анализа положения запятой подключены к входам индикации положения запятой устройства, шестнадцатый и семнадцатый выходы программного блока управления соединенЬ) с входом установки в начальное состояние и входом управления записью сумматора анализа положения запятой, выход узла формирования знака подключен к входу знакового разряда регистра множителя.

Р ,РВ

т ро

27

фиг. 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Устройство для умножения десятичных чисел | 1984 |

|

SU1198514A1 |

| Устройство для умножения десятичных чисел | 1981 |

|

SU1016780A1 |

| Арифметическое устройство | 1988 |

|

SU1578708A1 |

| Арифметическое устройство | 1971 |

|

SU522497A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Устройство для умножения десятич-НыХ чиСЕл | 1979 |

|

SU817704A1 |

| Множительное устройство | 1979 |

|

SU832554A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

Изобретение относится к вычислительной технике и может быть использовано в оп- тоэлектронных вычислительных устройствах, выполняющих операции над десятичными числами с фиксированной запятой. Целью изобретения является расширение области применения за счет обеспечения возможности обработки информации с естественным положением запятой. Это достигается тем, что устройство для умножения содержит сумматор анализа положения запятой. Использование в предлагаемом устройстве узла анализа положения запятой позволяет выполнять умножение десятичных чисел с естественным положением запятой с высоким быстродействием, предусмотренным устройством для умножения десятичных чисел, взятым в качестве прототипа. Одновременно с этим устройство для умножения может эффективно выполнять обработку целых чисел, которые р данном случае можно рассматривать как частный случай представления десятичных чисе.; с естественным положением запятой, ,;i разрядность дробной части чисел равна пулю. 3 ил, 1 табл. го 4 ;о ел

| Устройство для умножения | 1982 |

|

SU1136151A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-08-07—Публикация

1984-08-06—Подача