Изобретение огноглп., к р-диогехнике /i Г cxei использов,г ся /и р пряемг и пеое- да и информации

Цель кзобретзимi - повышение помехоустойчивости

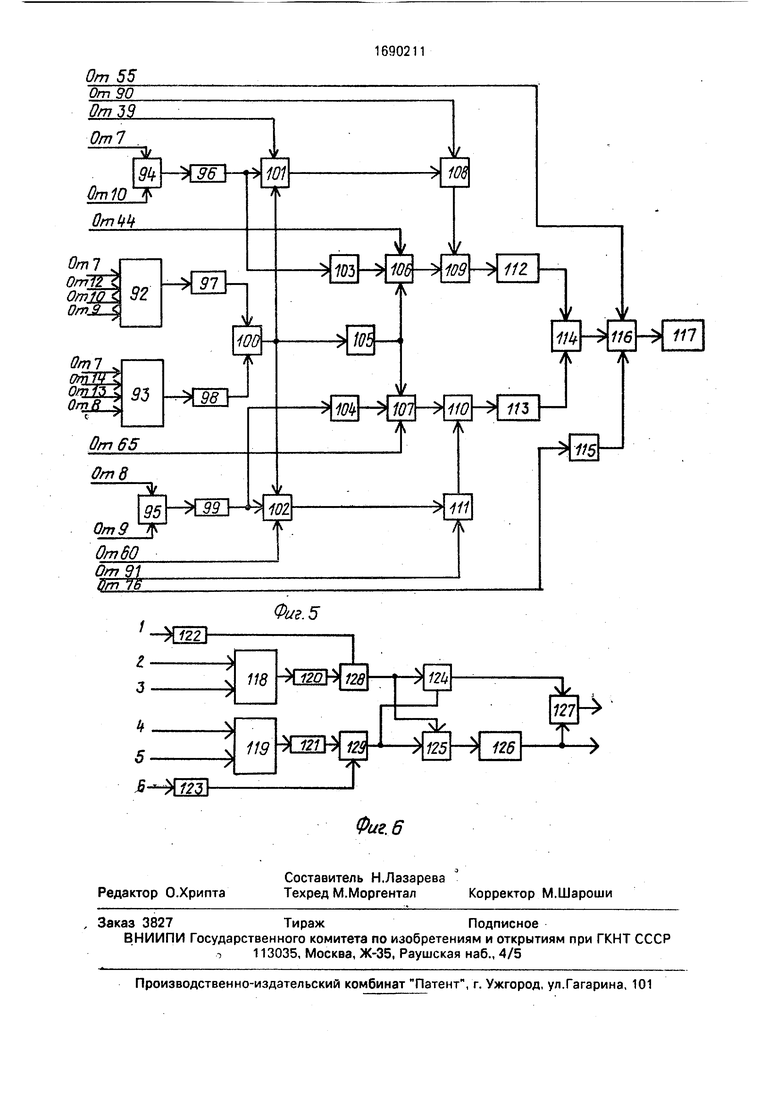

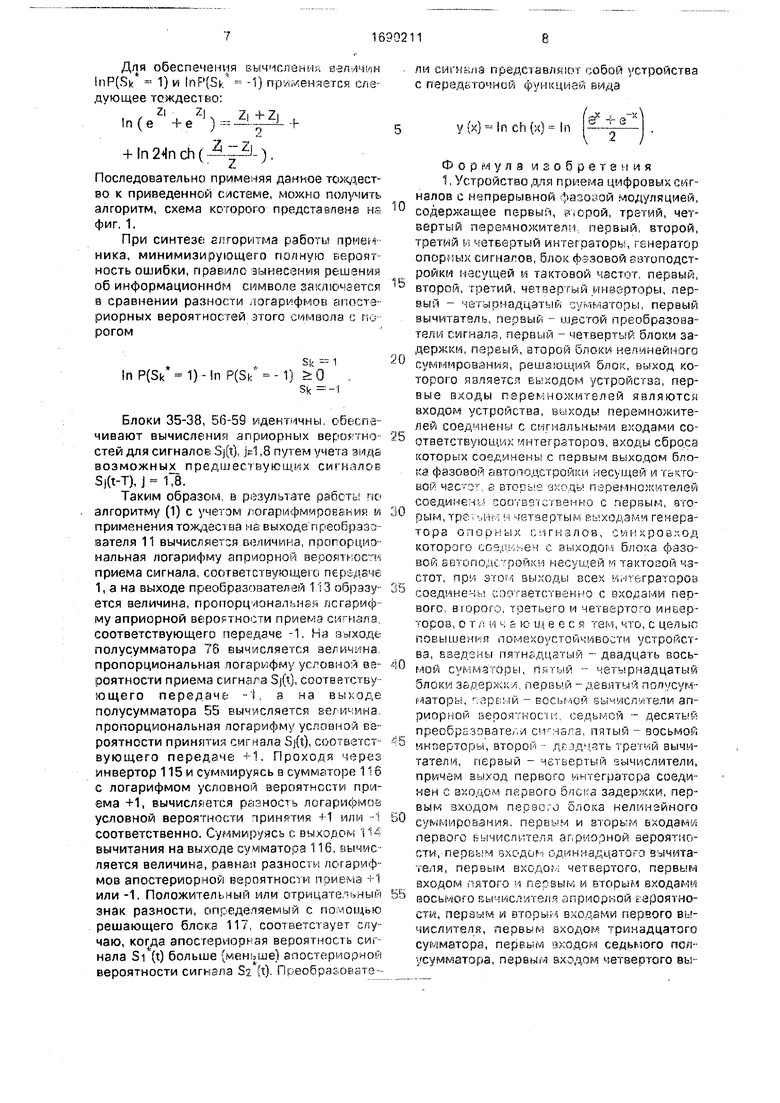

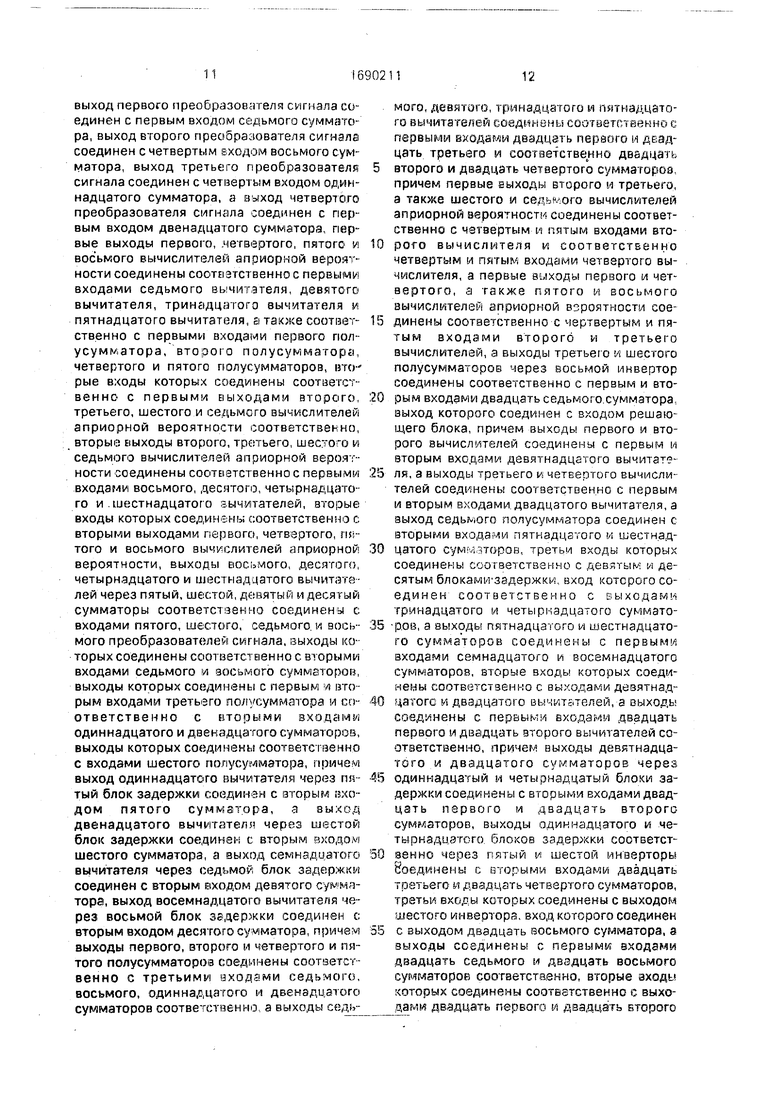

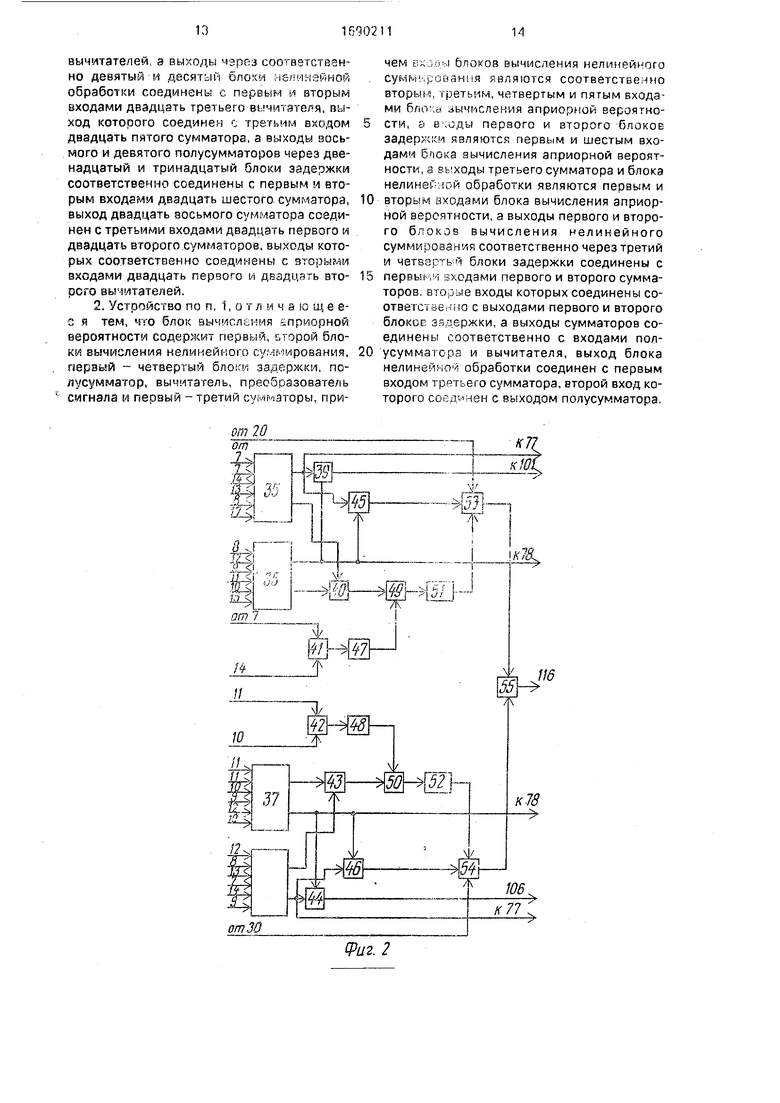

На фиг 1-5 приведете f трукгурная элэч- трическая схема прелагаемого устройства; на фи 6 - схеме бло :& зь числе- ич апрмор ной вероятности

Устройство содержим блок 1 фаговой гвюподстройки несущей / тактовой частот, генератор 2 опорных мп глоз, переый-чег вертый перемнож/ тэш f, пероы7гчегвер- тый s/JHTei раторы 7-0 ерваш-че зерть и инзерторы 11-14 пэриый, второй блоки 15 и 16 нелинейного суммиосл гния, перв й-чз- вертый блоки 17-20 С здер К, ч горой, гре тий, первый-четверг ыи сумматоры 21-24с первый-чегвертый вичшагели 25-28, пер- вый-четвертый преоЈ 0Јз шатели 20-32 сиг нала, пятый, шее го вычитагепи 13 (л 34 первый-четвертый вычис/ мтели 35-38 априорной вероятности Сйдьмо, восьмой, одиннадцатый, ДЕен дцзтый, десятый, девятый вычитателм 3) 44, первый, второй полусумматоры 45 и 4h, пятый, шестой блоки 47 и 48 з.э.с ержп пятый, шестой сумматоры 49 и 50, пный, шее гой преобразователи 51 и 52 сиг1- ала, седьмой, восьмой сумматоры 53 и 54, полу; умметор 55, пл шй-восьмой вычисли iJjiM Ьб-59 априорной вероятности тринадцатый, четырнэд цатый, семнадцатой, Bocesv над дат ый, шестнадцатый, - п -а/диагый вычитатели 6С 65, четвертый пят 3|й г опусуммагоры 66 и 67, седьмой, восьмой б; оки 68 и 69 злдэр- чки девятый, дгсг ыг ;ум агоры 70-71, седьмой восьмой поеоЕ разовзтег и 7273 cvrvcina, одиннадцатый, двенадцатый зум- чагоры /4 л 75 luec ot4 по/ ус/ммагос 76, первый четвер . ЕЫ i/ели вли 7/-80 седьмой полусумматор Bi, тринз/ ЦсЭ1ый четырнадцатый о / спозы 8, 83, яевят надиатый двадцЕтм Bt nnaiinn 6- и 8т, девятый десятый блок 3 и 87 , пятнадцатый, шес1и«:ццлыи сумматоры 88 и 89, семнадцатый, оосе чадцагым сумма- гору 90 1й 91, восьмой, девятый полусумматоры 92 и 93, ,пЈвя- чадцлтьй, двадцатый сумматоры 94 w 95, од п адиатий-чегыр- надцэтый блоки 9Р 99 и ДЕЛДЦЗТЬ шестой сумматор ИО авадиа ь ПРОЗЫЙ, двадцатьоторо oyf i ia оты 10 -1C1 седьр«той, шестой лнЕ зрторы 103-ЮЕ) цвад- цать третий, двацца г - РТ черты1 еры 106 и 107, два ища ьг грви вычитал ель ЮР. двадцать седьмой 1П9 драдд ь восьмой сумматор 110 л лдцат ь втоосй чы читатель (И, девтой, д f пты прроора -о вагели 112 и 113 гьт на с ивз L,ar- тое ий вь игатепь 114, ЕО( ниемор

двадцать пятый сумматор 116, решающий блок 117, 6 юки вычисления априорной вероятности содержат блоки 118 и 119 вычисления нелинейного суммирования, третий, четвертый, первый второй блоки 120-123 задержки полусумматор 124, вычитатель 125, преобразователи 126 сигнала, третий первый, второй сумма очы 127-129.

Устройство работает следующим образом.

Входной сигнал y(t) Sj(t) + n(t), J 1,8, тредставляет собой аддитивную смесь сигналов Sj(t) с выхода модулятора, обеспечиаагощего 1 М модуляцию с непрерывой фазой (НФМ), доительность которых Т и белого гауссового шума n(t) со спектральной плотностью мощности N НФМ ЧМ модулятор представляет собой последовательно

соединенные предмодуляторный фильтр и ЧМ модулятор На оход НФМ модулятора поступает последовательность противоположных информационных сигналов, длительность которых равна Т, а номер

определяется видом передаваемой информации (0 или 1) Вид сигнала вг выходе пред- модуля горчого фильтра Si(t) (или на входе ЧМ модулятора) определяется сверткой сигнала Si(c it ммпульсчот отклика фильтра

9W

i

n(tj- /S(t)g(T-t)dT,

о

длительность сиг чатов r,(t) равна Т-г Tg, если Тд - длительность импульсного отклика передмодуляюрного фильтоа Проходя через предмодуляторный фильтр, информационные сигналы растяпваютс во времени что приводит к появлению ежсимвольной интерференции При ограничении импульсногэ отклике временем Т интерферируют только сосодние сигналы $Г и Si(t + Т) Таким образом пр подаче на вход фильтра последовогэл-эности информационных сигналов Si на его выходе присутствует послецовательность , искаженных кежсимвольной интерференцией. Поскольку интерферирует го/юко два соседних информационных сигьапч Si (г), то число различных сигналов па выходе предмодуляторного с ильтоа 22 - 6/д сигнала зависит от соседних сигналов Si ft) или, что то же самое, си информационного перехода (i - 1, I - 1). требование непрерывности фазы ЧМ чодулгтора приводит к тому, что

число сигналов на его выходе равно,2 4 8, а п лд, сигнала определяется начальной фазой и видом информационного перехода.

Если К-й информационный сигнал имел сьаченче И(-1), соо(ветствующие ему сиг

алы на выходе НФМ HO.UVTT, , ,-j,,-s - .) или S3(t), Se(t) или SeC-}, i дон (-1) с о- четственНО S2(t) Л Л54(1), S ИЛ -; Saitj. J-OM 6СЛИ

в К-ый момент временм cur ,an ria выходе НФМ модулятора был Si(t), то предшеству- ющие ему сигналы на выходе НФМ модулятора - Si(t) или Se(t}, а последующие - Sift) или Ss(t).

Если передавался сигнал Salt), го предшествующие ему сигналы - S3(t) или Seft), a последующие - Ss(t) или S(t). Если передавался сигнал S2(t), ro предшествующие ему сигналы - S5(t) или S(t). а последующие - Ss(t) или Sq(t); если передавался смг.ал S4(t), то предшествующие еху - S2(t) .-ли 3(т), а последующие - Se(f) илг ЯД), если передавался сигнал 8е(т), то предлестз/ющие ему - S2(t) или S-/(tJ, а послелуощче - Si(0 или Ssft),- если передавался сигнзп , to предшествующие ему - 82(1) ИЛУ. S /(т), ч последующие - Si(t), 85(1). если передавит сигнал Ss(t), то предшествующие ему -и-налы - S ,(x} или S4(t), а последующие - 5б(0 или S2(t), наконец, если передавался сигнал S(t), то предшествующие ему сигналы - 5з( с) или Se(t), последующие за ним - Ss(tj илм-ЗДт.}. Таким образом, последовательность сигналов выхода НФМ модулятора нельзя считать последовательностью crav icT .ec . независимых равновероятных о,мгналсг

НМЛ ДЛИТСЛЬНОСТИ WtV.r-.

предг-лодулягорного фичпоследовательность ::,с

представляет собой трое-.

цепь Мар.сова второго

Вероятность того, что из ,; сн t-м ареале времени передавалась +i р°5на сунне вероятностей приема сигнала SJvi:j, сосн- ветствующих передаче + (J 1,3.6,8). з для -1 соответственно S/i) k, 4, 5 7. В СБОЮ очередь, сами вероятноетм приема сигнала 5j(t), j 1,8, определяются как произведение условной вероятности P(Sj{t)) принятия сигнала Si(t) в К-й момент времени на априорные вероятности наличия возможных сигналов Sj(t-T) в прерыдущий (К-1) и Sj(t+T) в последующие моменты времени (К+1), Это позволяет записать следующую систему:

л ПРИ ск аниче- отклика DC. вр8менем Т, Sjig, j 1,8, ;j сродную

P(Sk 1) (P(Si)k-2 + P(Sa)k-2)P(Si)k-i + + (P(S)k-2 + P(S2)k-2 P(Se)(Si)k(P(Si)k-KZ + + P(S5)k + 2)PfSi)k + i + (P(Se)k + 2 +

+ P(S2)k-b2P(S5)k+lT+(P( P(S6)k-2)P(S3)k-1-b + (P(S5)k-2 + P(S4)k-2P(36)(S3k)(P(S3)k+2 + + P(S)k + 2)P(S3)k+1 + (P(S4)k + 2 + + P(S8)k+2)P(S7)k+l + P(S4)k-2 + P() P(S4)k-1 + (P(Sl)k-2 + P(S8)k-2 P(S5)(S6}kf(P(S3)k+2 +

#P(S7)k+2K(Ss)k + i + (P(Se)k+2 +

P(S4X4-2P(S7)k+l + (P(S4)k-2 + P(S5)k- P( +

(P(S3)k-2 + P(Se)k-4P(S7)k-iJ P(S8)4(P(Si)k+2 +

f t { Ja)k-2P(S l)k + - A (P{Si5)k + 2 + + (S5Vil.

.-.; - -11 - :(p(si)k-2 + р(зйк-2)р( +

-« H b;)k 2 и )k-2jP( i)P(Sz)Px Si)k+2 + + PxS5}k-2%,)k-H 4-(P(S2)k-2 +

+ P(( (P(S3}k-g + P(S6)k-2)(S7)k 1+

+ ()k-2 + P(S4MP(S2)((S3)k+2 + 3{S7)k + 2lP(S6)k-2 + (P(S4Jk + 2 + + Pl38)k-2)P(S2(k+l + (P(Sl)k-2 + P()P(Sl)k-1+

+ (FfS)k- + P(S2)(S8)k-l3P(S5)(S3)k-2 +

-r F(S-)K + 2)P(S6)k+1 + (P(S8)k + 2 +

+ F(S (S2)(P(S5)k-: + P(S4)k-(S6)k-l + + (,k-2 + P(S6)(S3)(S7jk(P(SOk+2 +

+ )t + 2)P(S8)k+t + (P(S2)k + 2 + + (S4).

L 0

onr лов с - ния -е

CTЈfv ..

Soni(t;.

Si, Sj

лом т Sj(t),

разе.с ратсч. Esat i

СИГ -а

вег

наг- с. Sift), er .а определяет алгоритм построения .. чкого приемника цифровых сигна- ,епрерывной фазовой модуляцией на :елого гауссового шума. Для упрощепичесчой реализаций приемника силе с Ј сЬмируется. Опорные сигналы

i 1,4 представляют собой сигналы

j i-; 34 и синхронизированы с нача- ,ем- последовательности сигналов

i,o с помощью блока 1. В схеме - ir /сг окС ва корреляторы, об.,-.« поив ьо-кигелями 2-6 и интег- . С с глечиезют вычисление

оорел IJH/. с гнало э на зходе

, е з сигнзлоз. Энергии L/. -- 1,8, пдинакоьы, поэтому

/i, ,гг орииочальные логариф , eonoj.-Kb1 вероятностей сигналов ч.,,. / с ся

-i - J у

Som(t)dl, l 1,4,

где / --I P SO.

CiTrur KC ,,oe интегратора 7 пропорци- оиалз1- Z:, его пнверсия на выходе инвертора 11 пропорциональна ZG, аналогично для инте 8 . инвертора 12 , для мнте-;-зтора 9 , инвертора 13 Zi, и для К чсртооа 10 , инвертора 14 - Ze. Блоси 15 и 16 идентичны и вычисляют величи -.и типа

In(ez + ezj) - n(ez + eZm), , j, с, m

Наличие Элоков 17-20, 85 и 87, обеспе- 4MsaHjt4 /,x задержку на время Т, позволяет величины Z,(K+1), блоков 47,48, 68, 69, 96, 99, обеспечивающих задержку на 2Т, позволяет получить величины Zi(K), блоков 97 и 98, обеспечивающих задержки на ЗТ и 4Т С001°етственно, позволяет получить Zi(K-1) и Zi(K-2), который используется в при- ведекьо алгоритме.

Для обеспечения ьыччспенш. вал/мин nP(Sk 1) и lnF (Sk -1) прл./енчется следующее тождество:

. f Z| . 7- v Z, + Zj , In (e -be ) --;--L h

+ In 24n ch ( ).

Последовательно применяя данное тождество к приведенной системе, можно получить алгоритм, схема которого представлена н фиг. 1.

При синтезе алгоритма работу прмеи ника, минимизирующего полную ьероят ность ошибки, правило вынесения решения об информационном символе заключается в сравнении разности логарифмов апостериорных вероятностей эшго символа с г,и рогом

In P(Sk 1) - In P(Sk

Sk 1

-1) 0

Sk -l

Блоки 35-38, 56-59 идентичны обеспечивают вычисления априорных вероятно стей для сигналов Sj(t), jH ,8 путем учета згчда возможных предшествующих сигналов Sj(t-T), j 1,8.

Таким образом в результате рзбсть чо алгоритму (1) с учетом логарифмирования и применения тождест на на выходе преобрази вателя 11 вычисляется вепичина, пропорциональная логарифму априорной вероятюст приема сигнала, соответствующе с. перадаче 1, а на выходе преобразователей 1 :3 образуется величина, пропорциональная лсгариф му априорной вероятности приема си нала соответствующего передаче -1. На выходе полусумматора 76 вычисляется аегичина пропорциональная логарифму условной вероятности приема сигнала Sj(t}, соответству ющего передаче -I а на выходе полусумматора 55 вычисляется пропорциональная логарифму условной вероятности принятия сигнала Sj(t), соо ветст вующего передаче +1. Проходя через инвертор 115 и суммируясь в сумматоре 116 с логарифмом условной вероятности приема +1, вычисляется логарифмов условной вероятности принятия -И или - соответственно. Суммируясь г. выходов И вычитания на выходе сумматора 116, вычис ляется величина, равная разносил логарифмов апостериорной вероятности поие.ма н 1 или-1. Положительный или отрицательный знак разности, определяемый с поиощью решающего блока 117, соотоетстаует сг:у чаю, когда апостериорная вероятность сиг нала Si(t) больше (меньше) апостериорной вероятности сигнала ) Преобразоватьли сигнала представляю г собой устройства с переде.точной функцией вида

y{x} ln ch (х}- In

er

0

5

0

5

E°

5

O

ц

Формула изобретения 1, Устройство для приема цифровых сигналов с непрерывной азолэй модуляцией, содержащее первый, С,срой, третий, четвертый перемножите. первый, второй, третий t-s четвертый интегратор -, генератор опорных сигналов, блок фззовой гатоподстройки пасущей и тактовой частот, первый, второй, третий, четвертый инверторы, первый - четырнадцатый jy Maropbi, первый вычмтатель, первый - шестой преобразователи сигнала, первый - четвертуй блоки задержки, первый, второй блоки нелинейного суммирования, решающий блок, выход которого язпяетсл ЕЬ ХОДОМ устройства, первые входы перечислителей являются входом устройства, выходы перемножителей соединены с сигнальными входами соответствующих интеграторов, входы сброса которых соединены с первым выходом бло- лэ фазово автопсдстройки несущей и boi/ s втогс1 пэрепнояс/иелей соедине-iL оотвг гвенно с первым, вторым,трс ми . четвертым рь-хо/.згл генератора ОЮиг ЫХ , 1ГЬЗЛОВ, ХрОб.ЧОД

которого опе,и,-еч с выхода:;i блока фазовой SEncrio.ic фойкч несущей щ тактосой чз- стот, при згсм выходы всеч ИгРьгратороа соединечч с:эо -аетственно с ехолами первого вюрог-j, третьего и четвэрго-о иньер- торов, о г, 1 -. ъ ю ui e e с F тем, что, с целью повышения помехоустойчивости устройства, Ева,осгш пятнадцатый - двадцать восьмой сумма оры, - четырнадцатый блоки з&реря, первый-девятый полчсуп- маторь, лрЕлй - восьмой зьнисллтели ап- вероя носн-: седьмой - десять1 пресбрсзовагелИ сичагз пятый - восьмой мнперторь, второй дглдчтгь третий вычи- тателм, первый - четвертый вычислители, причем выход первого чнтеграгсра соединен с входом первого 5 ici а задержки, первым входом песво О блока нелинейного суммирования, первым и вторым входами первого вычисш тепя апр ооной аероячмп- сти, nepuh -i ахс ДОГ одиннадцато- о Зэшята- |вля, первым четвертого, первым входом пятого ч гесвым и вторым входами eocbfvfOfO пычмслигсл13 априорной сзроятно- оти, первым и вторые входами первого вь1- числмтеля, первым входом тринадцатого сур матора, первым -эходсм седьмого полусумматора, первым входом четвертого вычислителя, первым входом девятнадцатого сумматора и первыми входами восьмого и девятого полусумматоров а выход первого инвертора соединен с первым входом, второго блока нелинейного суммирования, с первым входом второго вычислитепя априорной вероятности, первым входом двенадцатого вычитателя, первым и вторым входами третьего, первым и вторым входами шестого и первым входом седьмого вычислителя априорной вероятности, а выход второго интегратора соединен с входом второго блока задержки, с вторым входом первого блока нелинейного суммирования, третьим входом первого, вторым входом второго, вторым входом четвертого и вторым входом пятого вычислителя априорной вероятности, первым входом семнадцатого вычитателя, вторым входом седьмого и третьим входом восьмого вычислителей априорной вероятности, вторым входом седьмого полусумматора, первым входом третьего вычислителя и вторым входом девятого полусумматора и первым входом

двадцатого сумматора, а выход второго инвертора соединен с вторым входом второго блока нелинейного суммирования, с третьим входом второго, третьим входом третьего, третьим входом четвертого, третьим входом пятого и третьим входом шестого вычислителей априорной вероятности, первым входом восемнадцатого вычислителя, третьим входом седьмого вычислителя априорной вероятности, первым входом второго вычислителя, первым входом четырнадцатого сумматора и вторым входом восьмого полусумматора и вторым входом третьего вычислителя, причем выход третьего интегратора соединен с входом третьего блока задержки, третьим входом первого блока нелинейного суммирования, четвертым входом второго, четвертым входом третьего, четвертым входом четвертого, четвертым входом пятого, четвертым входом шестого и четвертым входом седьмого вычислителей априорной вероятности, вторым входом восемнадцатого вычитателя, вторым входом второго вычислителя, вторым входом тринадцатого сумматора, третьим входом седьмого полусумматора, третьим входом третьего и вторым входом четвертого вычислителя, третьим входом восьмого полусумматора и вторым входом двадцатого сумматора, а выход третьего инвертора соединен с третьим входом второго , блока нелинейного суммирования, четвертым входом первого, пятым входом второго, пятым входом четвертого и пятым входом пятого вычислителей априорной вероятности, вторым входом семнадцатого вычитателя, пятым входом седьмого и четвертым входом восьмого вычислителей априорной вероятности и третьим входом девятого полусумматора, а выход четвертого интегратора соединен с входом четвертого блока задержки, четвертым входом первого блока нелинейного суммирования, шестым входом второго вычислителя априорной вероятности, вторым входом двенадцатого

0 вычитателя, пятым и шестым входами третьего, пятым и шестым входами шестого и пятым входом седьмого вычислителей априорной вероятности, третьим входом второго вычислителя, четвертым входом седьмого

5 полусумматора, вторым входом четырнадцатого сумматора, вторым входом девятнадцатого сумматора и четвертым входом восьмого полусумматора, а выход четвертого инвертора соединен с четвертым входом

0 второго блока нелинейного суммирования, пятым и шестым входами первого вычислителя априорной вероятности, вторым входом одиннадцатого вычитателя, шестым входом четвертого, шестым входом пятого и

5 пятым и шестым входами восьмого вычислителей априорной вероятности, третьим входом первого и третьим входом четвертого вычислителей и четвертым входом девятого полусумматора, а выходы первого и четвер0 того блоков задержки соединены соответст- венно с первыми входами первого и четвертого сумматоров и первыми входами второго и третьего вычитателей, выход первого блока нелинейного суммирования сое5 динен с первыми входами второго и третьего сумматоров, вторые входы которых соединены с выходами второго и третьего блоков задержки соответственно, причем выходы второго и третьего сумматоров сое0 динены соответственно с вторыми входами второго и третьего вычитателей, а вторые входы первого и четвертого сумматоров соединены с выходом второго блока нелинейного суммирования, причем первые входы

5 первого четвертого вычитателей соединены соответственно с выходами первого и четвертого сумматоров, а вторые входы первого и четвертого вычитателей соединены с выходами второго и третьего блоков задер0 жки соответственно, причем выходы второго и третьего вычитателей через второй и третий преобразователи сигнала соединены соответственное первыми входами пятого и шестого вычитателей, выходы которых

5-соединены соответственно с первыми входами пятнадцатого и шестнадцатого сумматоров, а выходы первого и четвертого вычитателей через первый и четвертый преобразователи сигнала соединены с вторыми входами пятого и шестого вычитателей, а

выход первого преобразователя сигнала соединен с первым входом седьмого сумматора, выход второго преобразователя сигнала соединен с четвертым еходом восьмого сумматора, выход третьего преобразователя сигнала соединен счетвершм входом одиннадцатого сумматора, а зыход четвертого преобразователя сигнала соединен с первым входом двенадцатого сумматора, первые выходы первого, .четвертого, пятого и восьмого вычислителей априорной eepoav- ности соединены соотаэтственно с первыми входами седьмого вычитэгеля, девятого вычитателя, тринадцатого вычитателя и пятнадцатого вычитателя, а также соответ- ственно с первыми входами первого полусумматора, второго полусумматора, четвертого и пятого полусумматоров, вторые входы которых соединены соответственно с первыми выходами второго, третьего, шестого и седьмого вычислителей априорной вероятности соответственно, вторые выходы второго, третьего, шестого и седьмого вычислителей априорной вероятности соединены соответственное первыми входами восьмого, десятого, четырнадцатого и шестнадцатого зычитателей, вторые входы которых соединены соответственно с вторыми выходами первого, четвертого, пятого и восьмого вычислителей априорной вероятности, выходы восьмого, десятого, четырнадцатого и шестнадцатого вычитате- лей через пятый, шестой, девятый и десятый сумматоры соответственно соединены с входами пятого, шестого, седьмого и вось- мого преобразователей сигнала, выходы которых соединены соответственно с вторыми входами седьмого л восьмого сумматоров, выходы которых соединены с первым л вторым входами третьего полусумматора и со- ответственно с вторыми входами одиннадцатого и двенадцатого сумматоров, выходы которых соединены соответственно с входами шестого гюпусуммэтора, причем выход одиннадцатого вычитателя через пя тый блок задержки соединен с вторым входом пятого сумматора, а выход двенадцатого вычмтателя через шестой блок задержки соединен с вторым входом шестого сумматора, а выход семнадцатого вычитателя через седьмой блок задержки соединен с вторым входом девятого сумматора, выход восемнадцатого вычитатепя через восьмой блок задержки соединен с вторым входом десятого сумматора, причем выходы первого, второго и четвертого и пятого полусумматоров соединены соответственно с третьими входами седьмого, восьмого, одиннадцатого и двенадцатого сумматоров соответственно а выходы седьмого, девятого, тринадцатого и пятнадцатого вычитагелей соединен LS соответп венно с первыми входами двадцать первого и двадцать третьего и соответственно двадцать второго и двадцать четвертого сумматоров, причем первые еыходы второго м третьего, в также шестого и седьмого вычислителей априорной вероятности соединены соответственно с четвертым и пятым входами второго вычислителя л соответственно четвертым и пятым входами четвертого вычислителя, а первые аиходы первого л четвертого, а также пятого и восьмого вычислителей априорной взроятности соединены соответственно с чертвертым и пятым входами второго и третьего вычислителей, а выходы третье о и шестого полусумматоров через восьмой инвертор соединены соответственно с первым и вторым входами двадцать седьмого сумматора выход которого соединен с входом решающего блока, причем выходы первого и второго вычислителей соединены с первым и вторым входами девятнадцатого вычитате- ля, а выходы третьего v четвертого вычислителей соединены соответственно с первым и вторым входами двадцатого вычитателя, а выход седьмого лопусумматора соединен с вторыми входа-ми пятнадцатого и шестнадцатого сум /лторов, третьи входы которых соединены ссо ветственно с девятым и десятым блокамм задержкм вход которого соединен соответственно с ыхсдамь тринадцатого и четырнадцатого суммато- ров, а выходы пятнадцатого м шестнадцатого сумматоров соединены с первыми входами семнадцатого и восемнадцатого сумматоров, вторые входы которых соединены соответственно с выходами девятнадцатого и двадцатого вычктателей, а выходы соединены с первыми входами двадцать первого и двадцать второго вычитателей соответственно, причем выходы девятнадцатого и двадцатого сумматоров через одиннадцатый и четырнадцатый блоки задержки соединены с вторыми входами двадцать первого и двадцать второго сумматоров, выходы одиннадцатого и че- тырнадиэтсго блоков задержки соответственно через пятый и шестой инверторы Воединены с вторыми входами двадцать третьего и двадцать четвертого сумматоров, третьи входы которых соединены с выходом шестого инвертора, вход которого соединен с выходом двадцать восьмого сумматора, а выходы соединены с первыми входами двадцать седьмого и двадцать восьмого сумматоров соответстаенно, вторые входы которых соединены соответственно с выходами двадцать первого м двадцать второго

вычитателей а выходы соответствзн- но девятый и десятой бло-си (ен нэциой обработки соединены с первым ,ч вторым входами двадцать третьего вичитателя, выход которого соединен „ третьим входом двадцать пятого сумматора, а выходы восьмого и девятого полусумматоров через двенадцатый и тринадцатый блоки задержки соответственно соединены с первым м вторым входами двадцать шестого сумматора, выход двадцать восьмого сумматора соединен с третьими входами двадцать первого и двадцать второго сумматоров, выходы которых соответственно соединены с вторыми входами двадцать первого и двадцать второго вы мтатепей.

2. Устройство по п. 1, о т л и ч а ю щ е е- с я тем, ч го блок вычигл ия приорной вероятности содержит первый, блоки вычисления нелинейного суммирования. первый - четвертый блогк задержки, полусумматор, вы«итатель, преобоазователь сигнала и первый - третий сумматоры, приот20

чем t , блоков вычисления нелинейного сум1ч ,. иеаш Я являются соответственно вторым, 1ретьим, четвертым и пятым входами бло1а вычисления априорной вероягности, о в.оды первого и второго блоков задерхки являются первым и шестым входами б- Югса вычисления априорной вероятности, а нь ходы третьего сумматора и блока нелинеГ обработки являются первым и

вторым входами блока вычисления априорной вероятности,а выходы первого и второго блоков вычисления нелинейного суммирования соответственно через третий и четвзс ьй блоки задержки соединены с

первьп i i входами первого и второго сумматоров в го ые входы которых соединены со- отвегст е -.но с выходами первого и второго блоксг зчзержки, а выходы сумматоров соединены соответственно с входами полусуммаюра и вычитателя, выход блока нелинейно обработки соединен с первым входом трр riero сумматора, второй вход которого соединен с выходом полусумматора

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для приема двоичных сигналов с непрерывной фазовой модуляцией | 1989 |

|

SU1753617A1 |

| УСТРОЙСТВО ДЛЯ РАСЧЕТА РАЗМЕРОВ ОБЛАСТИ ВЕРОЯТНОГО НАХОЖДЕНИЯ ЦЕЛИ | 2014 |

|

RU2554534C1 |

| Устройство для контроля аппаратуры управления электростанций | 1983 |

|

SU1201799A1 |

| Устройство для приема двоичных сигналов | 1988 |

|

SU1573551A1 |

| ПРИЕМНИК ДЛЯ РЕЛЬСОВОЙ ЦЕПИ | 1994 |

|

RU2083410C1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ВЕРОЯТНОСТИ ОБНАРУЖЕНИЯ ВОЗДУШНЫХ ЦЕЛЕЙ | 2000 |

|

RU2176104C1 |

| ТОПЛИВОМЕР | 1991 |

|

RU2019794C1 |

| Устройство для декодирования с исправлением ошибок | 1990 |

|

SU1797165A1 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЗНАЧЕНИЯ ХАРАКТЕРИСТИК ГОТОВНОСТИ ИЗДЕЛИЯ К ПРИМЕНЕНИЮ | 2014 |

|

RU2580099C2 |

| УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ЭКСПЛУАТАЦИОННО-ТЕХНИЧЕСКИХ ХАРАКТЕРИСТИК ИЗДЕЛИЯ ПРИ ОПТИМАЛЬНОМ ПЕРИОДЕ ЕГО ТЕХНИЧЕСКОГО ОБСЛУЖИВАНИЯ | 2014 |

|

RU2553077C1 |

Изобретение относится к радиотехнике и может использоваться для приема и передачи информации. Цель изобретения - повышение помехоустойчивости. Устройство для приема цифровых сигналов с непрерывной фазовой модуляцией содержит блок 1 фазовой автоподстройки несущей и тактоК 35, М, 38, 35.Н.ЗВ,5Б.59,7,80,93 вой частот, генератор 2 опорных сигналов, перемножители 3-6, интеграторы 7-10, инверторы 11-14, блоки 15 и 16 нелинейного суммирования, блоки 17-20 задержки, сумматоры 21-24, вычитатель 25, преобразователи 29-32 сигнала, пятый-четырнадцатый сумматоры, пятый, шестой преобразователи сигнала, решающий блок. Цель достигается введением пятнадцатого-двадцать восьмого сумматоров, пятого-четырнадца- того блоков задержки, девяти полусумматоров, восьми вычислителей априорной вероятности, седьмого-десятого преобразователей сигнала, пятого-восьмого инверторов, второго-двадцать третьего вычитателей, первого-четвертого вычислителей. Устройство по п. 2 отличается выполнением блока вычисления априорной вероятности. 1 з.п,ф-лы, 6 ил. 56,59,77,80.81,,33,32 (Л С 56,58.53.82.35.36.38УЛЩ 57.S8.78M3S,37 i2,83,34.3Z 32$В.57.58№.36.37.38.78.8Щ о Ч) о ю 32,56,57,58,63,38,37,73.32.18. 35,36.38. 80.8J.82.95 56.58.53.93 .

Фм. 2

Г

08

NT

Г Itato

§01У

1110691

От 55

Фиг. 5

| Устройство для приема двоичных сигналов | 1988 |

|

SU1573551A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-11-07—Публикация

1989-03-07—Подача