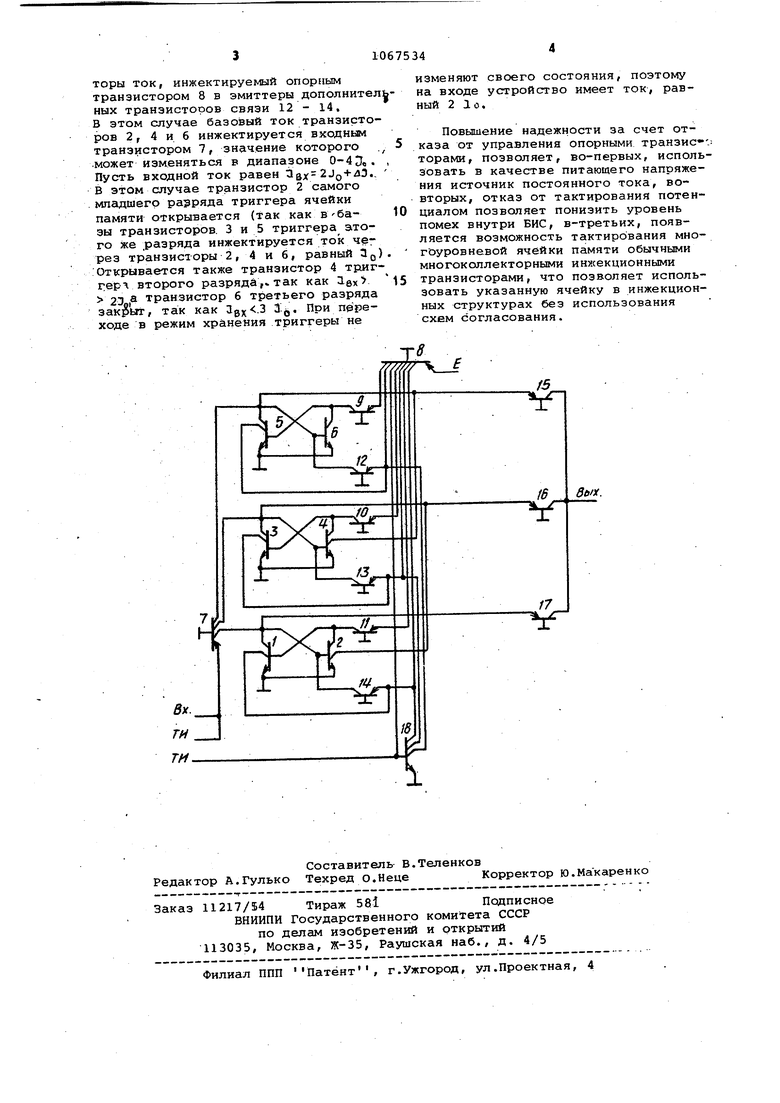

Изобретение относится к импульсной технике и может быть использов ано, например, для построения многоуровневых структур. Известна схема инжекционного запоминающего элемента, содержащая триггер, выполненный на транзистоpax с непосредственными связями, транзисторы записи и считывания, а также источники тока, выходы КОТОРЫХ подключены к соответствующим базам транзисторов П . . Основным недостатком данного устройства являются низкие, возможности, обусловленные запоминанием лишг;, двух уровневого сигнала, Иаи-более близкой к изобретению является мно.гоуровневая ячейка памяти ,содержащая элементы связи, входной элемент, выходные и опорные элементы, выполненные на р-п-р-транзисторах, блокировочный элемент и триггеры, выполненные на п-р-п-транзисто рах, причем первыевыходы .триггеров подключены к соответствующим коллекторам элементов связи, эмиттеры кото рых подключены к коллекторам соответ ствующих опорных элементов, база блокировочного транзистора является, управляющим входом ячейки памяти и подключена к соответствующему входу опорного транзистора 2. Недостатком этого устройства является его низкая надежность, которая обусловлена наличием в схеме двух шин питания. Использование различных шин питания для-записи.и хранения может привести к неоднозначности входного и выходного тока . Цель изобретения - повышение надежности устройства за счет снижения требования к амплитуде и фронтам так тового импульса. Поставленная цель достигается тем что в устройство, содержащее элементы связи, входной элемент, выходные элементы, опорные и блокировочные элементы, выполненные на p-hirp-TpaHзисторах, и триггеры,- первые выходы которых подключены кколлектору р-п-р-транзистора соответствующих элементов связи, эмиттеры которых подключены к соответствуЬщим коллекторам опорного элемента, база р-р-р-транзистора блокировочного эле мента является управляющим входом ячейки памяти и подключена к соответ ствующеьту коллектору р-п р-транзисто ра опорного элемента, коллекторы р-п-р-транзисторо выходных элементо являются выходом ячейки памяти, эмит теры р-п-р-транзисторов выходных эле ментов подключены к первому входу соответствующего триггера, эмиттер р-п-р-транзистора блокировочного эле мента и база р-п-р-транзистора опорного элемента подключены к оби1ей шине, причем эмиттер р-п-р-транзистора входного элемента йвляе -ся информационным входом ячейки памяти, введены дополнительные элементы связи, выполненные на р-п-р-транзисторах, коллекторы которых подключены к вторым выходам соответствующих триггеров, базы - к общей щине, а эмиттеры - к соответствующим коллекто Згм р-п-р-транзисторов опорного и блокировочного элементов, вторые входы триггеров подключены к соответствующим коллекторам р-п-р-транзистора блокировочного элемента, третий выход каждого триггера подключен к первому входу последующего TpHrrej)a, эмиттер р -( -р-транзистора входного элемента подключен к тактовой шине, На чертеже приведена принципиальная электрическая схема четырехуровневой ячейки памяти. Устройство содержит соответствен.но первые и вторые п-р-п-транзисторы триггеров 1 ,- 6, входной р-п-р-транзистор 7,-опорный транзистор 8, р-п-р-транзисторы связи 9 - 11, до полнительные р-п-р-транзисторы связи 12 - 14, выходные р-п-р-транзисторы 15 - 17, блокировочный р-п-р-транзистор 18. Многоуровневая ячейка памяти ра.ботает в режиме записи и в режиме хранения. В режиме хранения на тактовую щину (ТИ) подается сигнал низкого логического уровня, что приводит к зат иранию входного 7 и блокировочного 18 транзисторов-. Базовые токи транзисторов триггера подаются через транзисторы связи 9-14, причем значения токов идентичны/ поэтому состояние триггеров не изменяются, В зависимости от состояния триггеров через выходные транзисторы 15 - 17 инжектируется или не инжектируется значение в.ходного тока. Если для определенности считать, что транзистор 1 первого триггера открыт, второго 3 - закрыт, а третьего 5 открыт, то выходной ток устройства равен значению 2 З , в противном случае, т.е. первые транзисторы первого и третьего триггеров закрыты, а второго - открыт, выходной ток равен величине 3 Ij. В базы транзисторов триггера самого младшего разряда подаются через транзистор 9 (10,11) и дополнительный транзист. тор 12 (13,14) токи, равные 1 3, в базы транзисторов триггера второго разряда - 2 Зд, третьего - 3 Зд, . п-го - h3 о. Задание требуемого значения тока можно измерит.ь путем изменения геометрии базовых/р-областей инжектора; и переинжектора. В режиме записи на Тактовую шину подается второй логический уровень. Б этом случае.транзистор 18 открывается и отбирает через свои коллекторы ток, инжектируемый onoptibiM транзистором 8 в эмиттеры дополнительных транзисторов связи 12 - 14. В этом случае базовый ток транзисторов 2, 4 и 6 инжектируется входным транзистором 7, значение которого ., 5 может изменяться в диапазоне 0-4JX. , Пусть входной ток равен Зах 2Jo+d3., В этом случае транзистор 2 самого 1 шадшегр разряда триггера ячейки памяти открывается (так как Вба- 10 зы транзисторов. 3 и 5 триггера этого же .разряда инжектируется ток через транзисторы 2, 4 и б, равный Зд). Открывается также транзистор 4 триггер второго разряди, так как lex 15 23 ,а транзистор 6 третьего разряда закрыт, так как Jjj. При переходе в режим хранения триггеры не

изменяют своего состояния, поэтому на входе устройство имеет ток, равный 2 1 о.

Повышение надежности за счет отказа от управления опорными транзис торами, позволяет, во-первых, использовать в качестве питающего напряжения источник постоянного тока, вовторых, отказ от тактирования потенциалом позволяет понизить уровень помех внутри БИС, в-третьих, появляется возможность тактирования многоуровневой ячейки памяти обычными многоколлекторными инхсекционными транзисторами, что позволяет использовать указанную ячейку в инжекционных структурах без использования схем согласования.

dOfX.

| название | год | авторы | номер документа |

|---|---|---|---|

| Ячейка памяти | 1982 |

|

SU1140165A1 |

| Ячейка памяти | 1983 |

|

SU1132344A1 |

| Ячейка памяти | 1977 |

|

SU705523A1 |

| Интегральный четырехзначный D-триггер | 1986 |

|

SU1338012A1 |

| Тактируемый JK-триггер И @ Л-типа | 1987 |

|

SU1422367A1 |

| Регистр сдвига | 1982 |

|

SU1136217A1 |

| Входной транслятор И @ Л-типа | 1984 |

|

SU1202049A1 |

| Тактируемый @ -триггер @ -типа | 1985 |

|

SU1275738A1 |

| Элемент памяти для регистра сдвига | 1979 |

|

SU847373A1 |

| Инжекционный динамический элемент | 1980 |

|

SU953731A1 |

МНОГОУРОВНЕВАЯ ЯЧЕЙКА ПАМЯТИ, содержащая элементы связи/ входной элемент, выходые элементы,опорный и блокировочные элементы, выполненные на р-п-р-транзисторах, и триггеры, первые выходы которых подключены к коллектору р-п-р-транзистора соответствующих элементов связи, эмиттеры которых подключены к соответствующим коллекторам опорного элемента, база р-п-р-транзистора блокировочного элемента является управляющим входом ячейки памяти и подключена к соответствующему коллектору р-п-р-транзистора опорного элемента, коллекторы р-п-р-транзисторов выходных элементов являются выходом ячейки памяти, эмиттеры р-п-рттранэисторов выходных элементов подключены к первому входу соответствующего триггера, эмиттер р-п-р-транзистора блокировочного элемента и база р-п-ртранзистора опорного элемента подключены к общей шине, причем эмиттер р-п-р-транзистора входного элемента является информационным входом ячейки, памяти, отл. ичающаяся тем, что, с целью повышения надежности ячейки за счет снижения требований к амплитуде и фронтам тактовы в импульсов, в неё введены допол нительные элементы связи, выполненные на р-п-р-т.ранзисторах, коллекторы которых подключены к вторым вы- § ходам соответствующих триггеров, (Л базы - к общей шине, а эмиттеры к соответствующим коллекторам p-h-p.транзисторов опорного и блокировочного элементов, вторые входы триггеров подключены к соответствующим коллекторам р-Н-р-транзистора блокировочного элемента, третий выход каждого триггера подключен к первому входу последукицего триггера, о эмиттер р-п-р-транзистора входного элемента подключен к тактовой шине. сд со

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Инжекционный запоминающий элемент | 1976 |

|

SU615541A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Ячейка памяти | 1977 |

|

SU705523A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

Авторы

Даты

1984-01-15—Публикация

1980-05-22—Подача