ИЛИ блока управления, выходы которого соединены с разрядными выходами счетчика блока управления и вторым управляющим входом демультиплексора, выходы элементов И второй группы соединены с информационным входом буf

Изобретение относится к вычислительной технике и может быть использовано при делении и -разрядных чисел.

Цель изобретения - повышение быстродействия устройства.

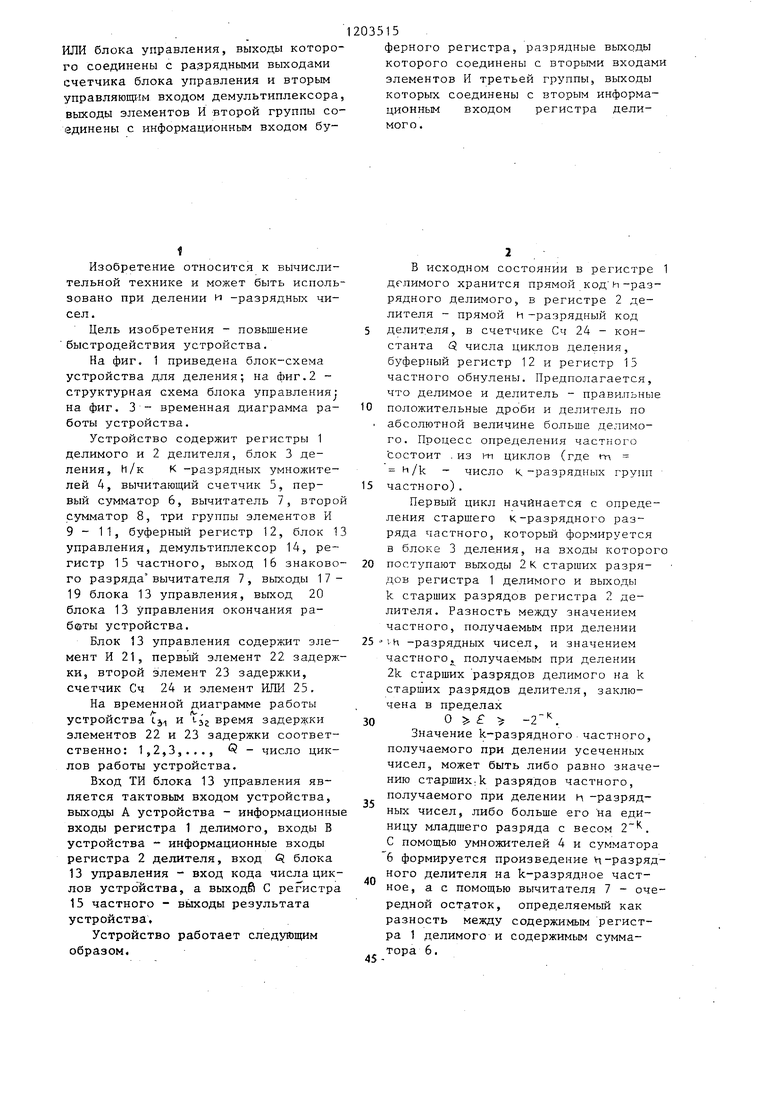

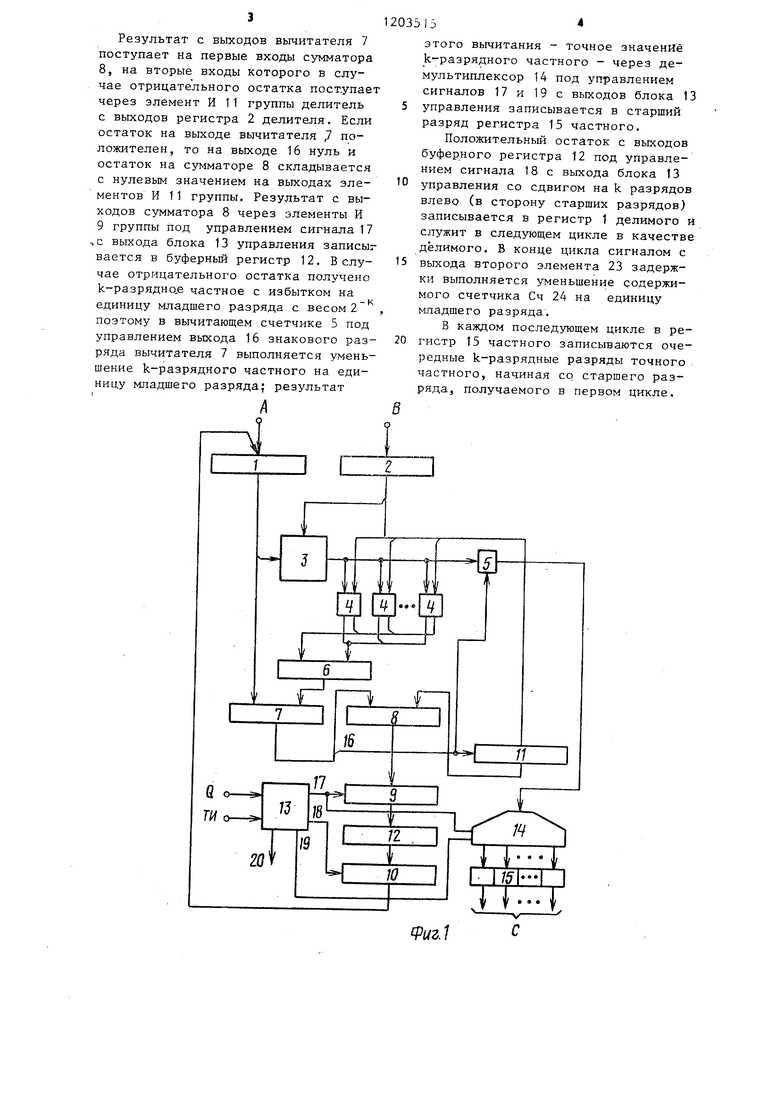

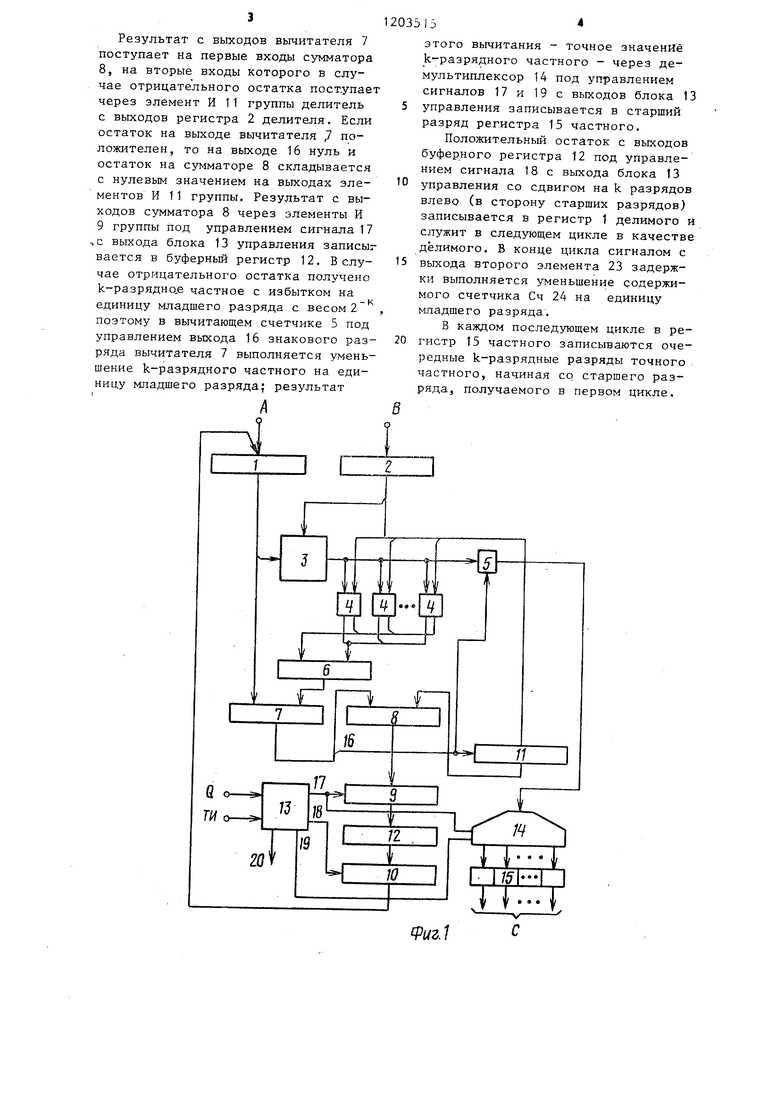

На фиг. 1 приведена блок-схема устройства для деления; на фиг.2 - структурная схема блока управления на фиг. 3 - временная диаграмма работы устройства.

Устройство содержит регистры 1 делимого и 2 делителя, блок 3 деления, И/к К -разрядных умножителей 4, вычитающий счетчик 5, первый сумматор 6, вычитатель 7, второ сумматор 8, три группы элементов И 9-11, буферный регистр 12, блок 1 управления, демультиплексор 14, регистр 15 частного, выход 16 знакового разряда вычитателя 7, выходы 17 - 19 блока 13 управления, выход 20 блока 13 управления окончания работы устройства.

Блок 13 управления содержит элемент И 21, первый элемент 22 задержки, второй элемент 23 задержки, счетчик Сч 24 и элемент ИЛИ 25.

На временной диаграмме работы

л А .

устройства 1.J1 и tjj время задержки элементов 22 и 23 задержки соответственно: 1,2,3,..., Q - число циклов работы устройства.

Вход ТИ блока 13 упр-авления является тактовым входом устройства, выходь А устройства - информационны входы регистра 1 делимого, входы В устройства - информационные входы регистра 2 делителя, вход Q блока 13 управления - вход кода числа циклов устройства, а выходи С регистра 15 частного - выходы результата устройства.

Устройство работает следующим образом.

ферного регистра, разрядные выходы которого соединены с вторыми входами элементов И третьей группы, выходы которых соединены с вторым информационным входом регистра делимого .

В исходном состоянии в регистре 1 делимого хранится прямой код h-разрядного делимого, в регистре 2 делителя - прямой h-разрядный код

делителя, в счетчике Сч 24 - константа Q числа циклов деления, буферный регистр 12 и регистр 15 частного обнулены. Предполагается, что делимое и делитель - правильные

положительные дроби и делитель по абсолютной величине больше делимого. Процесс определения частггого состоит . из и-1 циклов (где ТА Н/k - число К-разрядных групп

частного).

Первый цикл начинается с определения старшего к-разрядного разряда частного, который формируется в блоке 3 деления, на входы которого

поступают выходы 2 К старших разрядов регистра 1 делимого и выходы k старших разрядов регистра 2 делителя. Разность между значением частного, получаемым при делении

I h -разрядных чисел, и значением частного,, получаемым при делении 2k старших разрядов делимого на k старших разрядов делителя, заключена в пределах

О f -2.

Значение k-разрядного частного, получаемого при делении усеченных чисел, может быть либо равно значению старших;k разрядов частного, получаемого при делении h -разрядных чисел, либо больше его на единицу младшего разряда с весом 2. С помощью умножителей 4 и сумматора 6 формируется произведение h-разрядного делителя на k-разрядное частное, а с помощью вычитателя 7 - очередной остаток, определяемый как разность между содержимьм регистра 1 делимого и содержимым сумма- тора 6.

Результат с выходов вычитателя 7 поступает на первые входы сумматора 8, на вторые входы которого в случае отрицательного остатка пост.упает через элемент И 11 группы делитель с выходов регистра 2 делителя. Если остаток на выходе вычитателя ,7 положителен, то на выходе 16 нуль и остаток на сумматоре 8 складывается с нулевым значением на выходах элементов И 11 группы. Результат с выходов сумматора 8 через элементы И 9 группы под управлением сигнала 17 ., с выхода блока 13 управления записыг вается в буферный регистр 12. В случае отрицательного остатка получено k-paзpяднo,e частное с избытком на единицу младшего разряда с весом 2 поэтому в вычитающем счетчике 5 под управлением выхода 16 знакового разряда вычитателя 7 выполняется уменьшение k-разрядного частного на единицу младшего разряда; результат

I -к

а ет и я 7г од зьк

10

этого вычитания - точное значение k-разрядного частного - через де- мультиплексор 14 под управлением сигналов 17 и 19 с выходов блока 13 управления записывается в старший разряд регистра 15 частного.

Положительный остаток с выходов буферного регистра 12 под управлением сигнала 18 с выхода блока 13 управления со сдвигом на k разрядов влево (в сторону старших разрядов) записывается в регистр 1 делимого и служит в следующем цикле в качестве делимого. В конце цикла сигналом с

15 выхода второго элемента 23 задержки выполняется уменьшение содержимого счетчика Сч 24 на единицу младшего разряда.

В каждом последующем цикле в ре20 гистр 15 частного записываются очередные k-разрядные разряды точного частного, начиная со старшего разряда, получаемого в первом цикле.

В

22

М J7

э

/f

{;

г

t

25

I

20Редактор В Петраш

Составитель Е.Захарчекко

Техред И.Асталош .. Корректор А.Обручар

Заказ 8417/51

Тираж 709Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.4/5

Филиал ППП Патент, г.Ужгород, уд.Проектная, 4

20

Фиг. 2

Фиг. 5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1985 |

|

SU1265763A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для деления | 1989 |

|

SU1709301A1 |

| Устройство для деления | 1986 |

|

SU1425657A1 |

| Устройство для умножения | 1986 |

|

SU1432506A1 |

| Устройство для деления | 1986 |

|

SU1325467A1 |

| Устройство для деления | 1988 |

|

SU1541596A1 |

| Устройство для деления | 1985 |

|

SU1357946A1 |

| Устройство для деления | 1984 |

|

SU1249551A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления чисел | 1980 |

|

SU857977A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-01-07—Публикация

1984-07-19—Подача