| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для деления | 1989 |

|

SU1767497A1 |

| Устройство для деления | 1990 |

|

SU1709352A1 |

| Устройство для деления | 1989 |

|

SU1619255A1 |

| Устройство для деления | 1988 |

|

SU1541596A1 |

| Устройство для деления чисел | 1988 |

|

SU1580353A1 |

| Устройство для деления | 1990 |

|

SU1783521A1 |

| Устройство для деления | 1990 |

|

SU1783522A1 |

| Устройство для деления | 1988 |

|

SU1520510A1 |

| Устройство для деления чисел | 1985 |

|

SU1429109A1 |

| Устройство для деления чисел | 1985 |

|

SU1247862A1 |

Изобретение- относится к области вычислительной техники и может быть использовано в универсальных специализированных ЭВМ для построения быстродействующих устройств деления чисел. Целью изобретения является упрощение устройства. Устройство содержит регистры 1-3 делимого, делителя и частного, блок 4 деления усеченных чисел, два узла 5. 6 коррекции частного, блок 7 умножения, два вычитэтеля 8. 9, сумматор-вычитатель 10. коммур)тор 11. блок 12 управления. 3 ил.

VI

О

ю оэ

о

Изобретение относится к вычислительной технику и может быть использовано в быстродействующих арифметических .устройствах для выполнения операции деления,

Цель изобретения -упрощение устройства.

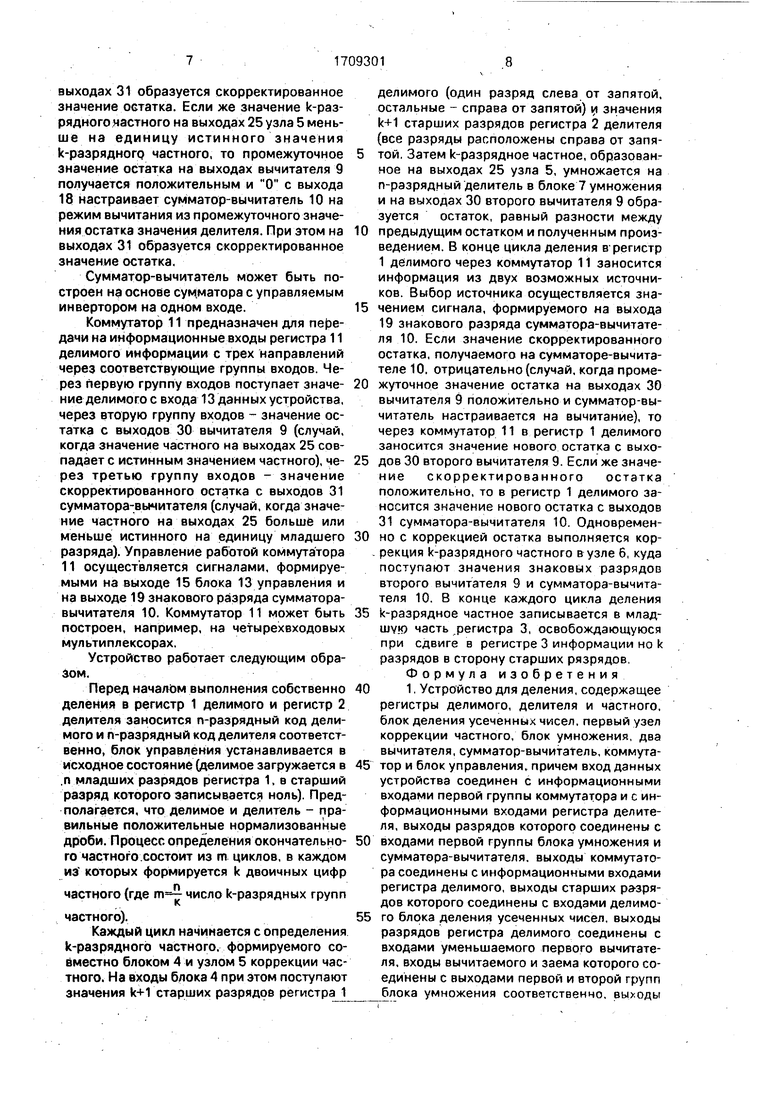

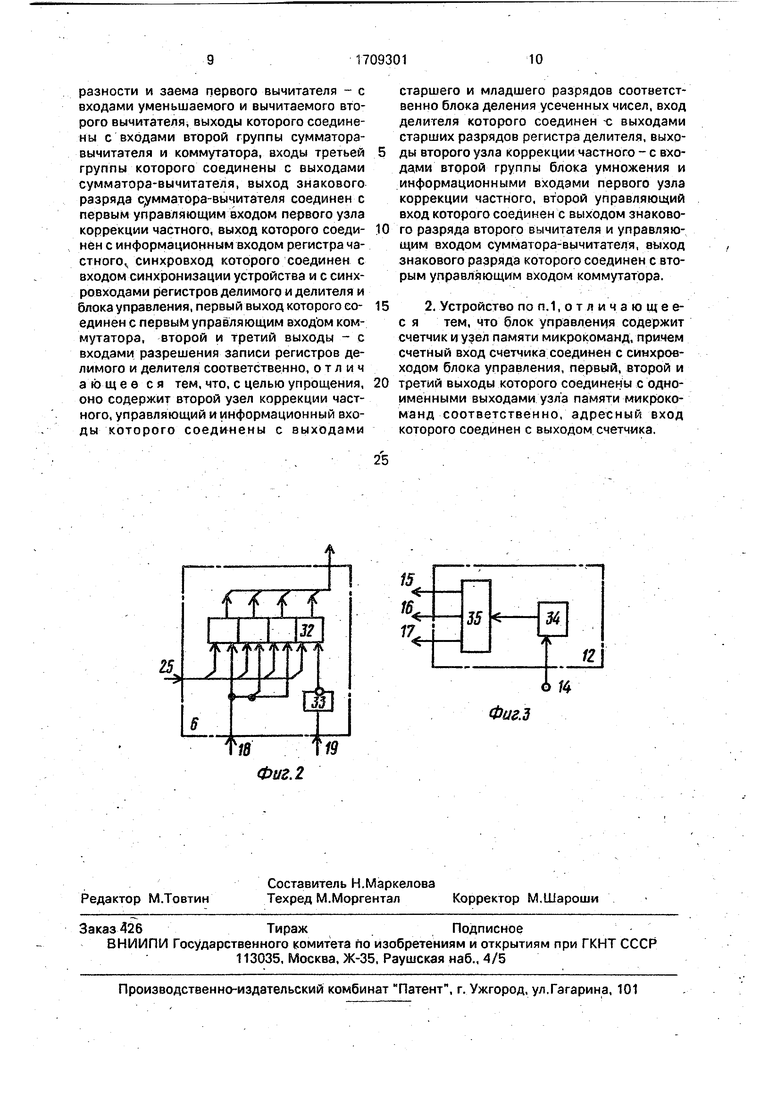

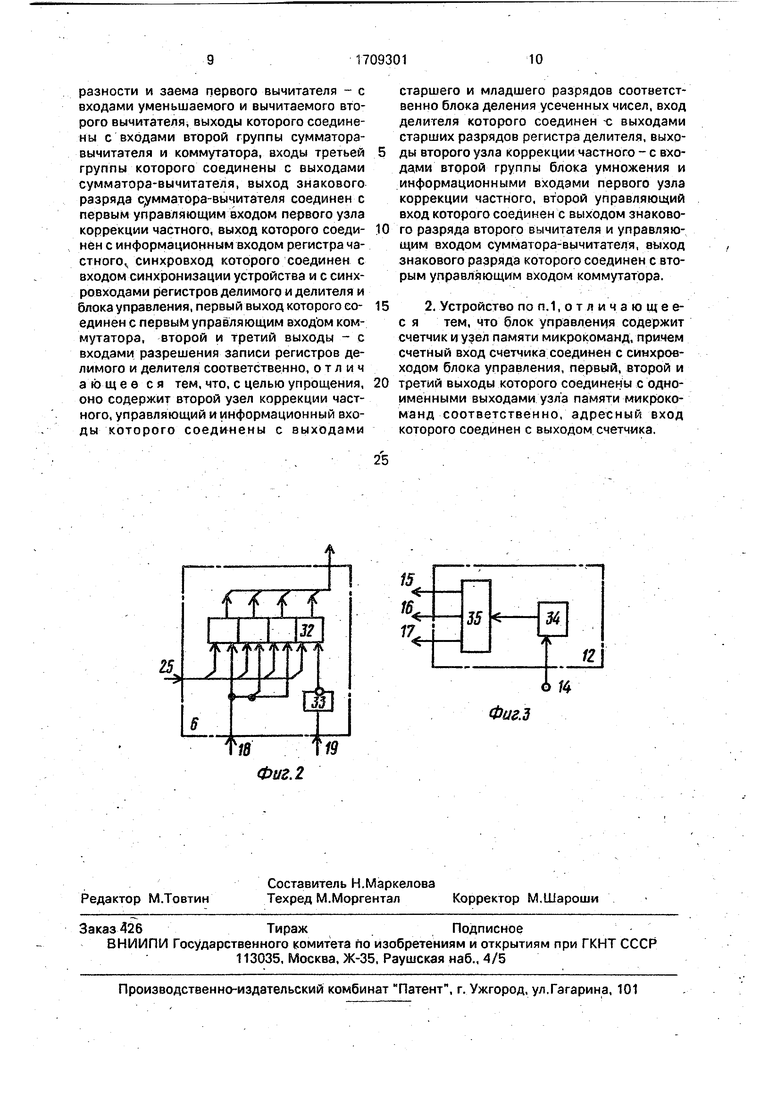

На фиг. 1 приведена структурная схема устройства; на фиг. 2 - функциональная схема первого узла коррекции частного для случая к 4; на фиг. 3 - функциональная схема блока управления.

Устройство для деления содержит (фиг.1) регистры 1, 2 и 3 соответственно делимого, делит,еля и частного, блок 4 деления усеченных чисел, второй 5 и первый 6 узлы коррекции частного, блок 7 умножения, первый 8 и второй 9 вычитатели, сумматор-вычитатель 10, коммутатор 11, блок 12 управления, вход 13 данных устройств, вход 14 синхронизации устройства, выходы 1517с первого по третий блока 12 управления, выход 18 знакового разряда второго вычитателя 9, выход 19 знакрвого разряда сумматора вычитателя 10, выходы 20 разрядов регистра 1 делимого, выходы 21 старших разрядов регистра 1 делимого, выходы 22 разрядов регистра, сумматора-вычитателя 10, выходы 23 старших разрядов регистра 2 делителя, выход24i старшего разрядам выходы 242 младших разрядов блока 4 деления усеченных чисел, выходы 25 второго узла 5 коррекции частного, выходы 26 первой и 27 второй группы блока 7 умножения, выходы 28 разности и быходы 29 заема первого вычитателя 8, выходы 30 второго вычитателя 9, выходы 31 сумматора-вычитателя 10. Первый узел б коррекции частного содержит (фиг.2) к-разрядный сумматор 32 и элемент НЕ 33. Блок 12 управления (фиг.3) может быть построен на базе счетчика 34 и узла 35 памяти микрокоманда.

Функциональное назначение и реализация оснбвных узлов и блоков устройства для деления.

Регистры 1 и 2 делимого и делителя соответственно предназначены для временного хранения двоичных кодов делимого (остатков) и делителя. Регистр 1 делимого (п+1)-разрядный, из которых один разряд расположен слева от запятой и п разрядов справа рт запятой. Регистр 2 делителя содержит п разрядов, которые все расположены справа от запятой. В первом такте деления в эти регистры загружаются двоичные коды делимого и делителя, которые являются правильными положительными дробями. Регистры могут быть реализованы на основе двухтактных синхронны с DVтриггеров. Запись информации в регистры

производится по синхроимпульсу при наличии разрешающего потенциала на их V-BXOдах. V-входы всех триггеров регистра 1 делимого объединены и подключеньгк выходу 16, а V-входы всех триггеров регистра 2 делителя - к выходу 17 блока 12 управления. Регистр 3 частного предназначен для хранения частного и реализован в виде регистра с возможностью однотактного сдвига на к разрядов в сторону старших разрядов. Входы к его младших разрядов соединены с выходами первого узла б коррекции частного. Он может быть построен на основе двухтактных синхронных D-триг5 герое, причем выход i-ro триггера (,2,...(k), где I - разрядность частного) соединен с информационным входом (i+k)-ro триггера.Запись информации в регистр 3 производится по синхроимпульсу, поступающему с

0 входа 14 синхронизации устройства.

Блок 14 ;1еления усеченных чисел предназначен для получения (k+1)-paзpяднoгo частного .от деления старших ( k+1) разрядов делимого, поступающих с выходов 21

5 регистра 1 и старших k+1 разрядив делителя, поступающих с выходов 23 регистра 2 делителя. При небольших значениях k блок 4 деления усеченных чисел может быть разработан по соответствующей таблице истинности либо в виде быстродействующего логического шифратора, либо в виде быстрой поисковой таблицы, реализованной на ПЗУ, причем в этом случае целесообразна совместная реализация блока 4 с вторым

5 узлом 5 коррекции частного. При больших лжезначениях k более предпочтительной является реализация блока 4 в виде быстродействующей однотактной матричной схемы деления. исг ользующей алгоритм с

0 восстановлением или без восстановления остатков и все известные средства ускоренной реализации этих алгоритмов. Возможны и другие варианты реализации блока 4 деления усеченных чисел.

5Значение частного, получаемого на выходах 24i и 242 блока 4 при делении в нем значения k+1 старших разрядов делимого (или остатка) на k+1 старших разрядов делителя, может быть либо равно значению k

0 старших разрядов истинного частного, получаемого при делении п-разрядных чисел, либо больше (меньше) на одну единицу .младшего разряда зтого значения.

Второй узел 5 предназначен для предварительной коррекции значения цифр частного, формируемого на выходах 241 и 242 блока 4 деления. Если в блоке 4 деления формируется частное, у которого значение старшего разряда равно единице, то на выходах узла 5 образуется значение скорректированного k-разрядного частного виде 11...1.

Если же значение старшего разряда равно нулю, то значение k младших :. -цифр частного, сформированное на выходах 242 блока 4 деления, передается транзитом на выходы 25 узла 5.

Первый узел 6 коррекции предназначен для окончательной коррекции частного, сформированного в текущем такте. Как было показано выше, значение k-разрядного честного, поступающего с выходов 25 узла

5на вход узла 6, в некоторых случаях может быть на единицу младшего разряда больше или меньше истинного значения k-разрядного частного, и тогда в узле 6 осуществляется соответственно либо вычитание из k-разрядного частного значения единицы, либо прибавление к k-paзpяднoмv частному значению единицы. Управление работой первого узла 6 коррекции осуществляется по значению сигналов с выходов 18 и 19 знаковых разрядов соответственно второго вычитателя 9 и сумматора-вычитателя. Так, при наличии на выходе 18 сигнала 1 в узле

6осуществляется вычитание из k-разрядного частного единицы его младшего разряда. Если же на выходе 18 присутствует О, то функционирование узла б определяется значением знакового разряда, поступающего с выхода 19 сумматора-вычитателя 10. Если зто значение равно единице, то информация проходит через узел 6 без изменения. В противном случае происходит прибавление к k-разрядному частному единицы младшего разряда.

В блоке 7 умножения осуществляется перемножение k-разрядного частного, сформированного на выходах 25 второго узла 5 коррекции и поступающего на вторую группу входов блока 7 и п-разрядного делителя, хранимого в регистре 2 и поступающего на первую группу входов блока 7 с выходов 22 разрядов регистра 2. На выходах 26 и 27 первой и второй групп блока 7 образуется произведение в двухрядном коде (в виде двух чисел). Блок 7 умножения комбинационного типа может быть реализован в виде совокупности из k-разрядных двоичных умножителей.

С помощью первого вычитателя 8, второго вычитателя 9 и сумматора-вычитателя 10 в устойстве формируется два возможных значения остатка, одно из которых записывается в качестве нового остатка через коммутатор 11 в регистр 1 делимого в зависимости от значения k-разрядного частного на выходах 25 узла 5. Если данное k-разрядное частное равно истинному kразрядному частному, то в регистр 1 делимого в качестве нового остатка заносится значение остатка с аыходов 30 второго вычитателя 9, если данное k-разрядное частное больше или меньше, чем истинное 5 k-разрядное на одну единицу его младшего разряда то новый остаток формируется на выходах 31 сумматора-вычитателя 10.

Первый вычитатель 8 комбинационного типа и выполнен по принципу вычитателя

0 без распространения заема. В вычитателе 8 осуществляется вычитание из содержимого регистра 1 делимого произведения, сформированного на выходах 26 и 27 блока 7 умножения в двухрядном коде. Результат

5 вычитания образуется на выходах 28 и 29 соответственно разности и заема вычитате, ля 8 в двухрядном коде.

Второй вычитатель 9 предназначен для вычитания из значения: разности, сформированной на выходах 28 первого вычитателя 8, значения заема, образованного на выходах 29 зтого же вычитателя 8. Второй вычитатель 9 комбинационного типа, с ускоренным распространением заема может быть заменен быстродействующим сумматором, если информацию, поступающую на его вход вычитаемого, проинвертировать, а на вход переноса сумматора подать сигнал 1. Выход 18 знакового разряда второго , вычитателя 9 соединен с управляющим входом сумматора-вычитателя и первым входом управления первого узла 6 коррекции частного.

Если разность делимого (остатка), хранимого в регистре 1, и произведения, образованного на выходах блока 7 умножения, положительна, то в знаковом разряде второго вычитателя 9 формируется значение О, что настраивает сумматор-вычитатель 10 на

0 вычитание, если же данная разность отрицательна, то в знаковом разряде второго вычитателя 9 формируется значение 1, что настраивает сумматор-вычитатель 10 на сложение.

5 Сумматор-вычитатель 10 предназначен для коррекции промежуточного значения ocTatKa, образуемого на выходах 30 второго вычитателя 9, если на выходах 25 узла 5 получилось k-разрядное частное большее

0 или меньшее истинного. Так, если значение k-разрядного частного на выходах 25 узла 5 больше на единицу истинного значения kразрядного частного, то промежуточное значение остатка на выходах вычитателя 9

5 получается отрицательными и Г с выхода 18 знакового разряда вычитателя 9 поступает на управляющий вход сумматор а-вычитателя 10 и настраивает его на режим суммирования промежуточного значения остатка со значением делителя. При этом на

выходах 31 образуется скорректированное значение остатка. Если же значение k-разрядногО;настного на выходах 25 узла 5 меньше на единицу истинного значения k-paзpяднoгQ частного, то промежуточное значение остатка на выходах вычитателя 9 получается положительным и О с выхода 18 настраивает сумматор-вычитатель 10 на режим вычитания из промежуточного значения остатка значения делителя. При зтом на выходах 31 образуется скорректированное значение остатка.

Сумматор-вычитатель может быть построен на основе сумматора с управляемым инвертором на одном входе.

Коммутатор 11 предназначен для nejaeдачи на информационные входы регистра 11 делимого информации с трех направлений через соответствующие группы входов. Через первую группу входов поступает значение делимого с входа 13 данных устройства, через вторую группу входов - значение остатка с выходов 30 вычитателя 9 (случай, когда значение частного на выходах 25 совпадает с истинным значением частного), через третью группу входов - значение скорректированного остатка с выходов 31 сумматора-вьмитателя (случай, когда значение частного на выходах 25 больше или меньше истинного на единицу младшего разряда). Управление работой коммутатора 11 осуществляется сигналами, формируемыми на выходе 15 блока 13 управления и на выходе 19 знакового разряда сумматоравычитателя 10. Коммутатор 11 может быть построен, например, на четырехвходовых мультиплексорах.

Устройство работает следующим образом.

Перед началйм выполнения собственно деления в регистр 1 делимого и регистр 2 делителя заносится п-разрядный код делимого и п-разрядный код делителя соответственно, блок управления устанавливается в исходное состояние (делимое загружается в .п младших разрядов регистра 1. в старший разряд которого записывается ноль). Предполагается, что Делимое и делитель - правильные положительные нормализованные дроби. Процесс определения окончательного частного.состоит из m циклов, в каждом из которых формируется k двоичных цифр

частного (где число k-разрядных групп

1

частного).

Каждый цикл начинается с определения k-разрядногЬ частного, формируемого совместно блоком 4 и узлом 5 коррекции частного. На входы блока А при этом поступают значения k+1 старших разрядов регистра 1

делимого (один разряд слева от запятой, остальные - справа от запятой) i/i значения k+1 старших разрядов регистра 2 делителя (все разряды расположены справа от запятой, Затем k-разрядное частное, образованное на выходах 25 узла 5, умножается на п-разрядный делитель в блоке 7 умножения и на выходах 30 второго вычитателя 9 образуется остаток, равный разности между

0 предыдущим остатком и полученным произведением. В конце цикла деления в регистр 1 делимого через коммутатор 11 заносится информация из двух возможных источников. Выбор источника осуществляется значением сигнала, формируемого на выхода 19 знакового разряда сумматора-вычитателя 10. Если значение скорректированного остатка, получаемого на сумматоре-вычитателе 10. отрицательно (случай, когда промежуточное значение остатка на выходах 30 вычитателя 9 положительно и сумматор-вычитэтель настраивается на вычитание), то через коммутатор 11 в регистр 1 делимого заносится значение нового остатка с выходов 30 второго вычитателя 9. Если же значение скорректированного остатка положительно, то в регистр 1 делимого заносится значение нового остатка с выходов 31 сумматора-вычитателя 10. Одновремен0 но с коррекцией остатка выполняется кор. рекция k-разрядного частного в узле б, куда поступают значения знаковых разрядов второго вычитателя 9 и сумматора-вычитателя 10. В конце каждого цикла деления

5 k-разрядное частное записывается в младшую часть регистра 3, освобождающуюся при сдвиге в регистре 3 информации но k разрядов в сторону старших рязрядов. Формула изобретения

0 1. Устройство для деления, содержащее регистры делимого, делителя и частного, блок деления усеченных чисел, первый узел коррекции частного, блок умножения, два вычитателя, сумматор-вычитатель, коммутатор и блок управления, причем вход данных устройства соединен с информационными входами первой группы коммутатора и с информационными входами регистра делителя, выходы разрядов которого соединены с

0 входами первой группы блока умножения и сумматора-вычитателя. выходы коммутатора соединены с информационными входами регистра делимого, выходы старших рэзрядов которого соединены с входами делимого блока деления усеченных чисел, выходы разрядов регистра делимого соединены с входами уменьшаемого первого вычитателя, входы вычитаемого и заема которого соединены с выходами первой и второй групп блока умножения соответственчо.

разности и заема первого вычитателя - с входами уменьшаемого и вычитаемого второго вычитателя; выходы которого соединены с входами второй группы сумматоравычитателя и коммутатора, входы третьей группы которого соединены с выходами сумматора-вычитателя, выход знакового разряда сумматора-вычитателя соединен с первым управляющим входом первого узла коррекции частного, выход которого соединён с информационным входом регистра частного,, синхровход которого соединен с входом синхронизации устройства и с синхровходами регистров делимого и делителя и блока управления, первый выход которого соединен с первым управляющим входом коммутатора, второй и третий выходы - с входами разрешения записи регистров делимого и делителя соответственно, о т л и ч ающее с я тем, что, с целью упрощения, оно содержит второй узел коррекции частного, управляющий и информационный входы которого соеди нены с выходами

1В119

Фиг. 2

старшего и младшего разрядов соответственно блока деления усеченных чисел, вход делителя которого соединен -с выходами старших разрядов регистра делителя, выходы второго узла коррекции частного - с входами второй группы блока умножения и информационными входами первого узла коррекции частного, второй управляющий вход которого соединен с выходом знакового разряда второго вычитателя и управляющим входом сумматора-вычитателя, выход знакового разряда которого соединен с вторым управляющим входом коммутатора.

2, Устройство по П.1, о т л и ч а ю щ е ес я тем, что блок управлен1/ я содержит счетчик памяти микрокоманд, причем счетный вход счетчика соединен с синхроеходом блока управления, первый, второй и третий выходы которого соединены с одноименными выходами узла памяти микрюкоманд соответственно, адрех:ный вход которого соединен с выходом счетчика.

Фаг.Ъ

| Устройство для деления | 1988 |

|

SU1541596A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Механическая топочная решетка с наклонными частью подвижными, частью неподвижными колосниковыми элементами | 1917 |

|

SU1988A1 |

| кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Механизм для сообщения поршню рабочего цилиндра возвратно-поступательного движения | 1918 |

|

SU1989A1 |

Авторы

Даты

1992-01-30—Публикация

1989-03-06—Подача