мирователи логических уровней с выходами второго и третьего счетчиков соответственно, управляющие входы первых и вторых формирователей логических ур9вней соединены с соответствующими третьими входными клеммами устройства.

2. Устройство по п. 1, отличающееся тем, что блок управления содержит формирователь синала сброса, соединенный входом с вторым входом блока, выходом - с первым выходом блока, соединенного третьими входами с первыми входами форг шрователя сигналов управления.

вторые входы которого соединены с шестыми входами блока, первая группа которых соединена с входами программатора источника питания и индикатора, вторая группа - с первыми входами формирователя импульсов записи, соединенного вторым входом с пятым входом блока, выходами - с тре тьими выходами блока, соединенного пятыми выходами с соответствующими выходами формирователя сигналов управления, один из которых соединен с первым входом элемента ИЛИ, соединенного вторым входом с четвертым входом блока, выходом - с вторым выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для функционально-параметрического контроля логических элементов | 1982 |

|

SU1140065A1 |

| Устройство для функционально-параметрического контроля логических элементов | 1985 |

|

SU1302220A2 |

| Устройство для функционально-параметрического контроля логических элементов | 1987 |

|

SU1562864A1 |

| Устройство сигнатурного контроля проводных соединений | 1986 |

|

SU1385105A1 |

| Устройство для контроля цифровой аппаратуры | 1989 |

|

SU1735854A1 |

| Устройство для обнаружения ошибок в блоке постоянной памяти | 1984 |

|

SU1246141A1 |

| Устройство для контроля цифровых блоков | 1989 |

|

SU1742753A1 |

| Устройство для диагностирования логических блоков | 1982 |

|

SU1071978A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

| Устройство для контроля электрических параметров цифровых узлов | 1984 |

|

SU1260974A1 |

1. УСТРОЙСТВО ДЛЯ ФУНКЦИОНАЛЬНО-ПАРАМЕТРИЧЕСКОГО КОНТРОЛЯ ЛОГИЧЕСКИХ ЭЛЕМЕНТОВ, содержащее генератор импульсов, соединенный выходом со счетным входом первого счетчика, коммутатор, соединенный первыми входами с клеммами для подключения выходов контролируемого логического элемента, дешифратор, соединенный входами с первыми выходами коммутатора, мультиплексор соединенный информационными и .адресными входами соответственно с вторыми и третьими выходами коммутатора, выходом - с первым информационным входом сигнатурного анализатора, первые и вторые клеммы для подключения входов контролируемого логичес кого элемента соединены соответст- -, венно четвертыми и пятыми выходами-коммутатора, отли-чающее с я тем, что, с целью повышения достоверности контроля, в устройство введены делитель частоты, второй и третий счетчики, первые и вторые формирователи логических уровней, R.S -триггер, программируемый источник питания.датчик тока потребления, компаратор, анализатор,неисправности, блок нагрузок и блок управления, соединенный первым выходом с установочными входами сигнатурного анализатора, второго и третьего счетчиков и анализатора неисправности, вторым и третьими входами - с соответстяуюпими первой и второй входными клеммами устройства, вторым выходом - с блокирующими входами делителя частоты, третьего счетчикаи анализатора неисправности, третьими выходами - с информационными входами первого счетчика, четвертым входом - с выходом анализатора неисправ ности И с выходной клеммой устройства,, четвертым выходом - со стробирующим входом анализатора неисправности, пятыми выходами - с управлякяцими входами программируемого источника питания, пятыми входами с выходами третьего счетчцка, шестым входом - с s-входом US -триггера, со счетным входом второго счетчика и с выходом делителя частоты, соединенного входом со счетным входом первого счетчика , выход переполнения которого соединен с Я -входом ftS -триггера, соединенного выходом с синхровходом первого счетчика и с первым синхровходом сигнатурного .анализатора, второй (Сиихровход которого соединен со счет/ ным входсм третьего счетчика и с шестым выходом коммутатора, выходы с первьми инфо{ |ационными входами ангшизатора неисправности, вторые i информсщионные входы - с седьмыми 4i СЛ выходами коммутатора, соединенного вторыми выходами с входами блока СлЭ нагрузок, восьмом выходом - с управляющим входом компаратора, соединенного выходом с вторым информационным входом анализатора неисправности, измерительньм входом через ,датчик тока потребления - с общей шиной устройства, a непосредственно - с токовым входом программируе-. мого источника питания, соединенного выходом с-клеммой для подключения вывода питания контролируемого логического элемента, a третьи вхо,ды коммутатора соединены через соответствующие первые и вторые фор

Изобретение относится к контроль но-измерительной технике и может бы использовано для контроля логически элементов, например микросхем и пла с микросхемами. Известно устройство для контроля схем цифровых вычислительных машин, содержащее блок ввода, регистр зада НИИ и хранении информации, кЬммутатор, блок сравнения, компаратор, бл управления и блок эталонов СИ. Недостатком известного устройст ва яв.ляются ограниченные функционал ные возможности- вследствие отсутстВИЯ динамического контроля. Наиболее близким к изобретению является устройство для функциональ но-параметрического контроля логических элементов, содержащее генератор импульсов, соединенный-ВЫходом со счетным входом первого счетчика, коммутатор, соединенныйпервыми входами с клеммами для подключения выходов контролируемого логического элемента, дешифратор, соединенный входами с первыми выхода коммутатора, мультиплек сор, сЬедийенный информационными и адресными входами соответственно с вторыми и третьими выходами коммутатора, выходом - с первым инфор- мационным входом сигнатурного анализатора, первые и вторые клеммы для подключения входов контролируемого логического элемента соединены соответственно с четвертыми и пятыми выходами коммутатора L21. Недостатком известного устройства является низкая достоверность контроля из-за невозможности контроля динамических параметров и воз можности качки напряжения питания в процессе контроля. ,Цель изобретения - повышение достоверности контроля, I Поставленная цель достигается тем, что в устройство для функционально-параметрического контроля логических элементов содержащее генератор импульсов, соединенный выходом со счетным входом первого счетчика, коммутатор, соединенный первы «1 входами с клеммами для подключения выходов контролируемого логического элемента, дешифратор, соединенный входами с первыми выходами коммутатора, мультиплексор, соединенный информационными и адресными входс ми соответственно с вторыми и -третьими выходами коммутатора, выходом - ,с первым информационным входом сигнатурного анализатора, первые и вторые клеммы для подключения входов контролируемого логического элемента соединены соответственно с четвертыми и пятыми выходами коммутатора, введены делитель частоты, второй и третий счетчики, первые и вторые формирователи логических уровней, RS -триггер, пpoгpaммиpye вJй источник питания, .датчик тока потребления, компаратор) анализатор неисправности, блок нагрузок и блок управления, соединенный первым выходом с установочными входами сигнатурного анализатора, второго и третьего счетчиков и анализатора неисправности, вторым и третьими входами - с соответствующими первой и второй входньвищ клеммами устройстьа, вторым выходе - с блокирующими входами делителя частоты третьего счетчика и анализатора неисправности, третьими выходами - с информационными входами первого счетчика, четвертым входом - с выходом анализатора неисправности и с выходной клеммой устройства, четвертым выходом со стробирующим входом анализатора неисправности пятыми выходами - с управляющими входами программируемого источника питания, пятыми входами - с выходами третьего счетчика шестым входом - с S -входом

R$ -триггера, со счетным входом второго счетчика и с выходом iделителя частоты, соединенного .входом со счетным входом первого счетчика, выход переполнения которого соединен с R. -входом ftS -триг гера, соединенного выходом с синхровходом первого счетчика и с первым синхровходом сигнатурного анализатора второй синхровход которого соединен со счетным входом третьего счетчика и с шестым выходом коммутатора, выходы - с первыми информационными входами анализатора неисправности, вторые информационные входы - с седьмыми выходами кол иутатора , соединенного вторыми выходами с входами блока нагрузок, воським выходом - с управляющим входом компаратора, соединенного выходом с вторым информационным входом анализатора неисправности, измеритель-ным входом через датчик оюка потребления - с общей шиной устройства, а непосредственно - с токовьм входом програкмируемого источника питания, соединенного выходом с клеммой для подключения вывода питания контролируемого логического, элемента, а третьи входы коммутатора соединены через соответствующие первые и вторые формирователи логических уровней с выхода 4и второго и третьего счетчиков сортветственно, управляющие входы первых и вторых формирователей логических уровней соединены с соответствующими третьими входными клеммами устройства.

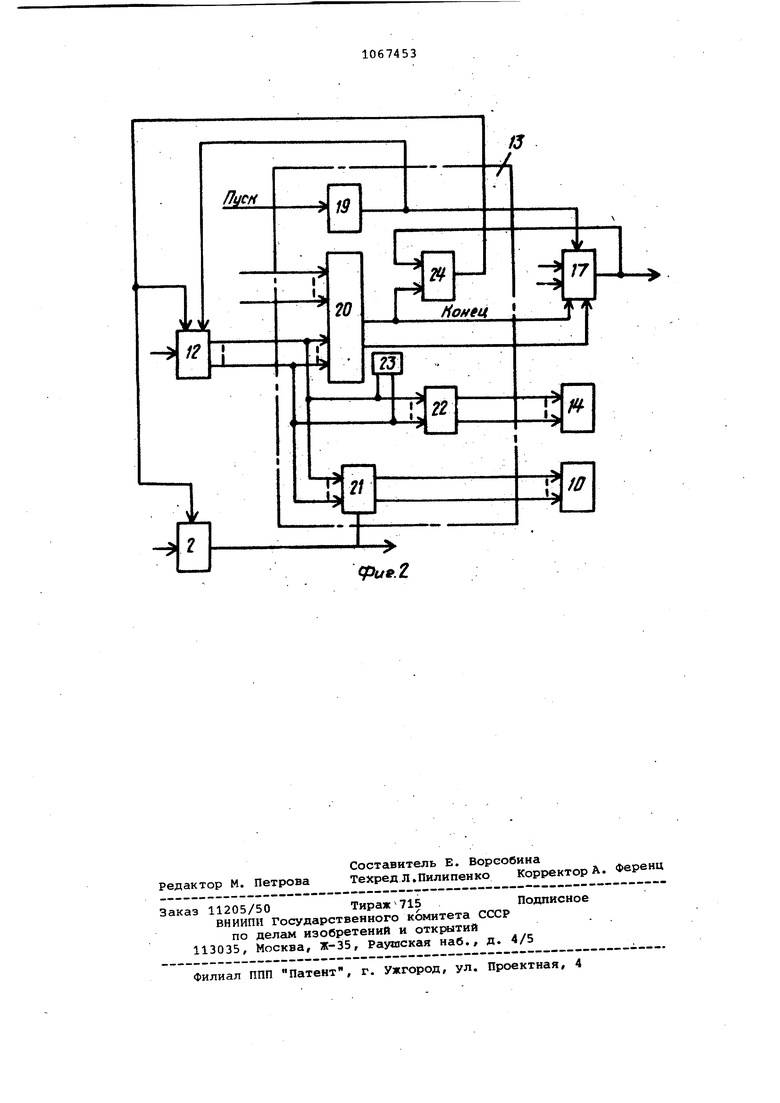

Блок управления содержит форми рователь сигнала сброса , соединенны входом с вторым входом блока, выходом - с первым выходом блока, соединенного третьими входами с первыми входами формирователя сигиалов управления, вторые входы которого соединены с шестыми входами блока первая группа которых соедииеиа с входами программатора источника пигания и индикатора, вторая группа с первыми входами формирователя импульсов Зсшиси, соединенного вторым входом с пятым входом блока, выходами - с третьими выходами блока, соединенного пятыми выходами с соответствующими выходами формирователя сигналов управления, один из которых соединен с первым входом элемента ИЛИ, соединенного вторым входом с четвертым входом блока, выходом .с вторым выходом блока.

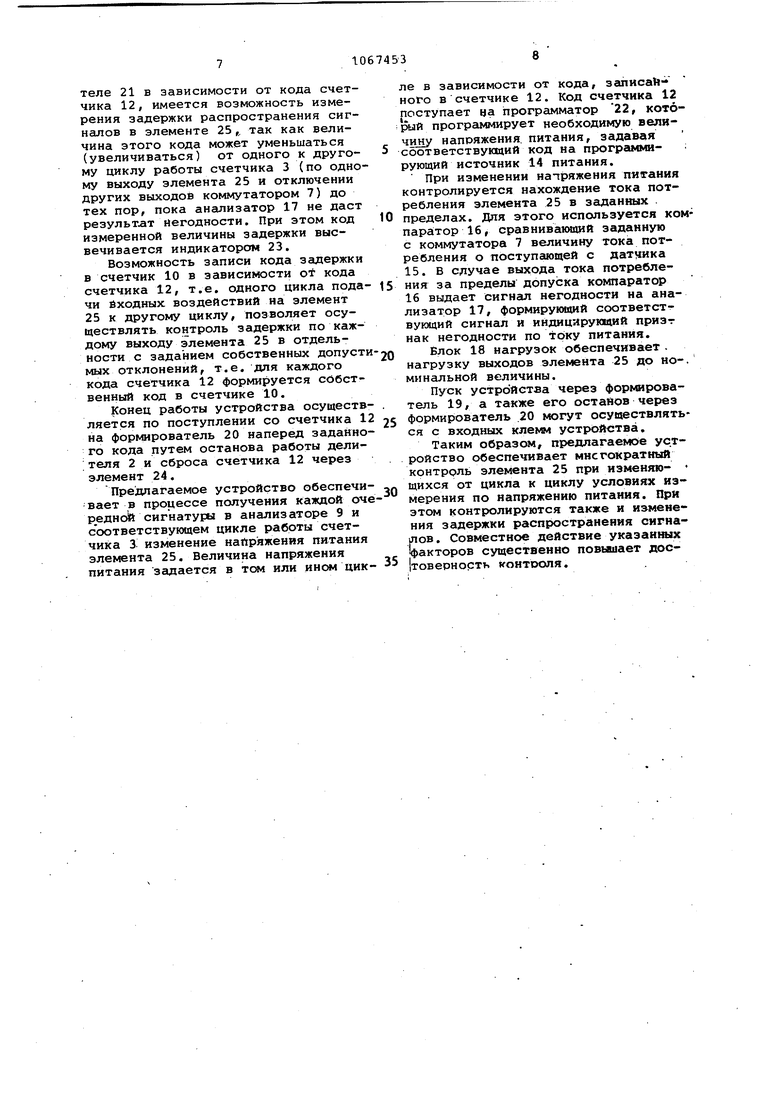

На фиг. 1 приведена блок-схема устройства; на фиг.. 2 - блокг-схема блока управления, в связи с другими блоками устройства.

Устройство содержит генератор 1 импульсов, делитель 2 частоты, счетчик 3, дешифратор 4, первые 5д-5гг

0 и вторые 6п фop шpoвaтeли логических уровней, коммутатор 7, муль типлексор 8, сигнатурный анализатор 9, счетчик 10, ft.3 -триггер 11, счетчик 12, блок 13 управления,

5 программируемый источник 14 питания,: датчик 15 тока потребления. Конпаратор 16, анализатор 17 неисправности, блок 18 нагрузок.

Блок 13 управления содержит фор-i мирователь 19 сигналов сброса, формирователь 20 сигналов управления, формирователь 21. импульсов записи, программатор 22 источника питания, индикатор 23, элемент 24 ИЛИ. На :фиг. 1 показан также контролируемый

5 логический элемент 25.

Устройство работает следующим образом.

I . . t

Перед началом работы с помощью элементов коммутации, например на0борного поля, кнопок, кнсшочных переключателей, перемычек, Зсщаются необходимые дл{1 проверки данного типа логического элемента соединения элементов устройства.

На анализатор 9 с коммутатора 7 задается эталонная сигнатура, на компаратор 16 - значения эталонного тока потребления элемента.25 по цепи питания. Кроме того, коммута-тор 7 коммутирует часть входов элемента 25 через формирователи 5 непосредственно к выходам первых i разрядов счетчика 3, а другие его ,. выходы через формирователи к . выходам дешифратора 4. Счетчик 3 имеет п разрядов. Первые его i разрядов коммутируются, например, к входам элемента 25, разряды с i+1 до п-1 - к адресным входам , мультиплексора 8, а п-й разряд к входу сигнатурного анализатора 9, разрешающему (по логической единице) получение сигнатур, а также к входу счетчика 12.

Перед началом работ устройства на вход блока 13 задается сигнал , обеспечивающий через формирователь 19 сброс в исходное состояние счетчика 12, анализатора 17 неисправности, сигнатурного анализатора 9 и счетчика 3.

После проведения исходной установки генератор 1 задает непрерывную последовательность импульсов на вход делителя 2 частоты. Делитель 2 частоты на серию из 54 входных импульсов формирует один выходной импульс по переднему фронту первого импульса, с выхода делителя 2 стробируется формирователь 21 и код допустимой временной задержки сигнала в элементе 25 переписывается из формирователя 21 в счетчик 10. При этом указанный код может быть сформирован, например, кно 1почным переключателем, входящим в состав формирователя 21, или формироваться (различной величины), например, по приходу различных кодов со счетчика,12, состояния которого индицируются индикатором 23, что позволяет оценить величину задержки . По приходу задних фронтов импульсов с делителя 2 происходит их счет в счетчике 3 и смена входных воздействий на входах формирователя 19, Деишфратор 4 обеспечивает задание на входы элемента 25 воздейст ий в необходиь ле по временной диаг рамме проверке моменты времени,. ормирователи 5 и 6 формируют велич ну необходимых входных (граничных) уровней для элемента 25. в зависи- i мости от управляющих сигналов на их входах, В результате исходной установки устройства при первом цикле работы счетчика 3 с его i+1 разряда поступает разрешение на первый адресный вход мультиплексора 8, что приводит к подключению первого выхода элемен та 25 к входу анализатора 9, При последующих циклах работы устройства счетчик 3 опрашивает последующие адресные входы мультиплексора 8, оп рашивая/ таким образом, все остальные выходы элемента 25, Указанная последовательность работы обеспечивает получение в ана лизаторе 9 сжатого шестнадцатиричного кода, характеризующего все выходы элементов 25 по всем входным воздействиям, при этом счетчик.3 реализует число циклов воздействий на элемент 25, равное или больше . числа выходов элемента 25. При Каждом очередном воздействии (тесте) на входы элемента 25 срабатывает совокупность элементов 2, 11 и 10, которые обеспечивают контроль задержки распространения элемента 25 следунндим образом. После того, как на счетчик 3 задан данный фронт первого импульса в очередном цикле его работы и триг гер 11 (по переднему фронту этого импульса) установлен в состояние, запрещающее работу анализатора 9, импульсы от- генератора 1 дополняют написанный в счетчик 10 код. В-. момент переполнения счетчика 10 выдаев.ся сигнал, переключающий триггер 11 и счетчик 10 в исходное состояние и разрешающий (стробирующий) работу анализатора 9, Если за время дополнения счетчика 10 до максимального кода элемент 25 не успел сформировать на своем выходе необходимый для данного входного воздействия логический уровень, т,е, он негоден по быстродействию, то сигнатура, полученная в анализаторе 9, не совпадает с эталонной. Указанная последовательность работы обеспечивает контроль задержек распространения по заданному пределу допустимых значений последовательно по каждому выходу элемента 25 для каждого входного воздействия, После получения первой суммарной сттнатуры элемента 25 по всем его.выходам сигнал логического нуля на входе анализатора 9, сформированный п-м разрядом счетчика 3, меняется на логическую единицу. В результате запрещается прием информации в анализатор 9 от мультиплексора 8 и добавляется единица в счетчик 12, В момент запрета приема информации анализатор 9 сравнивает эталонную и полученные сигнатуры, , После многократного повторения циклов получения сигнатур элемента 25, которое производится для повышения достоверности результата контроля, в счетчике 3 записано заданное число повторений (число полученных сигнатур). Формирователь 20 сигналов управления, настроентзй на это число после его дешифрации, выдает сигнал опроса на анализатор 17, К моменту опроса анализатор 9 сравнивает полученную и эталонную сигнатуры и выдает соответствующий сигнап на анализатор 17. Анализатор 17 предназначен для выявления неисправности индикации ее вида и другой вспомогательной информации , По поступлении сигнала опрос от формирователя 20 блока 13 анализатор 17 выдает сигнал годности или негодности элемента 25 на индикацию, на выход устройства и в блок 13 на элемент 24, В случае негодности на вход элемента 24 с выхода анализатора 17 поступает логическая единица, которая передается на вход делителя 2 и счетчика 12, запрещая их работу и останавливая дальнейшую работу устройства В момент останова анализатор 17 индицирует полученную и эталонную сигнатуры, В том случае, если код величины за.це§жки формируется в формирователе 21 в зависимости от кода счетчика 12, имеется возможность измерения задержки распространения сигналов в элементе 25,, так как величина этого кода может уменьшаться (увеличиваться) от одного к другону циклу работы счетчика 3 (по одному выходу элемента 25 и отключении других выходов коммутатором 7) до тех пор, пока анализатор 17 не даст результат негодности. При этом код измеренной величины задержки высвечивается индикатором 23.

Возможность записи кода задержки в счетчик 10 в зависимости от кода счетчика 12, т.е. одного цикла подачи Входных воздействий на элемент 25 к другому циклу, позволяет осуществлять контроль задержки по каждому выходу элемента 25 в отдельности с заданием собственных допусти мых отклонений, т.е. для каждого кода счетчика 12 формируется собственный код в счетчике 10.

Конец работы устройства осуществляется по поступлении со счетчика 12 на формирователь 20 наперед заданного кода путем останова работы делителя 2 и сброса счетчика 12 через элемент 24.

Предлагаемое устройство обеспечивает в процессе получения каждой очеpjeдней сигнатуры в анализаторе 9 и соответствующем цикле работы счетчика 3 изменение напряжения питания элемента 25, Величина напряжения питания задается в том или ином цикле в зависимости от кода, згшисай- ного в счетчике 12. Код счетчика 12 поступает ца программатор 22, который прогргилмирует необходимую величину напряжения, питания, задавая соответствующий код на программирующий источник 14 питания.

При изменении напряжения питания контролируется нахождение тока потребления элемента 25 в заданных . пределах. Дня этого используется копара:тор 16, сравнивакиций заданную с коммутатора 7 величину тока потребления о поступающей с датчика 15. В случае выхода тока потребления за пределы допуска компаратор 16 выдает сигнал негодности на анализатор 17, формирукиций соответствующий сигнал и индицирующий призт нак негодности по питания.

Блок 18 нагрузок обеспечивает нагрузку выходов элемента 25 до номинальной величины.

Пуск устройства через формирователь 19, а также его остайов через формирователь .20 могут осуществляться с входных клемм устрюйства.

Таким образом, предлагаемое устройство обеспечивает многократный контроль элемента 25 при изменяющихся от цикла к циклу условиях измерения по напряжению питания. При контролируются также и изменения задержки распространения сигналов. Совместное действие указанных факторов существенно повышает дос|товерность контооля.

/5

О

14-т

tn

М

/J

б-/

т

12

//

/

Cpuf.1

f6

1/8

s

i

ns

5

rf

J L. Т

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| УСТРОЙСТВО для КОНТРОЛЯ СХЕМ ЦИФРОВЫХ ВЫЧИСЛИТЕЛЬНЫХ МАШИН | 0 |

|

SU378852A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для функционально-парамет-РичЕСКОгО КОНТРОля лОгичЕСКиХэлЕМЕНТОВ | 1979 |

|

SU830391A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1984-01-15—Публикация

1982-07-19—Подача