(54) ДЕМОДУЛЯТОР СИГНАЛОВ С ФАЗОРАЗНОСТНОЙ

1

Изобретение относится к радиотехнике и может использоваться для детектирования фазоманипулированных сигналов в диапазоне дегшметровых или сантиметровых волн.

Известен демодулятор сигналов с фа- зоразностной модуляцией, содержащий генератор опорных сигналов, блок синхронизации и фильтры верхних частот, выходы которых соединены с соответствуюши- ,Q ми детекторами и входами фильтров нижних частот, выходы которых подключены к первым входам соответствующих блоков памяти, вторые входы которых соединены с выходами блока синхронизации, а также j компаратор, выходы которого соединены с выходами сумматоров 1 ,

Однако известный демодулятор имеет узкий частотный диапазон.

Цель изобретения - расширение частот-20 ного диапазона.

Поставленная цель достигается тем, что в демодулятор сигналов с фазоразностной модуляцией, содержащий генератор

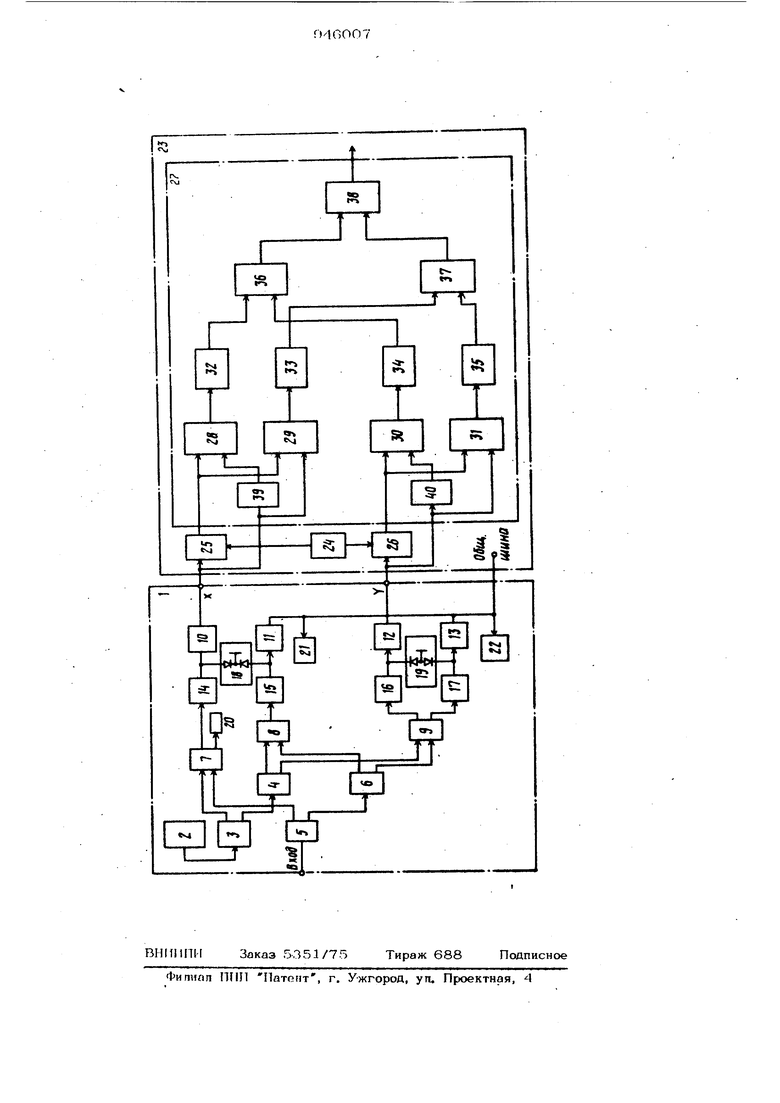

МОДУЛЯЦИЕЙ

опорных сигналов, блок синхронизации и фильтры верхних частот, выходы которых соединень с соответствующими детекторами и входами фильтров нижних частот, выходы которых подключены к первым входам соответствующих блоков памяти, вторые входы которых соединены с выхо-дами блока синхронизации, а также компаратор, входы которого соединены с выходами сумматоров, введены четыре дополнительных сумматора,. четыре делителя мощности, три сумматора мощности, два инвертора и четыре вьшрямителя, выходы которых подключены ко входам сумматоров, при этом выход генератора опорных сигналов соединен со входом первого делителя мощности, выходы которого соединены со входом второго делителя мощности и с первым входом первого сумматора мощности, второй вход которого соединен с первым выходом третьего делителя мощности, второй выход которого подключен ко входу четвертого делителя мощности, выходы которого соединены с 394 первыми входами второго и третьего сум- маторов мощности, вторые входы которых соединены с выходами второго делителя мощности, а выходы сумматоров мощности подключены ко входам соответс1вующих фильтров верхних частот, причем первый вход первого блока памяти соединен со входом первого инвертора, выход которого подключен к первому входу первого дополнительного сумматора, второй вход которого соединен с выходом первото блока памяти и с первым входом второго-допол- нительного сумматора, второй вход кото-. рого соединен со входом первого инвертора, выход второго блока памяти подключен к первым входам третьего и четвертого дополнительных сумматоров, вторые входы которых соединены соответственно с выходами и с входом второго инвертора, при этом выходы дополнительных сумматоров подключены ко входам соответствующих выпрямителей, а первый вход второго блока памяти соединен со входом второго инвертора. На чертеже представлена структурная электрическая схема предлагаемого демодулятора. Демодулятор сигналов с фазоразностной модуляцией содержит блок 1 обработки световых частот сигнала, состоящий из генератора 2 опорных сигналов, первого, второго, третьего и четвертого делителей мощности 3 - 6 соответственно, первого, второго и третьего сумматоров 7 - 9 мощности соответственно, четырех фильтров нижних частот 10 - 13, четырех фильтров верхних частот 14 - 17, двух детекторов 18, 19 и трех согласоватшых нагрузок 2О - 22, блок 23 обработки видеосигнала, состоящий из блока 24 синхронизации, первого и второго блоков 25 и 26 памяти соответственно и блока 27 вычисления разности фаз, который содержит четыре дополнительных сумматора 28-31, четыре вьшрямителя 32 35, два сумматора 36 и 37, компаратор 38 и первый и второй инверторы 39 и 40 соответственно. Демодулятор работает следующим образом . Сигнад от генератора опорных сигналов 2 ( SP ) поступает на вход первого депителя 3 мощности, проходит на один из его выходов и далее на один из входов первого сумматора 7 мощности. Входной СВЧ сигнал ( 5 ) поступает на вход третьего делителя 5 мощности, в котором происходит деление мощности на две равные части. Сигнал с одного з выходов 7.4 третьего делителя 5 мощности поступает на вход первого сумматора 7 мощности, Таким образом, на два входа первого сумматора 7 мощности подаются два сигнала : один от генератора опорных сигналов SQ ., второй - принимаемый фазоманипулированный сигнал S Так как первый сумматор 7 мощности выполнен на полуволновом шлейфном направленном ответвителе, на одном из диодов детектора 18 получается разность сигналов t с 5о . Это происходит вследствие того, что сигнал S, при прохождении по основной линии первого сумматора 7 мощности поступает на его выход, получив приращение фазы, равное /2, т. е. 1с. . Сигнал Sc. поступает от входа первого сумматора 7 мощности на выход, соединенный с фильтром 14 верхних частот и преодолевает отрезок линии длиной Я , обусловленной распространением по одному из щлейфов (длина Л-/2) и отрезку основной линии (длина Д./2) первого сумматора 7 мощности. Таким образом, за сигнала So на выходе первого сумматора мощности составляет , фаза сигнала составляет 21(7, и выполняется операция вычитания сигналов. На диод детектора 18, подключенный к выходу первого сумматора 7 мощности через фильтр верхних частот ФВЧ) 14, подается разность сигналов - SQ Обычно величины сигналов не выходят за пределы нелинейного участка вольт-амперной характеристики диода. Поэтому можно считать, что ток через диод пропорционален квадрату приложенного напряжения. На .паразитной емкости диода происходит интегрирование (усреднение) этого тока и в результате на этом диоде выделится постоянное напряжение, пропорциональное квадрату разности сигналов () Сигнал от генератора.2 (So ) после прохождения первого делителя 3 мощности по второму выходному каналу поступает на в;ход второго делителя 4 мощности, разветвляется на два равных сигнала. Один из этих сигналов поступает на один из входов второго сумматора 8 мощности. На второй вход второго сумматора В мощности подается сигнал, который поступает после прохождения через делители 5 и 6 мощности. На выходе второго сумматора 8 мощности после прохождения ФВЧ 15 на диоде детектора 18 выделяется постоянное напряжение, пропорциональное квадрату суммарного сигнала (Ъс. + SQ ). Так как один из диолов детектора 18, расположенный на выходе второго сумматора 8 мощности, включен последовательно с другим диодом детектора 18, включенным на выходе первого сумматора 7, то на цепочке двух диодов детектора 18 выделяется сигнал, который равен разности сигналов, выделенных на каждом из диодов. Обозначим этот сигнал через : хч-,.-§„ f Ч сЛ)-На одном из выходов второго сумматора 8 мощности, выполненного на четвертьволновом двухшлейфном направленном ответвителе, поступает сигнал от генератора 2, приобретая сдвиг фаз, равный Л/4 ( /2). Обозначим опорный сигнал, имеющий сдвиг на , через . На этот же выход поступает фазоманипулированный СВЧ сигнал, однако, получив сдвиг фаз, равный Л/2 ( ). Таким образом, на одном из выходов третьего сум матора 9 мощности , а следовательно и на одном из диодов детектора 19, выделяется сигнал, пропорциональный ( 5 + S(j ), а на втором выходе соответствую щего сумматора мощности и на втором из диодов детектора 19 выделяется сигнал, .р It пропорциональный (Sj- - S / i где Sg поворот фазы сигнала на 90. Последовательное соединение двух диодов детектора 19, включенных на выходах третьего сумматора 9 мощности, позволяет получить сигнал, равный разности напряжений на каждом из диодов, который обозначим через : ) Общая щина блока 23 соединена с выходами фильтров нижних частот 11 и 13, поэтому в блоке 23 поступают низкочастотные составляющие напряжений, выделивщиеся на диодт гх цепочках детекторов 18 и 19, т. е. сигналы Ч и у . Эти сигн лы представляют собой сигналы синфазног и квадратурного выходов блока обработки СВЧ сигналов. X и V через пер вый и второй блоки памяти поступают на первые входы дополнительных сумматоров 28-31 блока 27. На вторые входы этих дополнительных сумматоров напряжения синфазной и квадратурной составляющих сигнала поступают непосредственно или через инверторы 39 и 4О без задерж ки. На выходах дополнительных сумматоро формируются напряжения, соответствующие суммам к разностям синфазной и квадратурной составляющих сигналов соседних посылок. Если обозначить составляющие очередной посылки через и , а предыдущей посылки через Хи. и V|, ., тогда напряжения на выходах дополнительных сумматоров определ5потся Ху, t Xy, и У, ±М, , На выходах выпрямителей 3235 формируются абсолютные значения этих величин, которые поступают на входы сумматоров 36 и 37. Нетрудно убедиться, что на выходе сумматора 36 сформируется напряжение U соответствующее разностям проекций соседних посылок, т. е. -- H- «M/ / -Vi/, (1) а на выходе сумматора 37 - напряжение , соответствующее сумме проекций соседних посылок, т. е. ,/-«-/yh H-i/- (2) Очевидно при отсутствии фазового сдвига между сигналами соседних посылок (если разность фаз 4 0) сумма проекций больще их разности, т. е. /Хи + Х„.,,-Хи-1/ ,,/. Если же разность фаз сигналов соседних посылок равна Т тогда разность проекций больще их суммы. Компаратор 38 сравнивает величины и и и 4 и вьщает на выход информационные символы. Таким образом, введение новых блоков значительно расщиряет частотный диапазон предлагаемого демодулятора сигналов с фазоразностной модуляцией. Формула изобретения Демодулятор сигналов с фазоразиост - модуляцией, содержащий генератор опорных сигналов, блок синхронизации и фильтры верхних частот, выходы которых соединены с соответствующими детекторами и входами фильтров нижних частот, выходы которых подключены к первым входам соответствующих блоков памяти, вторые входы которых соедщцены с выходами блока синхронизации, а также компаратор, входы которого соединены с вы- 79 ходами сумматоров, отличаю шийс я тем, что, с целью расширения частот ного диапазона, в него введены четыре дополнительных сумматора, четыре делителя мощности, три сумматора мощности, два инвертора и четыре выпрямителя, выходы которых подключены ко входам сумматоров, при этом выход генератора опорных сигналов соединен со входом первого делителя мощности, выходы которого соединены со входом второго делителя мощности и с первым входом первого сумматора мощности, второй вход которого со единен с первым выходом третьего делителя мощности, второй выход которого подключен ко входу четвертого делителя мощности, выходы которого соединены с первыми входами второго и третьего сумматоров мощности, вторые входы которых соединены с выходами второго- делителя мощности, а выходы сумматоров мощности подключены ко входам соответствующих фильтров верхних частот, причем первый вход первого блока памяти со- 7 единен со входом первого инвертора, выход которого подключен к первому входу первого дополнительного сумматора, второй вход которого соединен с выходом первого блока памяти и с первым входом второго дополнительного сумматора, вторЪй вход которого соединен со входом первого инвертора, выход второго блока памяти подключен к первым входам третьего и четвертого дополнительных сумматоров, вторые входы которых соединены соответственно с выходом и с входом второго инвертора, при этом выходы дополнительных сумматоров подключены ко входам соответствующих выпрямителей, а первый вход второго блока памяти соединен со входом второго инвертора. Источники информации, принятые во внимание при экспертизе 1. Заездный А. М и Окунев Ю, Б. Аппаратура передачи дискретной информации МС-5. М., Связь, 1970, с. 17 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Демодулятор сигналов с фазоразностной модуляцией | 1984 |

|

SU1216834A1 |

| СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛАМ ИМПУЛЬСНО-ФАЗОВОЙ РАДИОНАВИГАЦИОННОЙ СИСТЕМЫ | 1994 |

|

RU2079855C1 |

| Устройство для квазикогерентного приема фазоманипулированных сигналов | 1984 |

|

SU1239885A1 |

| Устройство для передачи и приема дискретных сигналов | 1987 |

|

SU1451872A1 |

| ИНФРАКРАСНЫЙ ТРЕХСПЕКТРАЛЬНЫЙ ИЗВЕЩАТЕЛЬ ПЛАМЕНИ | 2011 |

|

RU2443023C1 |

| ДЕМОДУЛЯТОР ФАЗОМАНИПУЛИРОВАННЫХ СИГНАЛОВ | 2008 |

|

RU2393641C1 |

| Устройство тактовой синхронизации | 1983 |

|

SU1107315A1 |

| Устройство для отображения телетекста на экране телевизионного приемника | 1980 |

|

SU1181568A3 |

| УСТРОЙСТВО ДЛЯ ИЗМЕРЕНИЯ КООРДИНАТ ВРАЩАЮЩЕГОСЯ РЕАКТИВНОГО СНАРЯДА | 1997 |

|

RU2122175C1 |

| Приемник многочастотных сигналов | 1985 |

|

SU1367170A1 |

Авторы

Даты

1982-07-23—Публикация

1980-07-11—Подача