Мантиссы п иисел

Знаки п чисел

Изобретение относится к вычисли- тельноГ технике и может быть использовано в яычислительном устройстве с п е ци ал и 31ф ов а и но г о пр о не с с ор а«

Цели изобретения - уирощение устройства «

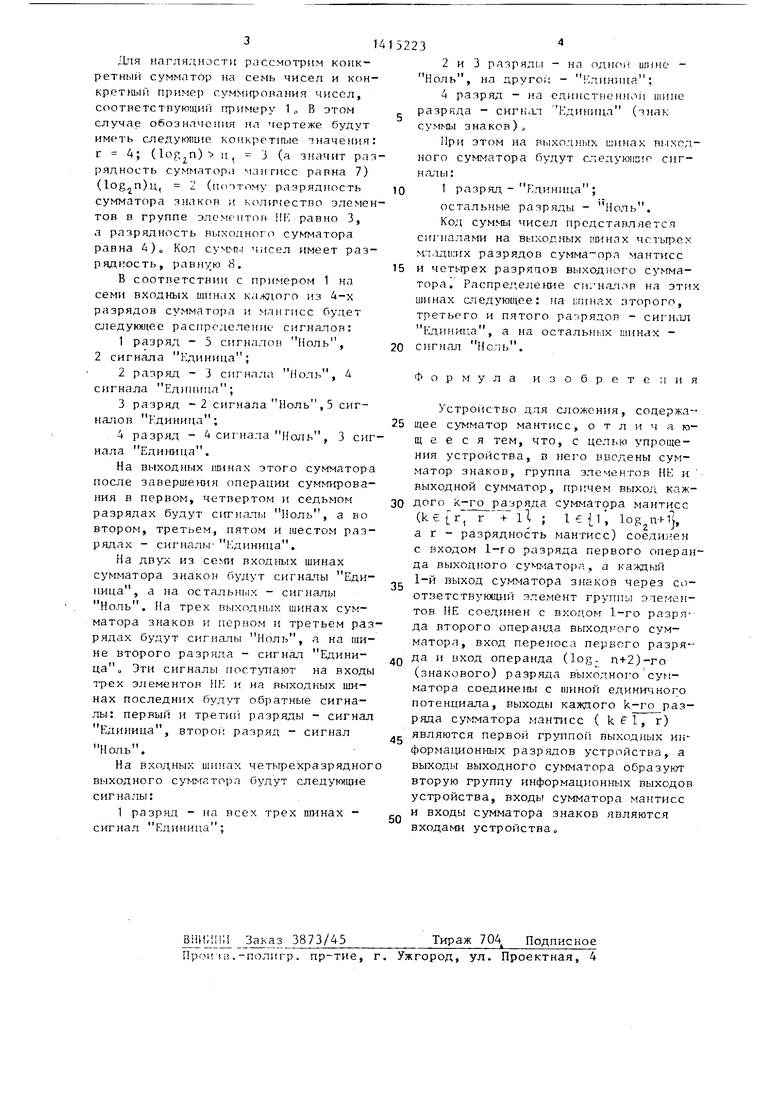

На чертеже представлена структурная схема устройства для сложения

Устройство для сложения содержит сумматор 1 мантией, сумматор 2 знаков, элементов ИР 3 и иыход- Hoi i cyNC iaTop А.

Сум(атор 1 мант1 сс построен по принципам, полностью соответствующим CTpyisType известного устройства.

Разрядность сумматора мантисс Оити что то же самое - разрядность кода суммы мантисс) равна r-(-()iJr. Разрядность сумматора знаков опре- де. гяется максимально возможным значением суммы знаков и равна ()ii;+ + 1 , а разрядность выходного сумматора превышает это значение на единицу (знаковый разряд для образования дополнительного кода суммы знаков). KojutnecTBo элементов в элементов НЕ соответствует количеству выходов сумматора знаков и равно (1ор,п)ц +1 о

В устройстве выход (ц+1)-го разряда cyNfMaTopa мантисс непосредственно и выход первого разряда сумматора знаков через элемент НЕ соединены с входами операвдов первого разряда выходного суммагора, вход переноса которого соединен с шиной един1гч- ного потенциала. Аналогично соединены ocTOJTbHbie (r+i)-e разряды сумматора мантисс и i-e разряды сумматора знаков с i-M разрядом выходного сумматора (i 1).

Единственный вход опера ща старшего (знакового) разряда выходного сумматора соединен с единичного потенциала. Полусумматор в старшем разряде выходного сумматора может быть заменен элементом НЕ, вход которого соединен с выходом переноса () ц+l -го разряда выходного cS MMaTopa (т.е. пр(;дшествую1цего кдад- шего разряда). Сигнал на выходе элемента НЕ в этом случае определяет знак кода суммы чисел.

Выходы г младших разрядов сумматора мантисс и выходы () ц+2 разрядов выходного сумматора (вес младшего из них равен весу (г+1)-го разряда) являются информационны

5

0

вык

выходами предлагаемого устройства; старший разряд этого кода является знаковым разрядом суммы чисел, остальные представляют мантиссу.

Количество выходных шин сумматора знаков практически всегда совпадает с количеством выходных шин сумматора мантисс, коммутируемых с входами ходно1 о сумматора, кроме случая где к - целое. В последнем случае сумматор знаков имеет на одну выходную шину больше и поэтому разряд, предшествующий знаковому разряду выходного сумматора, может быть выполнен на одном гголусумматоре и иметь всего один вход операнда. Это обстоятельство отражено на фиг.1 пунктирной линией, определяющей в данном случае соединение старшего разряда сумматора мантисс с выходным сумматором

П р и м е р U 0,5+0,,1875- 0,75-0,625+0,875+0,9375 1,375.

5

0

5

Мантиссы чисел

Сумма мантис чисел Дополнительный код суммы знаков Код суммы чисел с поряд;ком () Нормализованный код чисел с порядком 1

1000 0100 0011 0100 0110 1 10 1111 0110110.

1,110.

0,0010110.

0,1011.

40

II р и м е р 2. 0,5+0,25+0,1875- 0,75-0,625-0,875-0,,25.

5

0

5

Мантиссы чисел

Сумма мантис чисел Дополнительньп код суммы знаков Код суммы чисел с порядком () 3

Нормализованный код суммы чисел с поря;1- ком 1

Устройство работает с образомо

1000 0100 001 1 0100 0110 0010 0001 0011100.

1,100.

1,1011100.

1,01

11.

ггедующим

31

Для нагля/июсти рассмотрим конкретный сумматор на семь чисел и кон- крети 1Й пример сумм1фоваиия чисел, соответствующий примеру 1„ В этом случае обозначения ил чертеже будут иметь следуюпще конкретшле значения: г 4; () ц, 3 (а значит разрядность сумматор. 1ангисс равна 7) ()ц, 2 (тттому разрядность сумматора знаков и к(1Л1г(ество элементов в группе элем€ итон ПК равно 3, а разрядность выходного cyNfMaTopa равна 4) о Код су-оп, чисел имеет разрядность, рав) 8,

В соответстнии с примером 1 на семи входньЕХ шинах калдого из 4-х разрядов сумматора и мантисс будет следунхцее распределение сигналов:

1разряд - 5 сигналов Ноль, 2 сигнала Единица ;

2разряд - 3 сигнала Ноль, 4 сигнала Единица ;

3разряд - 2 сигнала Ноль,5 сигналов Единица ;

4разряд - 4 сиг нала Ноль, 3 сигнала Единица.

На выходных шинах этого сумматора после завершения операции суммуфова- ния в первом, четвертом и седьмом разрядах будут С1п нал1з1 Ноль, а во втором, третьем, пятом и шестом разрядах - сигналы- Единица,

На двух из семи входных шинах сумматора знаков будут сигналы Единица, а на остальн1 1х - сигналы Ноль. На трех выходных шинах сумматора знаков и nepiaoM и третьем разрядах будут сигналы Ноль, а на шине второго разряда - сигнал Единица Эти сигналы поступают на входы трех элементов НЕ и на выходных шинах последних будут обратньЕе сигналы: первый и третий разряды - сигнал Единица, второй разряд - сигнал

Ноль.

На входных шинах четырехразрядног выходного сумматора будут следуюш11е сигналы:

1 разряд - на всех трех шинах - сигнал Единица ;

3

2 и 3 разряд. - на о/июй ип)не - Ноль, на другой - Единица ;

4 разряд - на единственнои шине разряда - сигнал Единица (знак суммы знаков)

При этом на выход)ых шинах выходного сумматора будут с-едугоипю сиг- н ал ы: 1 разряд - Единица ;

остальные разряды - Ноль.

Код суммы чисел представляется сигналами на выходных ишнах четырех мл.1ди;их разрядов сумма ора мантисс и чстьфех разрядов выходного сумматора. Распределение сигналов на этих шинах следующее: на кпгнах второго, третьего и пятого разрядов - сигншт Едини11а, а на остальных шинах - сигнал io.nb.

Формула изобретения

Устройство для сложения, содержа-- щее су 1матор мантисс, о т л и ч а ю- щ е е с я тем, что, с целью упрощения устройства, в него введены сумматор знаков, группа элементов НЕ и выходной сумматор, причем выход каж- дого разряда сумматора мантисс (k е ll ; 1 Г, , а г - разрядность мантисс) соединен с входом 1-го разряда первого операнда выходного сумматора, а каждый 1-й выход сумматора знаков через соответствующий элемент группы элементов НЕ соединен с входом 1-го разряда второго onepafwa выходь ого сумматора, вход переноса первого разряда и вход операнда (log. п-ь2)-го (знакового) разряда в ыходного сумматора соединены с шиной единкчног о потенциала, выходы каждого ряда сумматора мантисс ( kel, г)

являются первой группой выходных И1Г

фор)ащ1онных разрядов устройства, а выходы выходного сумматора образуют вторую группу информационных выходов устройства, входы сумматора мантисс и входы сумматора знаков являются входами устройствар

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для выравнивания порядков чисел | 1982 |

|

SU1030798A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| ВЫЧИСЛИТЕЛЬНОЕ УСТРОЙСТВО для ПЕРЕРАБОТКИ ЧИСЛОВОЙ И БУКВЕННОЙ ИНФОРМАЦИИ | 1969 |

|

SU255656A1 |

| АРИФМЕТИЧЕСКИЙ ВЫЧИСЛИТЕЛЬ | 2004 |

|

RU2292580C2 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| ОПТИЧЕСКИЙ ЦИФРОВОЙ СТРАНИЧНЫЙ ДЕЛИТЕЛЬ С ПЛАВАЮЩЕЙ ТОЧКОЙ | 1998 |

|

RU2130639C1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1986 |

|

SU1411742A1 |

Изобретение относится к вычислительной технике. Предназначено для одновременного параллельного суммиМантисса суммы п чисел рования п двоичных чисел (п.2), отрицательные числа задаются дополнительными кодами с одним знаковым разрядом. Цель изобретения - упрощение устройства. Устройство позволяет сократить оборудование при суммировании п чисел за счет того, что на нем суммируются раздельно мантиссы чисел и их знаковые разряды, окончательный результат получается вычитанием кода суммы знаков чисел из кода суммы мантисс чисеЛа Для этого в устройство, кроме многовходового сумматора 1 мантисс, введены сумматор 2 знаков, группа элементов НЕ 3 и выходной сумматор 4. 1 ил„ Знак суммы л (Л

| Путинцев Н.Д | |||

| Аппаратный контроль управляющих пяфровых вычислительных машин | |||

| - М.: Энергия, 1968, с.55-63, рис.11 ,10 и 11.12 | |||

| Многовходовое суммирующее устровйство | 1971 |

|

SU455341A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-08-07—Публикация

1986-10-09—Подача