1

Изобретение относится к цифровой магнитной записи и может быть применено в системах памяти для сопряжения с внешними накопителями, выполненными на подвижных магнитных носителях, -например магнитных дисках, гибких магнитных дисках, гибких магнитных мини-дисках, магнитных лентах и т.д.

Целью изобретения является расширение функциональных возможностей устройства за счет обеспечения возможности диагностики работоспособности как всего устройства, так и его основных блоков и функциональных элементов.

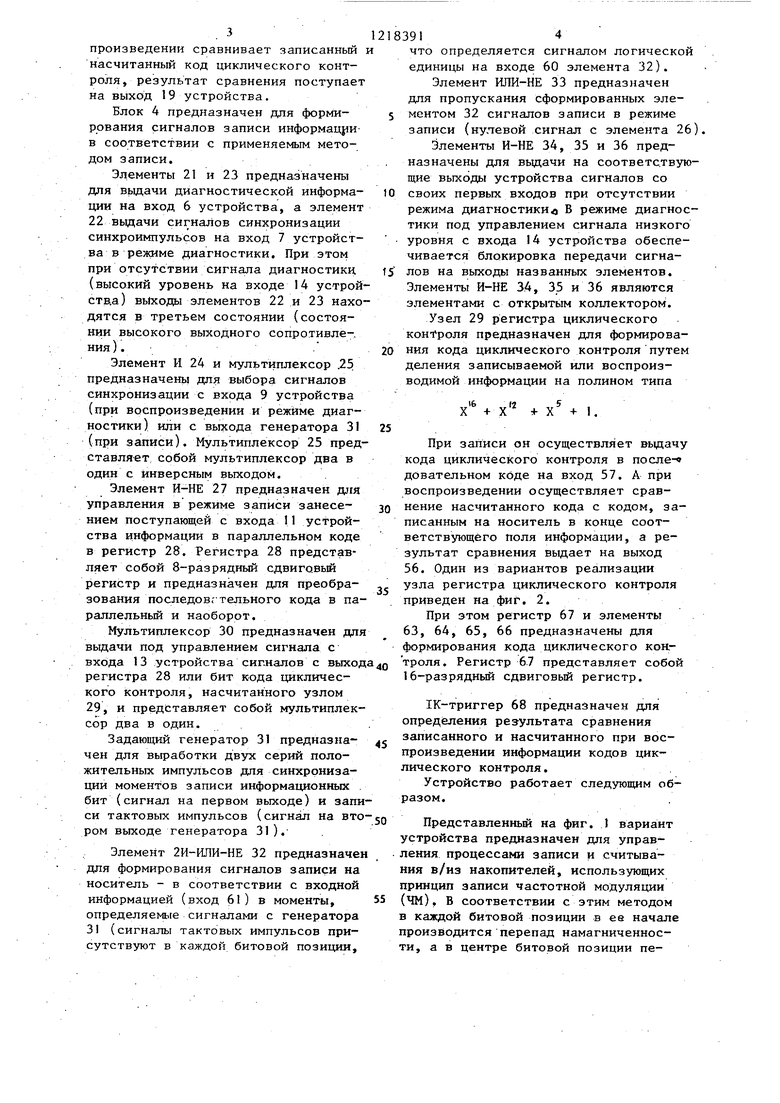

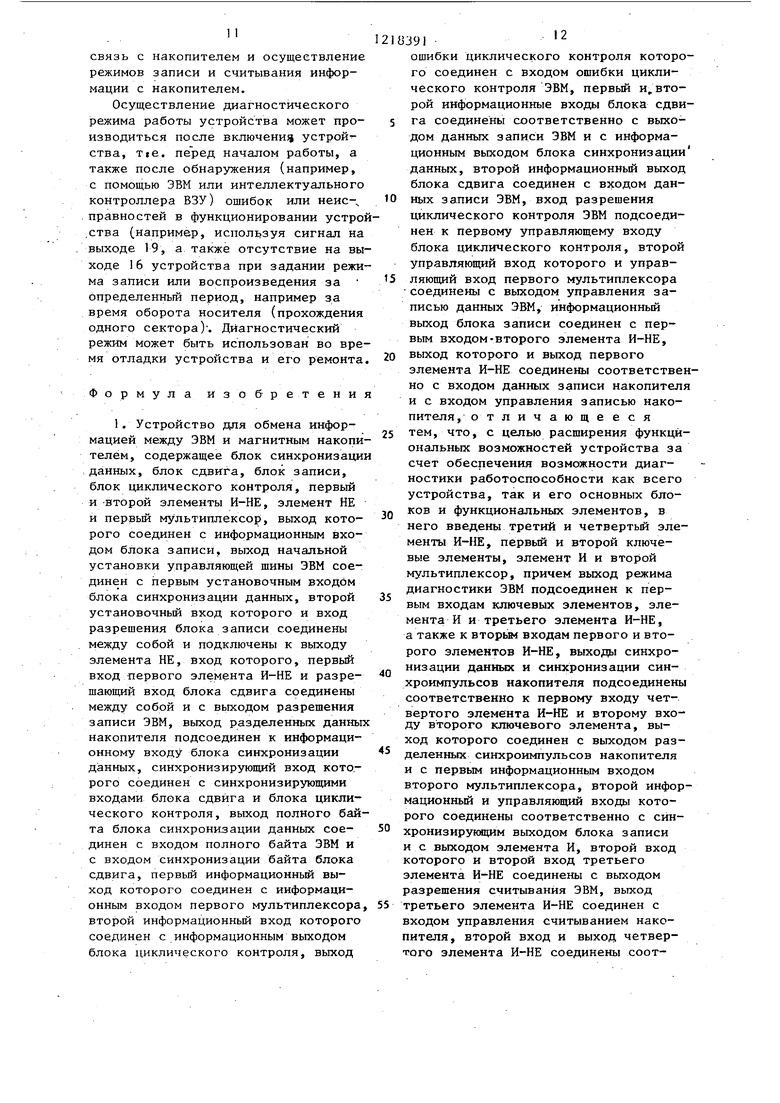

На фиг. 1 приведена схема устройства; на фиг. 2 - схема узла регистра циклического контроля; на фиг.З - схема блока синхронизации данных. . . Устройство содержит блок 1 снн-- хронизации данных, блок 2 сдвига, блок 3 циклического контроля, блок 4 записи, вход 5 начальной установки

йход 6 разделенных данных, вход 7 синхронизации данных вход 8 синхронизации синхроимпульсов, вход 9 разделенных синхроимпульсов, вход 10 разрешения записи, вход 11 данных записи, вход 12 разрешения работы циклического контроля, вход 13 управления записью данных, вход 1А режима диагностики, вход 15 разрешення считывания устройства, выход 16 полного байта, выход 17 управления записи выход 18 данных записи, выход 19 ошибки циклического Контроля, выход

20управления считыванием, четвертый

21элемент И-НЕ, второй 22 и первый 23 ключевые элементы, элемент И 24, мультиплексор 25, элемент НЕ 26j пятый элемент И-НЕ 27, регистр 28 сдвига, узел 29 регистра циклического контроля, второй мультиплексор 30,

.задающий генератор 31, элемент 2И- ИЛИ-НЕ 32, элемент ИЛИ-НЕ 33, первый 34, второй 35, четвертый 36 элементы Н-НЕ.

Кроме.того, на фиг. 1 обозначены 37, 38, 39, 40, 41, 42 соответственно первый установочный, информационный, второй установочный, синхронизирующий входы и информационней и полного байта выходы блока синхронизации данных; 43, 33, 45, 46 соответственно синхронизирующий, второй и первый инфорьигционные и управляющи входы регистра 28, а 47, 48 соответ12

ственно второй и первьй информационные выходы регистра 28; 49, 50 и 51 соответственно первый, второй и управляющий входы мультиплексора 25;

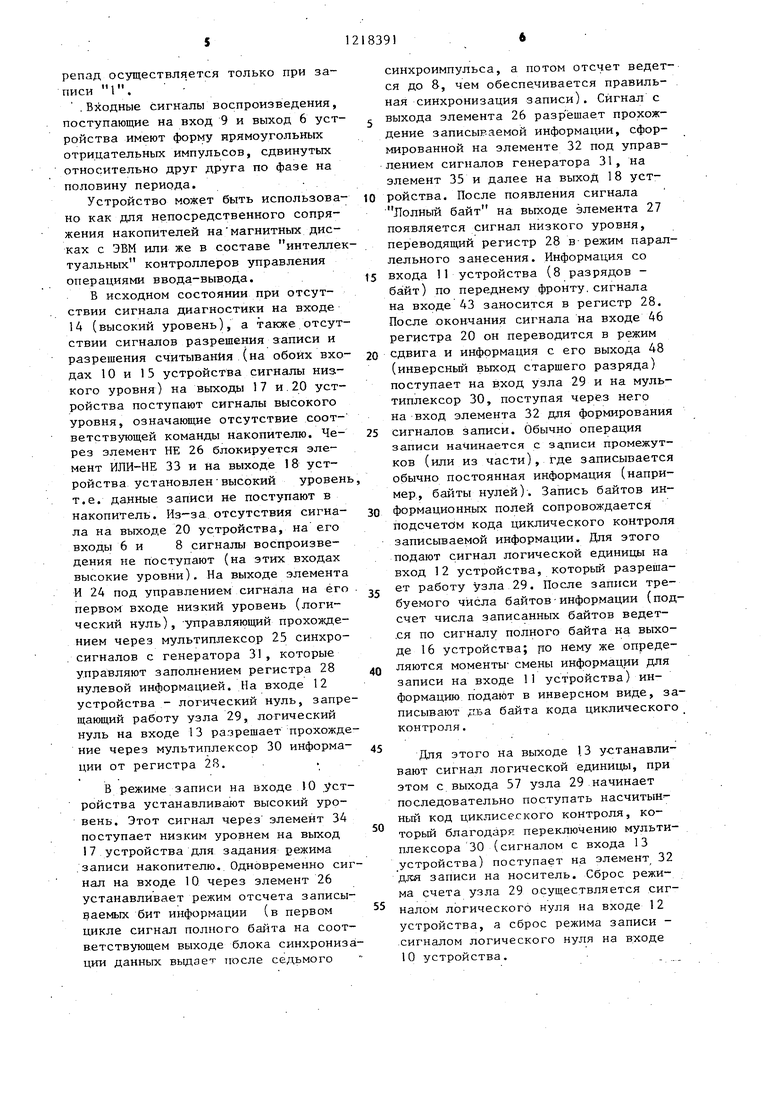

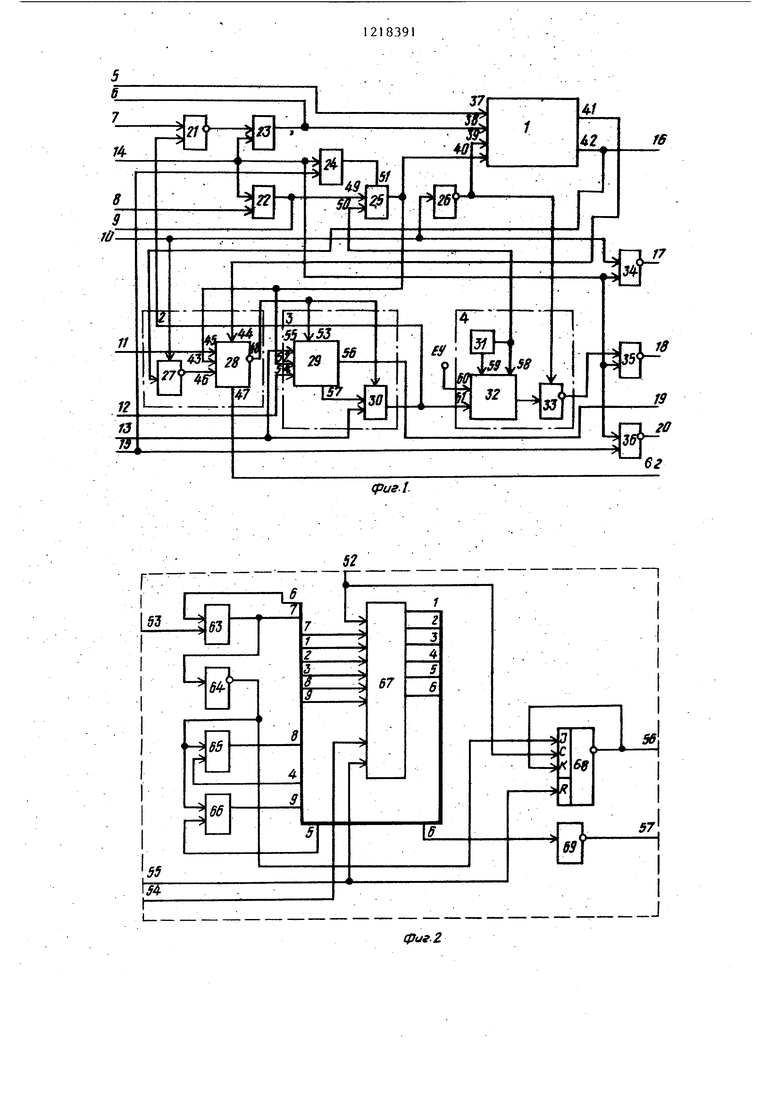

52, 53, 5.4, 55 соответственно синхронизирующий, и формационньй, первый и второй управляюиц1е входы узла 29 и 56, 57 соответственно выход ошибки циклического контроля и информационньй выход узла 29; 5в,-59, 60, 61 соответственно третий, четвертый и первьй входы элемента 2И-ИЛИ-НЕ 32; 62 - выход данных воспроизведения. На .фиг, 2 изображены 52, 53, 54,

55 соо.тветственно синхронизирующий, информационньй, первьй и второй управляющие входы и.56, 57 соответственно выход Ошибки циклического контроля и информационньй выход узла

регистра циклического контроля. Первьй элемент неравнозначности 63, первьй элемент НЕ 64, второй 65, третий 66 элементь неравнозначности, регистр 67 сдвига, . ЗК-триггер 68,

второй элемент НЕ 69.

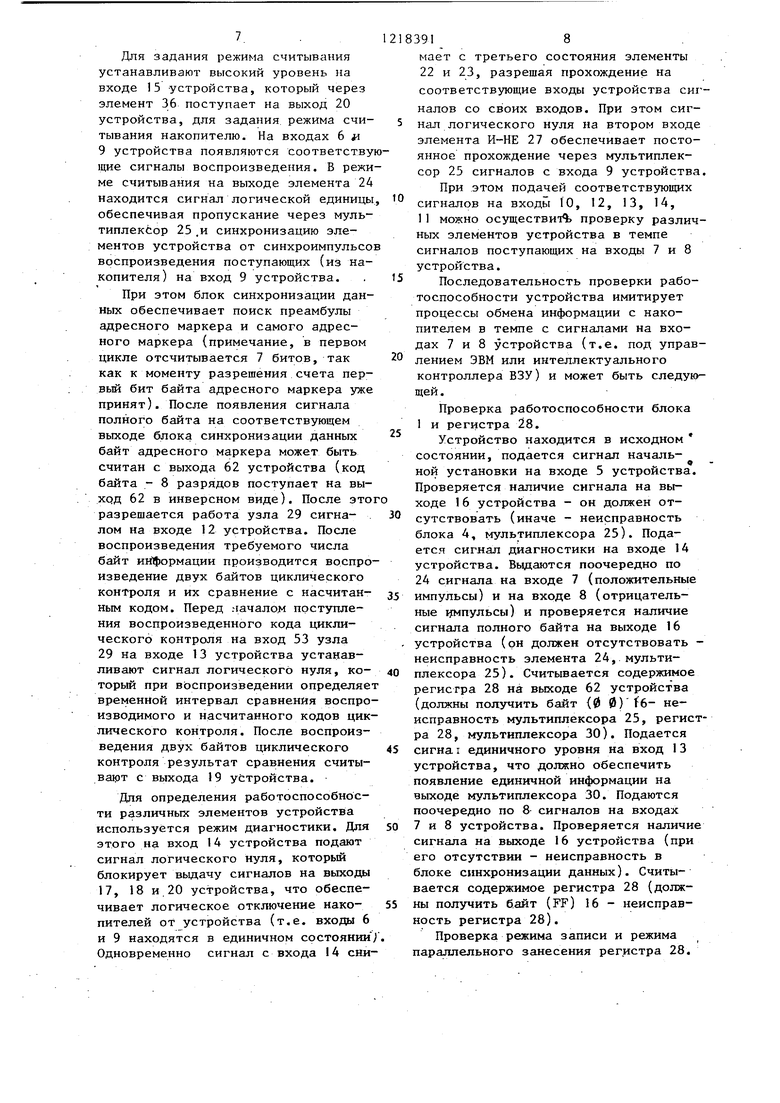

На фиг. 3 изображены первьй триггер 70, счетчик 71, элемент .И-НЕ 72, второй триггер 73, регистр 74, элё- мент ИЛИ-НЕ 75. . БЛОК 1 синхронизации данных предназначен для выбора сигналов синхро.- низадии элементов блочка 1, блоков 2 и 3. При этом при записи информации на носитель он осуществляет подсчет

числа записанных бит информации. При воспроизведении блок 1 осуществляет поиск преамбулы и начала адресного маркера на носителе, после обнаружения которых осуществляет подсчет

числа воспроизведенных бит информации . .

Блок 2 предназначен при записи для преобразования параллельного кода инфорь1ации с входа 11 устройства в последовательньй код информации, которая через мультиплексор 30 поступает в блок 4 для записи на носитель и вход элемента И-НЕ 21 для осуществления режима диагностики.

При воспроизведении блок 2 осуществляет преобразование воспроизводимой в последовательном коде инфор- в параллельньй код, которьй поступает на выход 62 устройства.

Блок 3 предназначен для подсчета кода циклического контроля. При этом при записи он В1)1дает насчитан- ньй код на вход блока 4, а при воепроизведении сравнивает записанный и насчитанный код циклического контроля, результат сравнения поступает на выход 19 устройства.

Блок 4 предназначен для формирования сигналов записи информац 1И- в соответствии с применяемым методом записи.

Элементы 21 и 23 предназначены для вьщачи диагностической информации на вход 6 устройства, а элемент 22 вьщачи сигналов синхронизации синхроимпульсов на вход 7 устройства в режиме диагностики. При этом при отсутствии сигнала диагностики (высокий уровень на входе 14 устрой- ств.а) выходы элементов 22 и 23 находятся в третьем состоянии (состоянии высокого выходного сопротивле-. ния)..

Элемент И 24 и мультиплексор .25 предназначены для выбора сигналов синхронизации с входа 9 устройства (при воспроизведении и режиме диагностики) или с выхода генератора 31 (при записи). Мультиплексор 25 представляет собой мультиплексор два в один с инверсным выходом. .

Элемент И-НЕ 27 предназначен для управления в режиме записи занесением поступающей с входа II устройства информации в параллельном коде в регистр 28. Регистра 28 представляет собой 8-разрядный сдвиговый регистр и предназначен для преобразования последов. тельного кода в параллельный и наоборот.

Мультиплексор 30 предназначен для вьщачи под управлением сигнала с

10

Г5

20

что определяется сигналом логической единицы на входе 60 элемента 32).

Элемент ИПИ-НЕ 33 предназначен для пропускания сформированных элементом 32 сигналов записи в режиме записи (нулевой сигнал с элемента 26

Элементы И-НЕ 34, 35 и 36 предназначены для вьщачи на соответствую щие выходы устройства сигналов со своих первых входов при отсутствии режима диагностикио В режиме диагнос тики под управлением сигнала низкого уровня с входа 14 устройства обеспечивается блокировка передачи сигналов на выходы названных элементов. Элементы И-НЕ 34, 35 и 36 являются элементами с открытым коллектором.

Узел 29 регистра циклического контроля предназначен для формирования кода циклического контроля путем деления записываемой или воспроизводимой информации на полином типа

|& f X + X

+

Х%

1.

25

30

35

При записи он осуществляет вьщачу кода циклического контроля в после-« довательном коде на вход 57. А при воспроизведении осуществляет сравнение насчитанного кода с кодом, записанным на носитель в конце соответствующего поля информации, а результат сравнения выдает на выход 56. Один из вариантов реализации узла регистра циклического контроля приведен на фиг. 2.

При этом регистр 67 и элементы 63, 64, 65, 66 предназначены для формирования кода циклического конвхода 13 устройства сипналов с выходадо троля. Регистр 67 представляет собой

регистра 28 или бит кода циклического контроля, насчитанного узлом 29, и представляет собой мультиплексор два в один.

Задающий генератор 31 предназна- 5 чен для выработки двух серий положительных импульсов дпя синхронизации моментов записи информационных . бит (сигнал на первом выходе) и записи тактовых Импульсов (сигнал на BTO-JQ ром выходе генератора 31).

Элемент 2И-ИЛИ-НЕ 32 предназначен для формирования сигналов записи на носитель - в соответствии с входной информацией (вход 61) в моменты, 55 определяемые сигналами с генератора 31 (сигналы тактовых импульсов присутствуют в каждой битовой позиции.

16-разрядный сдвиговый регистр.

1К-триггер 68 предназначен для определения результата сравнения записанного и насчитанного при воспроизведении информации кодов циклического контроля.

Устройство работает следующим образом.

Представленный на фиг. 1 вариант устройства предназначен для управления процессами записи и считывания в/из накопителей, использующих принцип записи частотной модуляции (ЧМ), В соответствии с этим методом в каждой битовой позиции в ее начале производится перепад намагниченности, а в центре битовой позиции пе

что определяется сигналом логической единицы на входе 60 элемента 32).

Элемент ИПИ-НЕ 33 предназначен для пропускания сформированных элементом 32 сигналов записи в режиме записи (нулевой сигнал с элемента 26).

Элементы И-НЕ 34, 35 и 36 предназначены для вьщачи на соответствующие выходы устройства сигналов со своих первых входов при отсутствии режима диагностикио В режиме диагностики под управлением сигнала низкого уровня с входа 14 устройства обеспечивается блокировка передачи сигналов на выходы названных элементов. Элементы И-НЕ 34, 35 и 36 являются элементами с открытым коллектором.

Узел 29 регистра циклического контроля предназначен для формирования кода циклического контроля путем деления записываемой или воспроизводимой информации на полином типа

f X

+

Х%

1.

0

5

При записи он осуществляет вьщачу кода циклического контроля в после-« довательном коде на вход 57. А при воспроизведении осуществляет сравнение насчитанного кода с кодом, записанным на носитель в конце соответствующего поля информации, а результат сравнения выдает на выход 56. Один из вариантов реализации узла регистра циклического контроля приведен на фиг. 2.

При этом регистр 67 и элементы 63, 64, 65, 66 предназначены для формирования кода циклического контроля. Регистр 67 представляет собой

16-разрядный сдвиговый регистр.

1К-триггер 68 предназначен для определения результата сравнения записанного и насчитанного при воспроизведении информации кодов циклического контроля.

Устройство работает следующим образом.

Представленный на фиг. 1 вариант устройства предназначен для управления процессами записи и считывания в/из накопителей, использующих принцип записи частотной модуляции (ЧМ), В соответствии с этим методом в каждой битовой позиции в ее начале производится перепад намагниченности, а в центре битовой позиции перепад осуществляется только при записи 1.

.Входные сигналы воспроизведения, поступающие на вход 9 и выход 6 уст ройства имеют форму прямоугольных отрицательных импульсов, сдвинутых относительно друг друга по фазе на половину периода.

Устройство может быть использова но как для непосредственного сопряжения накопителей на магнитных дисках с ЭВМ или же в составе интеллетуальных контроллеров управления операциями ввода-вывода.

Б исходном состоянии при отсутствии сигнала диагностики на входе 14 (высокий уровень), а также отсутствии сигналов разрешения записи и разрешения считывания (на обоих вхо дах 10 и 15 устройства сигналы низкого уровня) на выходы 17 и.20 устройства поступают сигналы высокого уровня, означающие отсутствие соответствующей команды накопителю. Че- рез элемент НЕ 26 блокируется элемент ИЛИ-НЕ 33 и на выходе 18 устройства установлен высокий уровен т.е. данные записи не поступают в накопитель. Из-за отсутствия сигна- ла на выходе 20 устройства, на его входы 6 и 8 сигналы воспроизведения не поступают (на этих входах высокие уровни). На выходе элемента И 24 под управлением сигнала на его первом входе низкий уровень (логический нуль), управляющий прохождением через мультиплексор 25 синхро- . сигналов с генератора 31, которые управляют заполнением регистра 28 нулевой информацией. На входе 12 устройства - логический нуль, запрещающий работу узла 29, логический нуль на входе 13 разрешает прохождение через мультиплексор 30 информа- ции от регистра 28.

В режиме записи на входе Ю устройства устанавливают высокий уровень. Этот сигнал через элемент 34 поступает низким уровнем на выход 17 устройства для задания режима .записи накопителю. Одновременно сигнал на входе 10 через элемент 26 устанавливает режим отсчета записываемых бит информации (в первом цикле сигнал полного 6afiTa на соответствующем выходе блока синхронизации данных выдает после седьмого

синхроимпульса, а потом отсчет ведется до В, чем обеспечивается правильная синхронизация записи). Сигнал с выхода элемента 26 разр ёшает прохождение записываемой информации, сформированной на элементе 32 под управлением сигналов генератора 31, на элемент 35 и далее на выход 18 устройства. После появления сигнала Лолный байт на выходе элемента 27 появляется сигнал низкого уровня, переводящий регистр 28 в- режим параллельного занесения. Информация со входа 11 устройства (8 разрядов - байт) по переднему фронту.сигнала на входе 43 заносится в регистр 28. После .окончания сигнала на входе 46 регистра 20 он переводится в режим сдвига и информация с его выхода 48 (инверсный выход старшего разряда) поступает на вход узла 29 и на мультиплексор 30, поступая через него на вход элемента 32 для формирования сигналов записи. Обычно операция записи начинается с за,писи промежутков (или из части), где записывается обычно постоянная инфо.рмация (например, байты нулей). Запись байтов информационных полей сопровождается подсчетом кода циклического контроля записываемой информации. Для этого подают сигнал логической единицы на вход 12 устройства, которьш разрешает работу Узла 29. После записи требуемого числа байтов-информации (подсчет числа записанных байтов ведет- .ся по сигналу полного байта на выходе 16 устройства; по нему же определяются моменты- смены информации для записи на входе 11 устройства) информацию подают в инверсном виде, записывают два байта кода циклического контроля.

Для этого на выходе 13 устанавливают сигнал логической единицы, при этом с выхода 57 узла 29 начинает последовательно поступать насчитын- ный код циклисе.ского контроля, которьш благодаря переключению мультиплексора 30 (сигналом с входа 13 устройства) поступает на элемент 32 ддш записи на носитель. Сброс режима счета узла 29 осуществляется сигналом логического нуля на входе 12 устройства, а сброс режима записи - сигналом логического нуля на входе 10 устройства.

7. . Для задания режима считывания устанавливают высокий уровень на входе 15 устройства, который через элемент 36 поступает на выход 20 устройства, для задания режима счи- тывания накопителю. На входах 6 л 9 устройства появляются соответствущие сигналы воспроизведения. В режиме считывания на выходе элемента 2А находится сигнал логической единицы обеспечивая пропускание через мультиплексор 25 .и синхронизацию элементов устройства от синхроимпульсо воспроизведения поступающих (из накопителя) на вход 9 устройства. .

При этом блок синхронизации данных обеспечивает поиск преамбулы адресного маркера и самого адресного маркера (примечание, в первом цикле отсчитывается 7 битов, так как к моменту разрешения счета первый бит байта адресного маркера уже принят). После появления сигнала полного байта на соответствующем выходе блока синхронизации данных байт адресного маркера может быть считан с выхода 62 устройства (код байта - 8 разрядов поступает на выход 62 в инверсном виде). После это разрешается работа узла 29 сигна- . лом на входе 12 устройства. После воспроизведения требуемого числа байт ин формации производится воспроизведение двух байтов циклического контроля и их сравнение с насчитан- ным кодом. Перед гачало 1 поступления воспроизведенного кода циклического контроля на вход 53 узла 29 на входе 13 устройства устанавливают сигнал логического нуля, ко- торый при воспроизведении определяет временной интервал сравнения воспроизводимого и насчитанного кодов циклического контроля. После воспроизведения двух байтов циклического контроля результат сравнения считы- BaipT с выхода 19 устройства.

Для определения работоспособности различных элементов устройства используется режим диагностики. Для этого на вход 14 устройства подают сигнал логического нуля, который блокирует выдачу сигналов на выходы 17, 18 и 20 устройства, что обеспечивает логическое отключение нако- пителей от устройства (т.е. входы 6 и 9 находятся в единичном состоянии Одновременно сигнал с входа 14 сни3918

мает с третьего состояния элементы 22 и 23, разрешая прохождение на соответствующие входы устройства си1 - налов со своих входов. При этом сигнал логического нуля на втором входе элемента И-НЕ 27 обеспечивает постоянное прохождение через мультиплексор 25 сигналов с входа 9 устройства.

При этом подачей соответствуюш11х сигналов на входы 10, 12, 13, 14, 11 можно осуществит проверку различных элементов устройства в темпе сигналов поступающих на входы 7 и 8 устройства.

Последовательность проверки работоспособности устройства имитирует процессы обмена информации с накопителем в темпе с сигналами на входах 7 и 8 устройства (т.е. под управлением ЭВМ или интеллектуального контроллера ВЗУ) и может быть следующей.

Проверка работоспособности блока 1 и регистра 28.

Устройство находится в исходном состоянии, подается сигнал начальной установки на входе 5 устройства. Проверяется наличие сигнала на выходе 16 устройства - он должен отсутствовать (иначе - неисправность блока 4, мультиплексора 25). Подается сигнал диагностики на входе 14 устройства. Вьщаются поочередно по 24 сигнала на входе 7 (положительные импульсы) и на входе 8 (отрицательные импульсы) и проверяется наличие сигнала полного байта на выходе 16 устройства (он должен отсутствовать - неисправность элемента 24, мультиплексора 25). Считывается содержимое регистра 28 на выходе 62 устройства (должны получить байт {0 0) f6- неисправность мультиплексора 25, регистра 28, мультиплексора 30). Подается сигна I единичного уровня на вход 13 устройства, что должно обеспечить появление единичной информации на выходе мультиплексора 30. Подаются поочередно по 8 сигналов на входах 7 и 8 устройства. Проверяется наличие сигнала на выходе 16 устройства (при его отсутствии - неисправность в блоке синхронизации данных). Считывается содержимое регистра 28 (должны получить б.айт (FF) 16 - неисправность регистра 28).

Проверка режима записи и режима араллельного занесения регистра 28.

Сбрасывается сигнал на входе 13 устройства и выдается сигнал начальной установки на входе 5 устройства,. Подается сигнал единичного уровня на вход 10 устройства. Выдается по 7 си налов на входы 7 и 8 устройства - должен появиться сигнал полного байта на выходе 16 устройства (иначе неисправность блока синхронизации данных). Выст авляется байт (8 рязря- дов) эталонной информации на входе 11 устройства и выдается сигнал на входе 8 устройства. Считанный байт информации с выхода 62 должен совпасть с эталонным (иначе - неисправ- ность элемента 27, регистра 28).

Проверка работоспособности узла циклического контроля. Устанавливается режим записи, выдачей сигналов на входах 7 и 8 устройства получают сигнал полного байта на выходе 16. устройства. Выставляют байт эталонной информации на входе 11 и сигналом на входе 8 записывают его в регистр 28. Подачей сигнала логичес- кой единицы на вход 12 устройства включают в работу узел 29. Путем подачи сигналов на входы 7 и 8 устройства записывают в диагностическом режиме определенное количество байтов эталонной информации. После записи в регистр 28 первого байта эталонного кода циклического контроля устанавливают сигнал единичного уровня на входе 13 устройства, обес печивая режим сравнения эт.алонного и насчитанного кода циклического контроля. После записи в регистр 28 второго байта эталонного кода циклического контроля и его сравнения в узле 29 с насчитанным проверяют наличие ошибки контроля на выходе 19 устройства (при ошибке - неисправность регистра 67, элементов 63. 64 или 1К-триггёра 68 узла 29). В регистре 67 при правильной работе должны находиться единицы во всех разрядах. Это может быть проверено путем сброса режима записи и последовательной переписи (вьщачей сигна лов на входы 7 и 8 устройства) содержимого регистра 67 в регистр 28 (должны получить.на выходе 62 устройства два байта (00.) 16).

Устройство допускает и другой алгоритм проверки насчитанного кода циклического контроля, при котором после записи последнего байта эталонной информации в регистр 28 сбрасывается режим записи, а после преобразования байта в регистре 28 в последовательный код устанавливается сигнал единичного уровня на входе 13 и насчитанный код циклического контроля может быть переписан в регистр 28 и считан с выхода 62 . устройства для сравнения его с эталонным.

Узел 29 (см.фиг. 2) работает следую1чим образом. Особенностью узла 29 является то, что он максимально использует особенности существующей элементной базы. Так как подсчет кода циклического контроля ведется в обратном коде, то перед началом работы во все его разряды заносятся нули, что осуществляется низким уровнем на входе 12 устройства.

Подсчет кода циклического контроля осуществляется при сигнале логической единицы на входе 12 устройства в режиме параллельного занесения. Синхронизация работы регистра 67 и триггера 68 осуществляется синхросигналами с входа мультиплексора 25. Для записи насчитанного кода на носитель подают уровень логической единицы на вход 13 устройства, который переводит регистр 67 в ре- жим сдвига,

Сравнение насчитанного и воспроизводимого кода циклического контроля осуществляется при единичном сигнале на входе 13, который разрешает работу 1К-триггера 68, При этом сравнение осуществляет элемент 63 (при сравнении кодов, учитывая, что в регистре 67 код насчитывается в инверсном виде, на выходе элемента 63 появляется сигнал логической единицы, который через элемент НЕ 64 поступает на 3-вход триггера 68). Если возникло несравнение, то перебрасывается в единичное состояние ТК-уриг гер 68, который фиксирует ошибку циклического контроля. Сброс 1К-тригге- ра осуществляется после сравнения всего кода циклического контроля (16 бит, т.е. появления двух сигналов на выходе 16 устройства) сигналом на входе 13 устройства.

После осуществления диагностического режима устанавливают сигнал логической единицы на входе 14 устройства, разрешающего логическую

связь с накопителем и осущеетвление режимов записи и считывания информации с накопителем.

Осуществление диагностического режима работы устройства может производиться после включени устройства, Tie. перед началом работы, а также после обнаружения (например, с помощью ЭВМ или интеллектуального контроллера ВЗУ) ошибок или неис- правностей в функционировании устрой ,ства (например, используя сигнал на выходе 19, а также отсутствие на выходе 16 устройства при задании режима записи или воспроизведения за определенньгй период, например за время оборота носителя (прохождения одного сектора)-. Диагностический режим может быть использован во время отладки устройства и его ремонта

Формула изобретения

1. Устройство для обмена информацией между ЭВМ и магнитным накопителем, содержащее блок синхронизации данных, блок сдвига, блок записи, блок циклического контроля, первый и -второй элементы И-НЕ, элемент НЕ и первый мультиплексор, выход которого соединен с информационным входом блока записи,, выход начальной установки управляющей шины ЭВМ соединен с первым установочным входом блока синхронизации данных, второй установочный вход которого и вход разрешения блока записи соединены между собой и подключены к выходу элемента НЕ, вход которого, первый вход -первого элемента Й-НЕ и разрешающий вход блока сдвига соединены между собой и с выходом разрешения записи ЭВМ, выход разделенных данных накопителя подсоединен к информационному входу блока синхронизации данных, синхронизирующий вход которого соединен с синхронизирующими входами блока сдвига и блока циклического контроля, выход полного байта блока синхронизации данных соединен с входом полного байта ЭВМ и с входом синхронизации байта блока сдвига, первый информационный выход которого соединен с информационным входом первого мультиплексора, второй информационный вход которого соединен с информационным вькодом блока циклического контроля, выход

218391

ошибки циклического контроля которого соединен с входом ошибки циклического контроля ЭВМ, первый и,второй информационные входы блока сдви- 5 га соединены соответственно с выходом данных записи ЭВМ и с информационным выходом блока синхронизации данных, второй информационный выход блока сдвига соединен с входом дан- 10 ных записи ЭВМ, вход разрешения

циклического контроля ЭВМ подсоединен к первому управляющему входу блока циклического контроля, второй управляющий вход которого и управ15 ляющий вход первого мультиплексора соединены с выходом управления записью данных ЭВМ, информационный выход блока записи соединен с первым входом-второго элемента И-НЕ, 20 выход которого и выход первого

элемента И-НЕ соединены соответственно с входом данных записи накопителя и с входом управления записью накопителя, отличающееся 25 тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения возможности ностики работоспособности как всего устройства, так и его основных бяо- JQ ков и функциональных элементов, в него введены третий и четвертьй элементы И-НЕ, первый и второй ключевые элементы, элемент И и второй мультиплексор, причем выход режима диагностики ЭВМ подсоединен к первым входам ключевых элементов, элемента И и третьего элемента И-НЕ, а также к втор№4 входам первого и второго элементов И-НЕ, выходы синхро- .Q низации данных и синхронизации синхроимпульсов накопителя подсоединены соответственно к первому входу четвертого элемента И-НЕ и второму входу второго ключевого элемента, выход которого соединен с выходом раз- деленных синхроимпульсов накопителя и с первым информационном входом второго мультиплексора, второй информационный и управляюнщй входы которого соединены соответственно с син- 0 хронизирукидим выходом блока записи и с выходом элемента И, второй вход которого и второй вход третьего элемента И-НЕ соединены с выходом разрешения считывания ЭВМ, выход 5 третьего элемента И-НЕ соединен с входом управления считыванием накопителя, второй вход и выход четвертого элемента И-НЕ соединены соот5

петствеино с ныходом первого мультиплексора и с вторым входом первог ключевого элемента, выход которого подсоединен к информационному входу блока синхронизации данных, вход синхронизации которого подсоединен к выходу второго мультиплексора.

2, Устройство по п. 1, о т л и- чающееся тем, что блок циклического контроля содержит первьй, второй и третий элементы неравнозначности, 1К-триггер, первый, второй элементы НЕ и регистр сдвига, при этом вход данных узла регистра циклического контроля соединен с первым входом первого элемента неравнозначности, выход которого соединен с первым информационным входом регистра сдвига и через первый элемент НЕ - с первыми входами вторго и третьего элементов неравнозначности, первьй, второй и третий информационные выходы регистра сдвига соединены соответственно с вторым, третьим и четвертым информационными входами регистра сдвига, четвертьй, пятьй и шестой информационные выходы регистра сдвига соединены соответственно с вторыми входами второго, третьего и первого элементов неравнозначности, выходы второго и третьего элементов неравнозначности подсоединены соответственно к пятому и к шестому информационным входам регистра сдвига, вход сброса и шестой информационньй выход которого соединены соответственно с управляющим входом узла регистра циклического контроля и через второй элемент НЕ - с выходом данных узла регистра циклического контроля, вход синхронизации которого соединен с синхронизирующим входом регистра сдвига, вход сброса 1К-триггера подсоединен к второму управляющему входу узла регист18391. .

ра циклического контроля и к входу разреш;ения сдвига регистра сдвига, выход первог;о элемента НЕ подсоединен к 1-входу 1К-триггера, К-вход 5 и инверсный выход которого соединены между собой и с выходом ошибки циклического контроля узла, синхронизирующий вход которого соединен с синхронизирующим входом 1К-триггера. 10

3. Устройство по п, 1, о т л и- чающееся тем, что.блок синхронизации данных содержит первьй и второй триггеры, счетчик, регистр, 5 элемент И-НЕ и элемент ИЛИ-НЕ, причем синхронизирующий вход блока синхронизации данных соединен с синхронизирующими входами первого триггера, счетчика и регистра, выход стар20 щего разряда которого соединей с информационным входом регистра и с первым входом элемента ИЛИ-НЕ, второй вход и выход которого соединены соответственно с выходом предпослед- 5 него разряда регистра и с выходом полного байта блока синхронизации данных, установочный вход регистра соединен с прямым вькодом второго триггера, информационный вход кото- 0 рого соединен с вторым установочным входом блока синхронизации данных, первьй установочный вход которого соединен с входами сброса счетчика и второго триггера, информационный

5 вход блока синхронизации данных соединен с информационным входом первого триггера, прямой выход которого соединен с первым входом элемента И-НЕ, второй вход и выход кото0 рого соединены соответственно с выходом переполнения счетчика и с синхронизирующим входом второго триггера, ичверсньй выход первого триггера соединен с входом загрузки счетчика

5 и с информационным вьпсодом блока синхронизации данных.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода измерительной информации | 1986 |

|

SU1354179A1 |

| Устройство для управления обменом информацией накопителя на магнитной ленте с электронно-вычислительной машиной | 1983 |

|

SU1128245A1 |

| Устройство для сопряжения внешних устройств с накопителем на магнитной ленте | 1984 |

|

SU1348842A1 |

| Способ многодорожечной цифровой магнитной записи и устройство для его осуществления | 1990 |

|

SU1732380A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА МАГНИТНОГО НОСИТЕЛЯ | 1992 |

|

RU2040050C1 |

| Устройство для отображения информации | 1987 |

|

SU1474634A1 |

| Устройство для сопряжения вычислительной машины с датчиками | 1988 |

|

SU1605245A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1987 |

|

SU1476477A1 |

| Устройство для обмена информацией между ЭВМ и периферийными устройствами | 1987 |

|

SU1442996A1 |

| Устройство для подключения устройств ввода-вывода к многосегментной магистрали | 1987 |

|

SU1564638A2 |

Изобретение относится к вычислительной технике, в частности к устройствам для сопряжения ЭВМ и внешних накопителей на подвижных магнитных носителях. Целью изобретения является обеспечение возможности самодиагностики как всего устройства, так и его о-тдельных блоков. Указанная цель достигается введением в устройство элементов, блокирующих информационные связи между отдельными блоками устройства, так и между устройством и маг- нйтным накопителем. В устройство входят блок синхронизации данных, регистр сдвига, блок цилиндрического контроля и генератор записи. Кроме того, в устройство введены элементы, устанавливающие новые информационные связи между блоками устройства .Все вновь введенные элементы включаются в режиме самодиагностики устройства, позволяя ЭВМ произвести анализ его работоспособности с индикацией неисправностей до уровня отдельных блоков. 2 3.п. ф-лы, 3 ил.

Редактор М. Бандура

Составитель С. Бурухин Техред М.Ходанич

Заказ 2799Тираж 671Подписное

. ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий П3035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Корректор М. Шароши

| Устройство для обмена с накопителями на магнитных дисках | 1973 |

|

SU737984A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Микросрелства управляющей вычислительной техники сер | |||

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ИНКА | |||

| Непрерывный дозатор жидкости | 1973 |

|

SU467234A1 |

Авторы

Даты

1986-03-15—Публикация

1984-07-06—Подача