11

I Изобретение относится к вычисли тельной технике и может быть исполь эовано в управляюпшх вычислительных комплексах, имеющих интерфейс Общая шина и содержавших периферийные ройства, использующие другие интерфесы.

Цель изобретения « расширение области применения

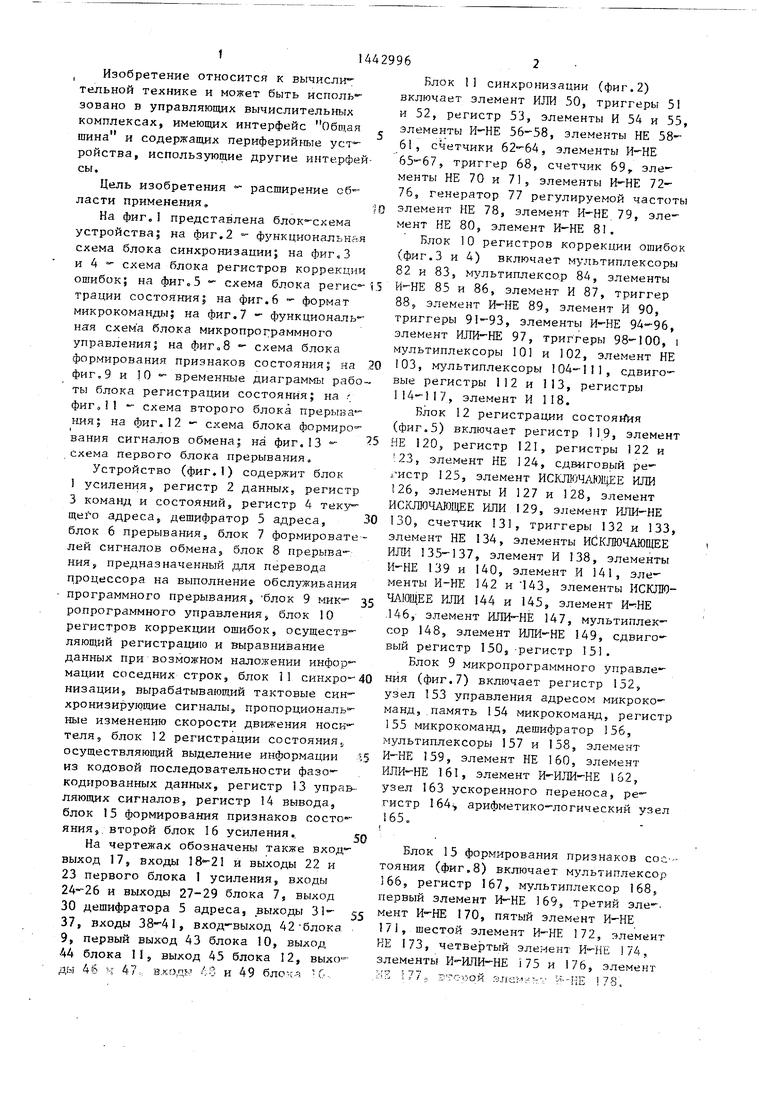

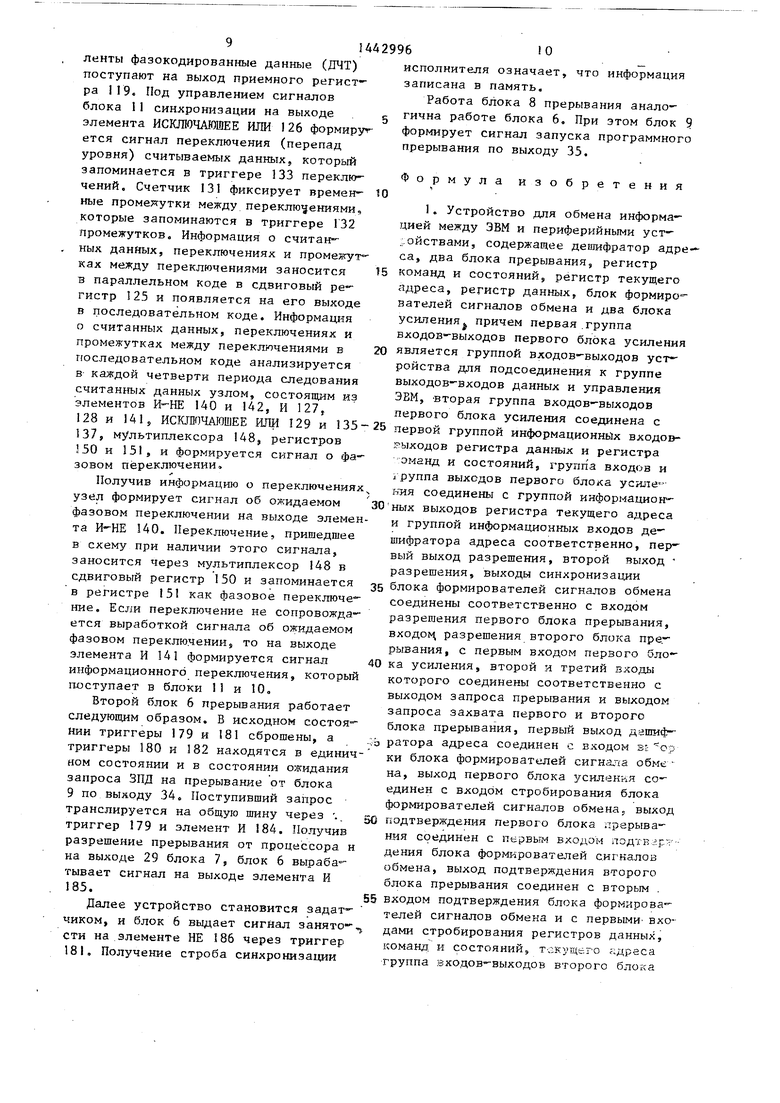

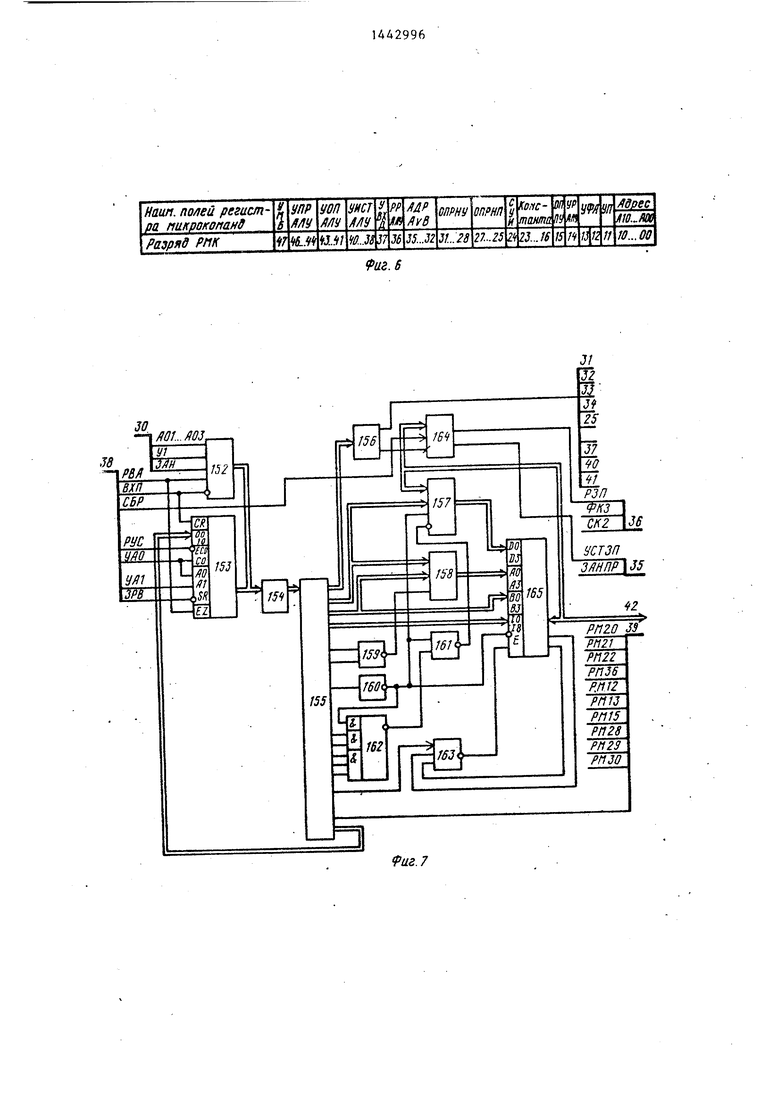

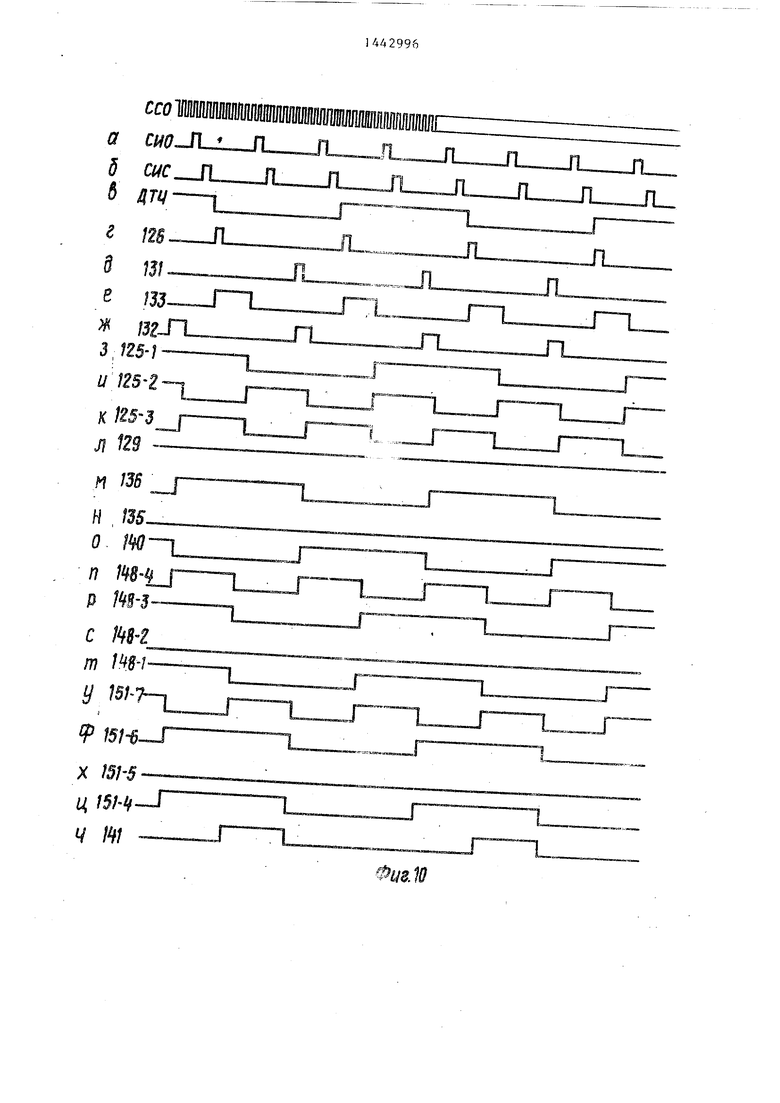

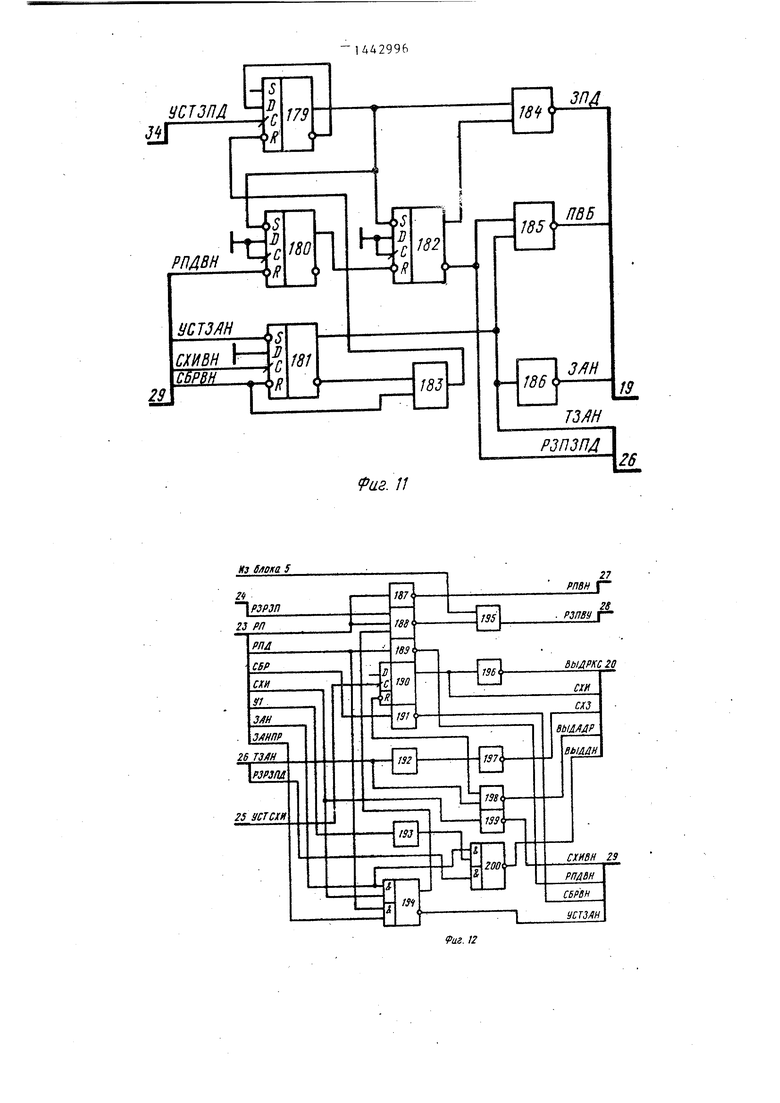

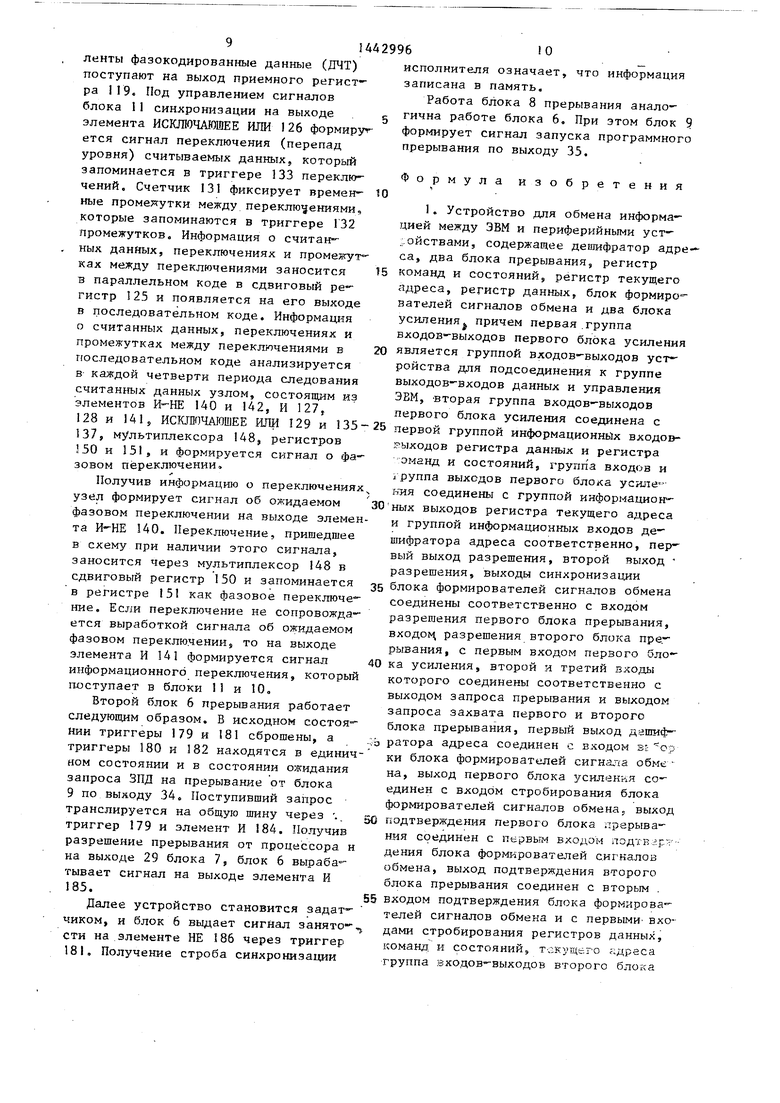

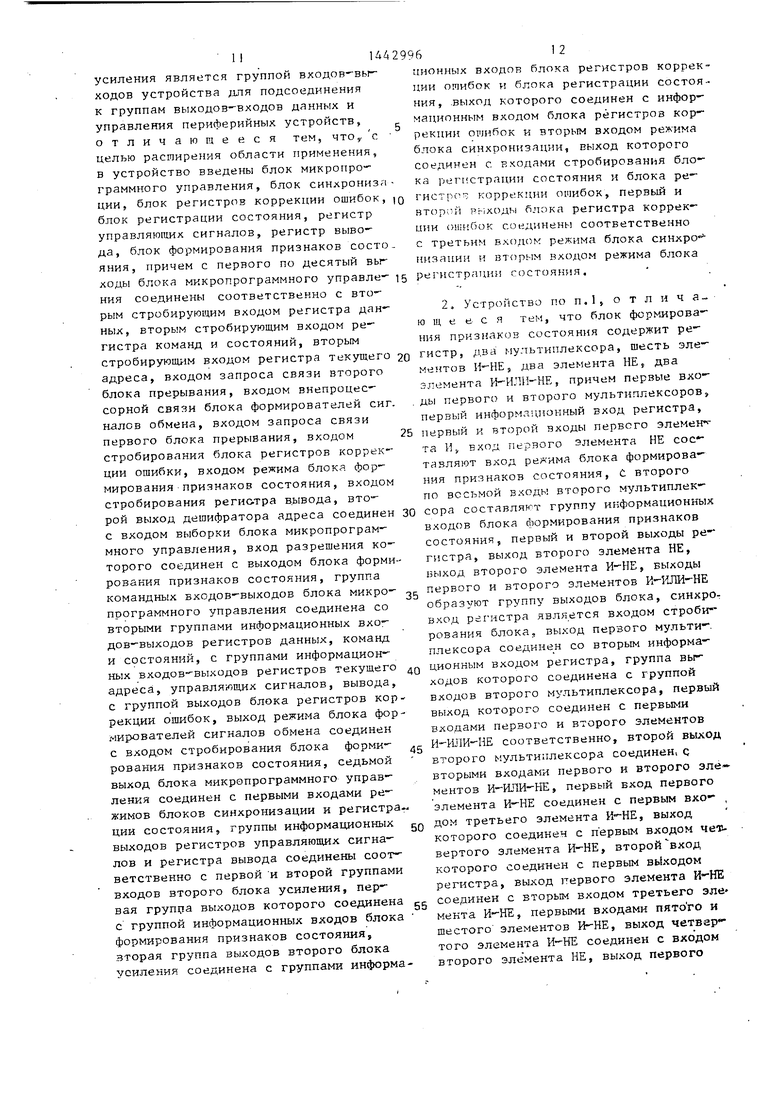

На фиг.1 представлена блок-схема устройства; на фиг.2 - функциональна схема блока синхронизации; на фиг.З и 4 - схема блока регистров коррекци ошибок; на фиг.5 - схема блока perHC трации состояния; на фиг.6 - формат микрокоманды; на фиг. 7 функциона-пь ная схема блока микропрограммного управления; на фиго8 схема блока формирования признаков состояния; на фиг,9 и 10 - временные диаграммы рабты блока регистрации состояния; на . фиг, 1 - схема второго блока прерыва нияI на фиг. 12 - схема блока формиро вания сигналов обмена; на фиг, 13 схема первого блока прерывания.

Устройство (фиг.1) содержит блок усиления, регистр 2 данных, регист 3 команд и состояний, регистр 4 тек щего адреса, дешифратор 5 адреса,

блок 6 прерывания, блок 7 формирователей сигналов обменаj блок 8 прерыва - ния, предназначенный для перевода процессора на выполнение обслуживания программного прерывания, блок 9 мик- з5 ропрограммного управления, блок 10 регистров коррекции ошибок, осуществ - ляющий регистрацию и выравнивание данных при возможном наложении инфор - мадии соседних строк, блок И синхро-40 низации, вырабатывающий тактовые синхронизирующие сигналы, пропорциональ ные изменению скорости движения теля, блок 12 регистрации состояния осуществляющий выделение информации -15 из кодовой последовательности кодированных данных, регистр 13 управляющих сигналов, регистр 14 вывода, блок 15 формирования признаков состо- яния,. второй блок 16 усиления.. 50

На чертежах обозначены также вход выход 17, входы 18-21 и выходы 22 и 23 первого блока 1 усиления, входы 24-26 и выходь 27-29 блока 7, выход 30 дешифратора 5 адреса, выходьг З 55 37, входы 38-41, вход- выход 42 блока 9, первый выход 43 блока 10, выход 44 блока 11, выход 45 блока 12, выхо ды 46 м 47. ВАОдь Лб и 49 блоча С.

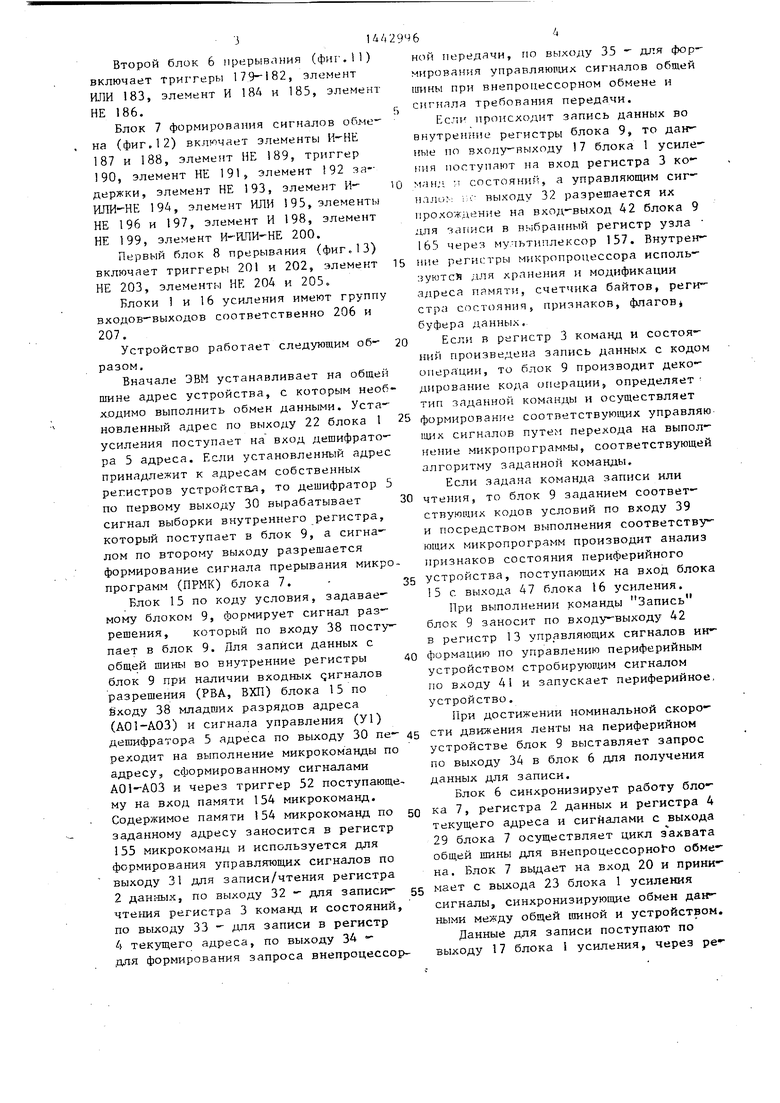

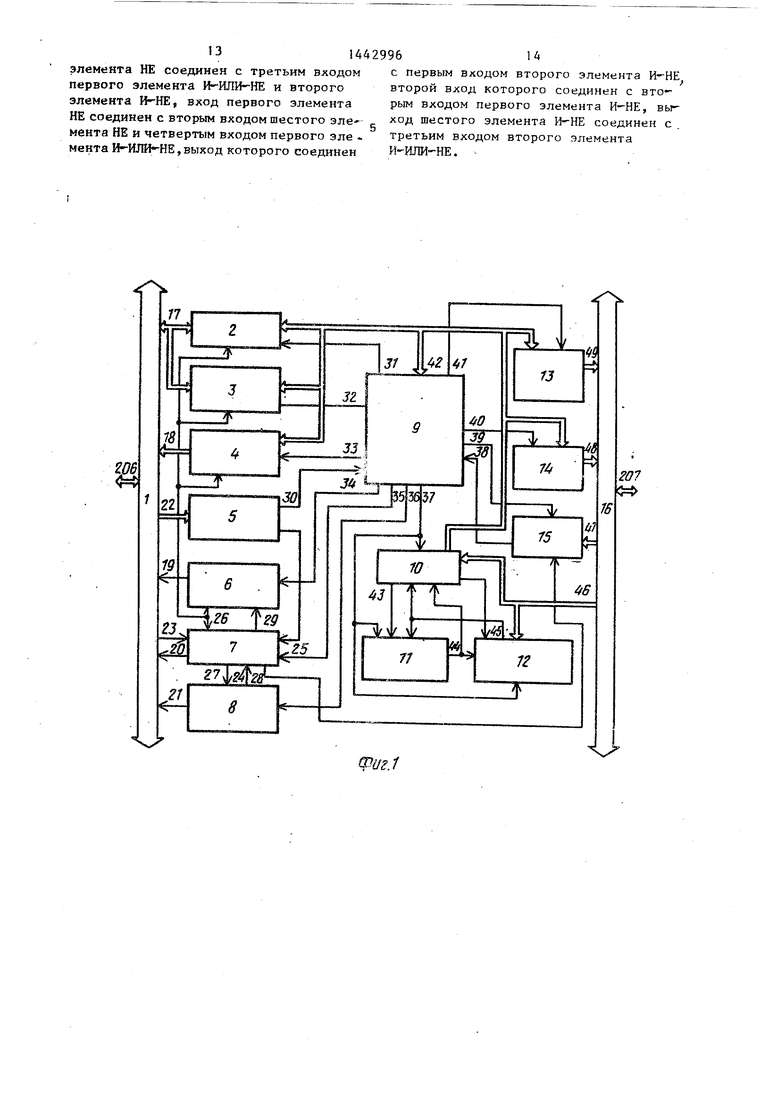

Блок 1 синхронизации (фиг.2) включает элемент ИЛИ 50, триггеры 5 и 52, регистр 53, элементы И 54 и 55, элементы 56-58, элементы НЕ 58- 61, счетчики 62-64, элементы И-НЕ 65-67, триггер 68, счетчик 69, элементы НЕ 70 и 71, элементы И-НЕ 72- 76, генератор 77 регулируемой частоты элемент НЕ 78, элемент И-НЕ 79, элемент НЕ 80, элемент И-НЕ 81.

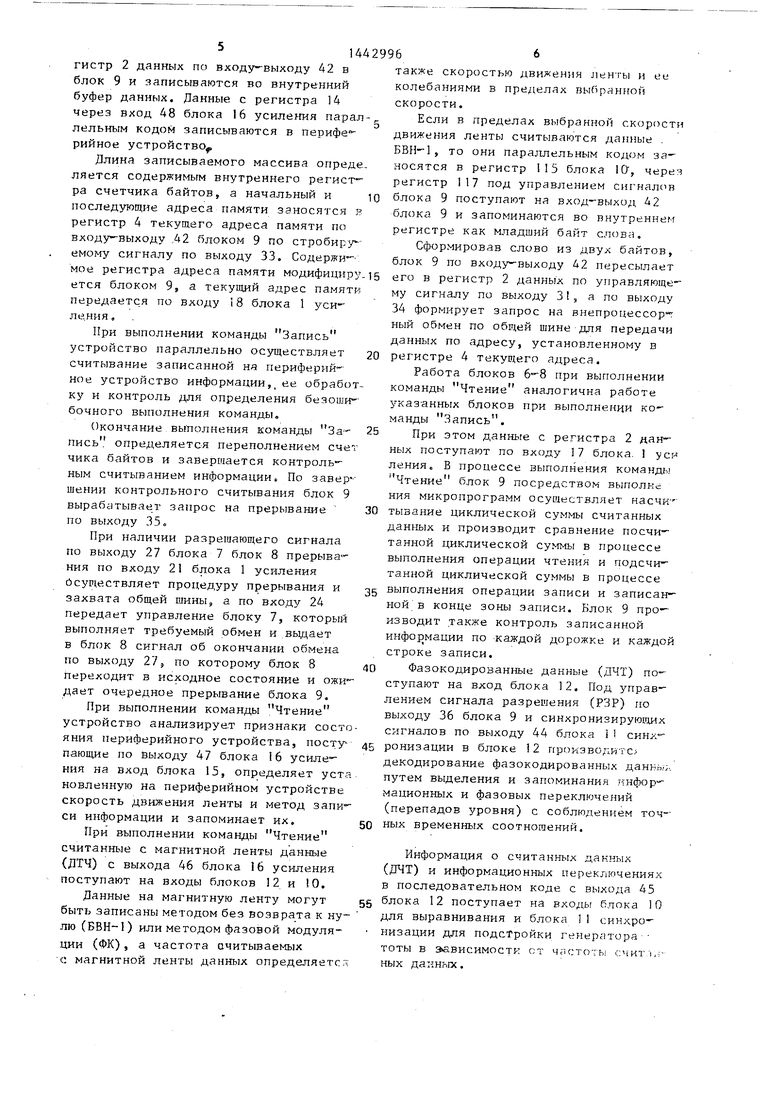

Блок 10 регистров коррекции ошибок (фиг.З и 4) включает мультиплексоры 82 и 83, мультиплексор 84, элементы ИНЕ 85 и 86, элемент И 87, триггер 88, элемент И-НЕ 89, элемент И 90, триггеры 91-93, элементы И-НЕ 94-96, элемент ИЛИ-НЕ 97, триггеры 98-100, i мультиплексоры 101 и 102, элемент НЕ 103, мультиплексоры 104-111, сдвиго

вые регистры 112 и 113, регистры I 14-117, элемент И 118.

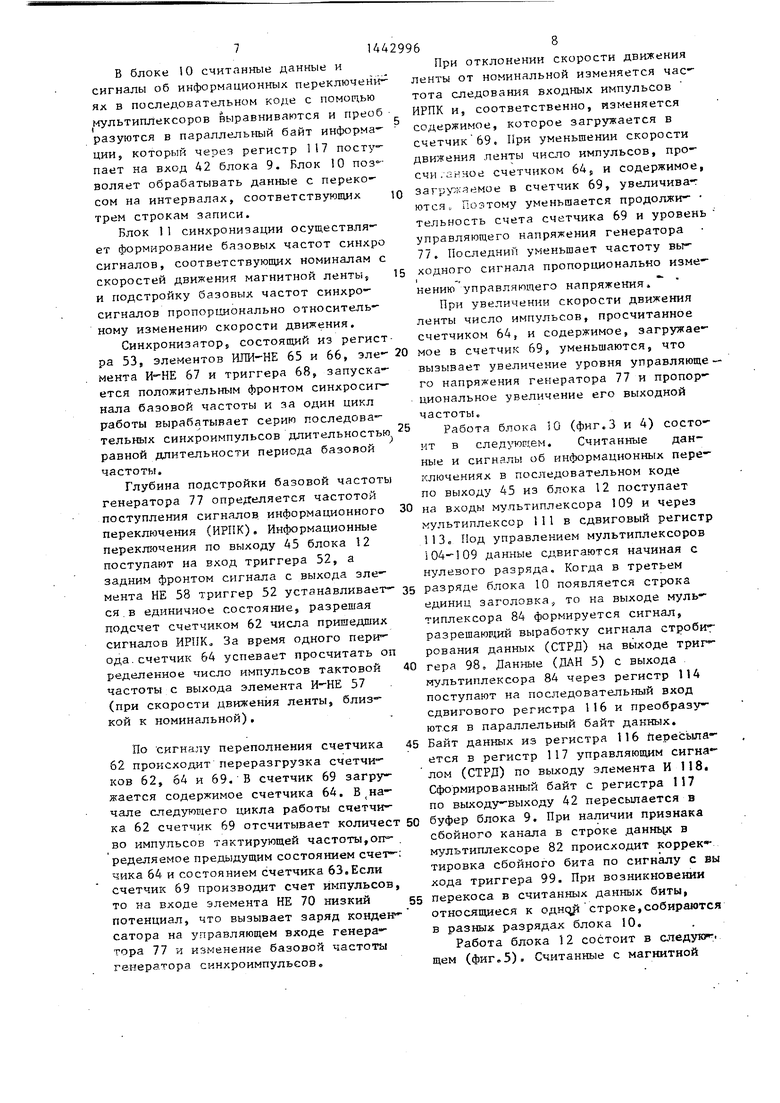

Блок 12 регистрации состоян Ия (фиг.5) включает регистр 119, элемент ЯЕ 120, регистр 121, регистры 122 и 23, элемент НЕ 124, сдвиговый регистр 125, элемент ИСЮТОЧ ЩЕЕ ИЛИ 26, элементы И 127 и 128, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 129, элемент ИЛИ-НЕ 130, счетчик 131, триггеры 132 и 133, элемент НЕ 134, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 135-137, элемент И 138, элементы И-НЕ 139 и 140, элемент И 141, элементы И-НЕ 142 и 143, элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 144 и 145, элемент И-НЕ ,146, элемент ИЛИ-НЁ 147, мультиплексор 148, элемент ИЛИ-НЕ 149, сдвиговый регистр 150j -регистр 151.

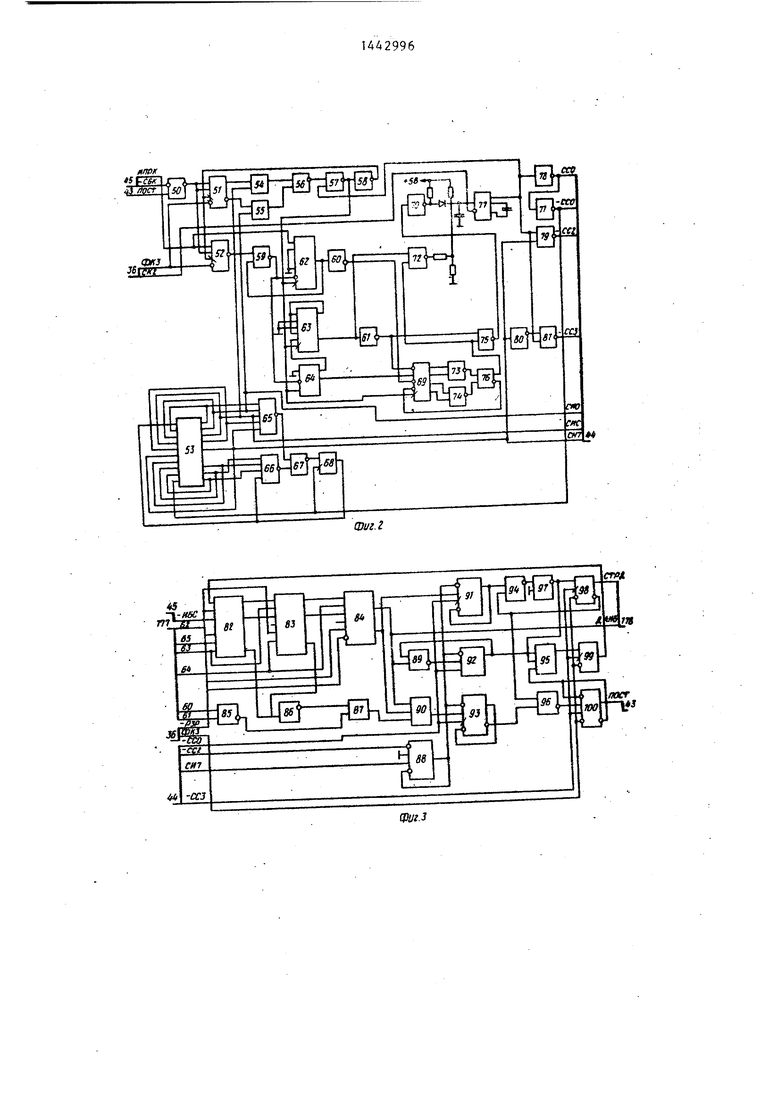

Блок 9 микропрограммного управления (фиг.7) включает регистр 152, узел 153 управления адресом микрокоманд, .память 154 микрокоманд, регистр 155 микрокоманд, дешифратор 156, мультиплексоры 157 и 158, элемент И-НЕ 159, элемент НЕ 160, элемент ИЛИ-НЕ 161, элемент И-ИЛИ-НЕ 1о2, узел 163 ускоренного переноса, регистр 164 арифметико-логический узел

165.

(

Блок 15 формирования признаков состояния (фиг,8) включает мультиплексор lee, регистр 167, мультиплексор 168, первый элемент И-НЕ 169, третий эле-, мент И-НЕ 170, пятый элемент И-НЕ 171, шестой элемент И-НЕ 172, элемент НЕ 173, четвертый элемент И-НЕ 74, элементы И-ИЛИ-НЕ 175 и 176, элемент

Второй блок 6 прерывания (фиг. И) включает триггеры 179-182, элемент ИЛИ 183, элемент И 184 и 185, элемент НЕ 186.

Блок 7 формирования сигналов обле- на (фиг. 12) включает элементы 187 и 188, элемент НЕ 189, триггер 190, элемент НЕ 191, элемент 192 за-- держки, элемент НЕ 193, элемент И- ИЛИ--НЕ 194, элемент ИЛИ 195, элементы НЕ 196 и 197, элемент И 198, элемент НЕ 199, элемент И-ЕПИ-НЕ 200.

Первый блок 8 прерывания (фигЛЗ) включает триггеры 201 и 202, элемент НЕ 203, элементы НЕ 204 и 205.

Блоки 1 и 16 усиления имеют группу входов-выходов соответственно 206 и 207.

Устройство работает следующим об-- разом.

Вначале ЭВМ устанавливает на общей шине адрес устройства, с которым необходимо выполнить обмен данными. Устаной передачи, по выходу 35 ДJTЯ фор-- мировання управляюпшх сигналов общий шины при внепропессорном обмене н сигнала требования передачи.

Если происходит запись данных во внутренние регистры блока 9, то данные по вхопувыходу 17 блока 1 усиле- кия поступают на вход регистра 3 ко

манл ; состояний, а управляющим сиг- нало;-: ::: выходу 32 разрешается их прохождение на вход-выход 42 блока 9 для заг1иси в выбранный регистр узла 165 через му. тьтиплексор 157. Внутрен-

иие регистры микропроцессора используются для хранения и модификации адреса памяти, счетчика байтов, регистра состояния, признаков, флагов буфера данных .Если в регистр 3 команд н состояний произведе} а запись данных с кодом операции, то блок 9 производит декодирование кода операции9 определяет тип заданной команды и осуществляет

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с внешними устройствами | 1990 |

|

SU1839253A1 |

| Устройство для сопряжения электронно-вычислительной машины (ЭВМ) с внешним устройством | 1984 |

|

SU1272337A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для обмена информацией между ЭВМ и внешней памятью | 1989 |

|

SU1714613A1 |

| Устройство для обмена данными между электронно-вычислительной машиной и абонентами | 1985 |

|

SU1277125A1 |

| Устройство для обмена данными между группой каналов ввода-вывода и оперативной памятью | 1985 |

|

SU1278867A2 |

| Имитатор канала | 1990 |

|

SU1714606A1 |

| Устройство для сопряжения электронно-вычислительной машины с внешним устройством | 1986 |

|

SU1388880A2 |

| Устройство для сопряжения периферийных устройств с процессором и оперативной памятью | 1983 |

|

SU1156084A1 |

| Устройство для сопряжения процессора с периферийными устройствами | 1985 |

|

SU1359780A1 |

Изобретение относится к вычисли- тельной технике и может быть исполь зовано в управляющих вычислительных комплексах, имеющих интерфейс Общая ,шина и содержащих периферийные устройства, использующие другие интер- фейсы. В частности, оно может быть применено при необходимости обмена информацией между ЭВМ и контроллером накопителя на магнитных лентах. Целью изобретения является расширение обла сти применения. Устройство содержит два блока усиления, регистр данных, регистр команд и состояний, регистр текущего адреса, дешифратор адреса, два блока прерывания, блок формирователей сигналов обмена, блок микропрограммного управления, блок регистров коррекции ошибок, блок синхронизации, блок регистрации состояний, регистр управляющих сигналов, регистр вывода, блок формирования признаков условий. 1 3. п ф-лы, 13 ил, (Л

новленный адрес по выходу 22 блока I 25 формирование соответствующих управляю- усиления поступает на вход дешифрато- идах сигналов путем перехода на выпол- ра 5 адреса. Если установленный адрес принадлежит к адресам собственных регистров устройства, то дешифратор 5 по первому выходу 30 вырабатывает сигнал выборки внутреннего регистра, который поступает в блок 9, а сигналом по второму выходу разрешается формирование сигнала прерывания микропрограмм (ПРМК) блока 7. - 35 устройства, поступающих на вход блока

Блок 15 по коду условия, задавае- 5 с выхода 47 блока 16 усиления, мому блоком 9, формирует сигнал разрешения, который по входу 38 поступает в блок 9. Для записи данных с общей шины во внутренние регистры блок 9 при наличии входных сигналов разрешения (РВА, ВХП) блока 15 по ёходу 38 младших разрядов адреса (АО1-ЛОЗ) и сигнала управления (У1)

дешифратора 5 адреса по выходу 30 пе- 45 движения ленты на периферийном реходит на выполнение микрокоманды по устройстве блок 9 выставляет запрос адресу, сформированному сигналами по выходу 34 в блок 6 для получения А01-АОЗ и через триггер 52 поступающе- данных для записи, му на вход памяти 154 микрокоманд.

50

нение микропрограммы, соответствующей алгоритму заданной команды.

Если задана команда записи или 30 чтения, то блок 9 заданием соответствующих кодов условий по входу 39 и посредством выполнения соответству- ющих микропрограмм производит анализ признаков состояния периферийного

При выполнении команды Запись блок 9 заносит по входу-выходу 42 в регистр 13 упр авляющих сигналов ин 40 формацию по управлению периферийным устройством стробируюпдлм сигналом по входу 4i и запускает периферийное, устройство.

При достижении номинальной скоро-

Блок 6 синхронизирует работу блока 7, регистра 2 данных и регистра 4 текущего адреса и сигналами с выхода 29 блока 7 осуществляет цикл захвата общей шины для внeпpoцeccopнo o обме- на. Блок 7 выдает на вход 20 и прини-

Содержимое памяти 154 микрокоманд по

заданному адресу заносится в регистр

155 микрокоманд и используется для

формирования управляк1щих сигналов по

выходу 31 для записи/чтения регистра

2 дан1-1ык, по выходу 32 - для записи- 55 мает с выхода 23 блока 1 усиления

чтершя регистра 3 команд и состояний, сигналы, синхронизирующие обмен дан-

по выходу 33 - для записи в регистр ными между общей юиной и устройством.

4 текущего адреса, по выходу 34 -

для формирования запроса внепроцессорДанные для записи поступают по выходу 17 блока 1 усиления, через ре

формирование соответствующих управляю- идах сигналов путем перехода на выпол- устройства, поступающих на вход блока

нение микропрограммы, соответствующей алгоритму заданной команды.

Если задана команда записи или чтения, то блок 9 заданием соответствующих кодов условий по входу 39 и посредством выполнения соответству- ющих микропрограмм производит анализ признаков состояния периферийного

5 с выхода 47 блока 16 усиления,

При выполнении команды Запись блок 9 заносит по входу-выходу 42 в регистр 13 упр авляющих сигналов ин формацию по управлению периферийным устройством стробируюпдлм сигналом по входу 4i и запускает периферийное, устройство.

При достижении номинальной скоро-

движения ленты на периферийном устройстве блок 9 выставляет запрос по выходу 34 в блок 6 для получения данных для записи,

Блок 6 синхронизирует работу блока 7, регистра 2 данных и регистра 4 текущего адреса и сигналами с выхода 29 блока 7 осуществляет цикл захвата общей шины для внeпpoцeccopнo o обме- на. Блок 7 выдает на вход 20 и прини-

Данные для записи поступают по выходу 17 блока 1 усиления, через ре

гистр 2 данных по входу-выходу 42 в блок 9 и записываются во внутренний буфер данных. Данные с регистра 14 через вход 48 блока 16 усиления парал лельным кодом записываются в перифе- рийное устройство

Длина записываемого массива опреде ляется содержимым внутреннего регистра счетчика байтов, а начальный и последующие адреса памяти заносятся в регистр 4 текущего адреса памяти по входувыходу ,42 блоком 9 по стробиру - емому сигналу по выходу 33. Содержи- мое регистра адреса памяти модифициру ется блоком 9, а текущий адрес памяти передается по входу 18 блока 1 уси- ле.ния.

При выполнении команды Запись устройство параллельно осуществляет считывание записанной ня периферийное устройство информации,, ее обработку и контроль для определения безоши бочного выполнения команды.

Окончание выполнения команды пись определяется переполнением счетчика байтов и завершается контроль-- ным считыванием информации. По зaвep шении контрольного считывания блок 9 вырабатывает запрос на прерывание по выходу 35о

При наличии разрешаюп;его сигнала по выходу 27 блока 7 блок 8 прерыва-- ния по входу 21 блока 1 усиления Осуществляет процедуру прерывания и захвата общей шины,, а по входу 24 передает управление блоку 7, который выполняет требуемый обмен и .выдает в блок 8 сигнал об окончании обмена по выходу 27, по которому блок 8 переходит в исходное состояние и дает очередное прерывание блока 9.

При выполнении команды Чтение устройство анализирует признаки состояния периферийного устройства, поступающие по выходу 47 блока 16 усиле- ния на вход блока 15, определяет уста новленную на периферийном устройстве скорость движения ленты и метод запи- си информации и запоминает их.

При выполнении команды Чтение считанные с магнитной ленты данные (ДТЧ) с выхода 46 блока 16 усиления поступают на входы блоков 12 и 0,

Данные на магнитную ленту могут быть записаны методом без возврата к нулю (БВН-) или методом фазовой модуляции (ФК), а частота считываемых с магнитной ленты данных определяется

5

0

5

0

5

0

также скоростью движения ленты и ее колебаниями в пределах выбрангюй скорости.

Если в пределах выбранной скорости движения ленты считываются да1П1ые . ВВП-1 , то они пара:глельным кодом за-- носятся в регистр 115 блока 10, через регистр 117 под управлением сигналов блока 9 поступают на вход-выход 42 блока 9 и запоминаются во внутреннем регистре как младший байт .

Сформировав слово из двух байтов, блок 9 по входувыходу 42 пересылает его в регистр 2 данных по управляющему сигналу по выходу 31, а по выходу 34 формирует запрос на внепроцессор г ный обмен по общей шине для передачи данных по адресу, установленному в регистре 4 текущего адреса.

Работа блоков при выполнении команды Чтение аналогична работе указанных блоков при выполнении команды Запись.

При этом данные с регистра 2 данных поступают по входу 17 блока. уси ления. В процессе выполнения команды Чтение блок 9 посредством выполке ния микропрограмм осуществляет насчи тывание циклической суммы считанных данных и производит сравнение посчитанной циклической суммы в процессе выполнения операции чтения и подсчитанной циклической суммы в процессе выполнения операции записи и записанной в конце зоны записи. Блок 9 производит также контроль записанной инфО1Эмации по каждой дорожке и каждой строке записи.

Фазокодированные данные (ДЧТ) поступают на вход блока 12. Под управлением сигнала разрешения (РЗР) по выходу 36 блока 9 и синхронизируюЕоих сигналов по выходу 44 блока i 1 ронизации в блоке 12 произворитс декодирование фазокодированных даннь/;.. путем выделения и запоминания информационных и фазовых переключений (перепадов уровня) с соблюдением точ-- ных временных соотношений.

Информация о считанных данных (ДЧТ) и информационных переключениях в последовательном коде с выхода 45 блока 12 поступает на входы блока 10

для выравнивания и блока I1 синлро- низации для подстройки генератора тоты в эависимостк ст частоты спит i,:- ных данных.

71442996S

В блоке 10 считанные данные иПри отклонении скорости движения

сигналы об информационных переключенй- ленты от номинальной изменяется час- ях в последовательном коде с помор;ью тота следования входных импульсов мультиплексоров выравниваются и преоб ИРПК и, соответственно, изменяется

разуются в параллельный байт информа ции, который через регистр 117 посту- пает на вход 42 блока 9. Блок 10 поз° воляет обрабатывать данные с переко- сом на интервалах, соответствующих трем строкам записи.

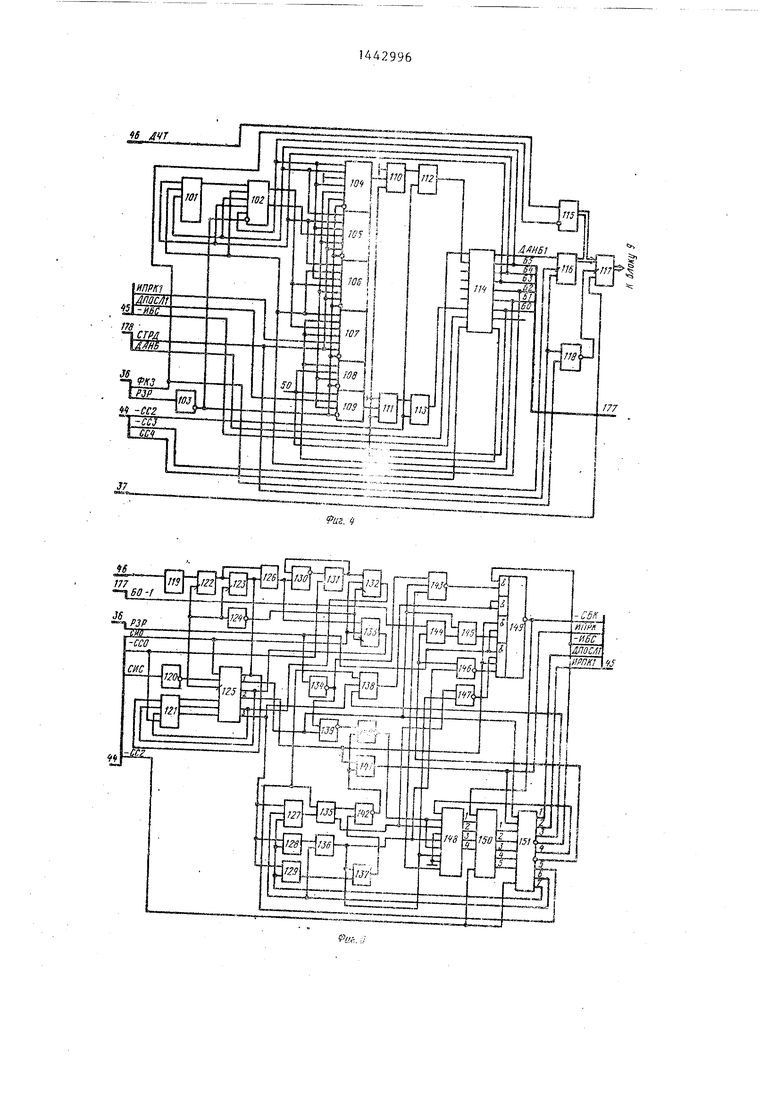

Блок 1 1 синхронизации осуществля-- ет формирование базовых частот синхро сигналов, соответствующих номиналам с скоростей движения магнитной ленты, и подстройку базовых частот синхро-- сигналов пропорционально относительному изменению скорости движения.

Синхронизатор состоящий из регист содержимое, которое загружается в счетчик 69, При уменьшении скорости движения ленты число импульсов, про-- счи.анное счетчиком 64, и содержимое,

0 загружаемое в счетчик 69, увеличива-г ются.. Поэтому уменьшается продолжи тельность счета счетчика 69 и уровень управляющего напряжения генератора 77, Последний уменьшает частоту вьг

15 ходного сигнала пропорционально изменению управляющего напряжения

При увеличении скорости движения ленты число импульсов, просчитанное счетчиком 64, и содержимое, загружав- ра 53, элементов ИЛИ-НЕ 65 и 66, эле 20 мое в счетчик 69, уменьшаются, что мента И- НЕ 67 и триггера 68, запуска- вызывает увеличение уровня управляюще-

ется положительным фронтом синхросиг нала базовой частоты и за один цикл работы вырабатывает серию последова-- тельных синхроимпульсов длительностью равной длительности периода базовой частоты.

Глубина подстройки базовой частоты генератора 77 определяется частотой поступления сигналов информационного переключения (ИРПК), Информационные переключения по выходу 45 блока 12 поступают иа вход триггера 52, а задним фронтом сигнала с выхода злемента НЕ 58 триггер 52 устанавливает- 35 разряде блока 10 появляется строка ся.в единичное состояние, разрешая единиц заголовка, то на выходе муль-

подсчет счетчиком 62 числа пришедших сигналов ИРПКо За время одного пери- ода.счетчик 64 успевает просчитать оп ределенное число импульсов тактовой частоты с выхода элемента И-НЕ 57 (при скорости движения ленты, близкой к номинальной),

45 Байт данных из регистра 116 йерес ыла - ется в регистр 117 управляющим сигна лом (СТРД) по выходу элемента И 118, Сформированный байт с регистра 117 по выходу-выходу 42 пересылается в

По сигналу переполнения счетчика 62 происходит переразгрузка счетчиков 62, 64 и 69, В счетчик 69 загружается содержимое счетчика 64, В начале следующего цикла работы счетчика 62 счетчик 69 отсчитывает количест 50 буфер блока 9, При наличии признака во импульсов тактирующей частоты,оп сбойного канала в строке данных в ределяемое предыдущим состоянием счет-: чика 64 и состоянием счетчика 63,Если счетчик 69 производит счет импульсов, то на входе элемента НЕ 70 низкий 55 перекоса в считанных данных биты, потенциал, что вызывает заряд конден относящиеся к однс строке,собираются сатора на управляющем входе генератора 77 и изменение базовой частоты генератора синхроимпульсов.

мультиплексоре 82 происходит коррек тировка сбойного бита по сигналу с вы хода триггера 99, При возникновении

в разных разрядах блока 10.

Работа блока 12 состоит в следую., щем (фиг.5), Считанные с магнитной

содержимое, которое загружается в счетчик 69, При уменьшении скорости движения ленты число импульсов, про-- счи.анное счетчиком 64, и содержимое,

загружаемое в счетчик 69, увеличива-г ются.. Поэтому уменьшается продолжи тельность счета счетчика 69 и уровень управляющего напряжения генератора 77, Последний уменьшает частоту вьг

ходного сигнала пропорционально измего напряжения генератора 77 и пропорциональное увеличение его выходной частоты,

Работа блока 10 (фиг.З и 4) состоит в следующем. Считанные данные и сигналы об информационных переключениях в последовательном коде по выходу 45 из блока 12 поступает

на входы мультиплексора 109 и через мультиплексор 111 в сдвиговый регистр 113с Под управлением мультиплексоров данные сдвигаются начиная с нулевого разряда. Когда в третьем

типлексора 84 формируется сигнал, разрешающий выработку сигнала стробит рования данных (СТРД) на выходе триг

гера 98. Данные (ДАН 5) с выхода мультиплексора 84 через регистр 114 поступают на последовательный вход сдвигового регистра и преобразуются в параллельный байт данных.

Байт данных из регистра 116 йерес ыла - ется в регистр 117 управляющим сигна лом (СТРД) по выходу элемента И 118, Сформированный байт с регистра 117 по выходу-выходу 42 пересылается в

буфер блока 9, При наличии признака сбойного канала в строке данных в перекоса в считанных данных биты, относящиеся к однс строке,собираются

буфер блока 9, При наличии признака сбойного канала в строке данных в перекоса в считанных данных биты, относящиеся к однс строке,собираются

мультиплексоре 82 происходит коррек тировка сбойного бита по сигналу с вы хода триггера 99, При возникновении

буфер блока 9, При наличии признака сбойного канала в строке данных в перекоса в считанных данных биты, относящиеся к однс строке,собираются

в разных разрядах блока 10.

Работа блока 12 состоит в следую., щем (фиг.5), Считанные с магнитной

ленты фазокодированные данные (ДЧТ) поступают на выход приемного регист - ра 119. Под управлением сигналов блока 11 синхронизации на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 126 формируг ется сигнал переключения (перепад уровня) считываемых данных, которьй запоминается в триггере 133 переклкг- чений. Счетчик 131 фиксирует временные промежутки между переключениями, которые запоминаются в триггере 132 промежутков. Информация о считан - ных данных, переключениях и промежутках между переключениями заносится в параллельном коде в сдвиговый гистр I25 и появляется на его выходе в последовательном коде, Информащ-ш о считанных данных, переключениях и промежутках между переключениями в последовательном коде анализируется в каждой четверти периода следования

1, Устройство для обмена информацией между ЭВМ и периферийными уст .;.ойствами, содержащее дешифратор адре са, два блока прерывания, регистр команд и состояний, регистр текущего адреса, регистр данных, блок формиро- нателей сигналов обмена и два блока усиления причем первая .группа входов-выходов первого блока усиления 20 является группой влодов- выходов устройства для подсоединения к группе выходов-входов данных и управления ЭВМ, -вторая группа входов-выходов первого блока усиления соединена с

считанных данных узлом, состоящим из

элементов И-НЕ 140 и 142, И 127,

128 и 141, ИСКЛЮЧАЮЩЕЕ ИЛИ 129 и 135-25 первой группой информационных входов137, мультиплексора 148, регистров рыходов регистра данных и регистра

50 и 151, и формируется сигнал о фаоманд и состояний, I pynn a входов и группа выходов первого блока усиле - кия соединены с группой информационных выходов регистра текущего адреса и группой информационных входов дешифратора адреса соответственно, первый выход разрешения, второй выход разрешения, выходы синхронизации 35 блока формирователей сигналов обмена соединены соответственно с входом

зовом переключении.

Получив информацию о переключениях узел формирует сигнал об ожидаемом зО фазовом переключении на выходе элемента И-НЕ 140, Переключение, пришедшее в схему при наличии этого сигнала, заносится через мультиплексор 148 в сдвиговый регистр 150 и запоминается в регистре 151 как фазовое переключе35

ние. Если переключение не сопровождается выработкой сигнала об ожидаемом фазовом переключении, то на выходе элемента И 141 формируется сигнал информационного переключения, который поступает в блоки 11 и 10,

Второй блок 6 прерывания работает следующим образом. В исходном состоянии триггеры 179 и 181 сброшены, а триггеры 180 и 182 находятся в единичном состоянии и в состоянии ожидания запроса ЗПД на прерывание от блока 9 по выходу 34« Поступивший запрос транслируется на общую шину через .. триггер 79 и элемент И 184, Получив разрешение прерывания от процессора н на выходе 29 блока 7, блок 6 выраба - тывает сигнал на выходе элемента И 185,

Далее устройство становится задат- чиком, и блок 6 выдает сигнал занято сти на элементе НЕ 186 через триггер 181, Получение строба синхронизации

исполнителя означает, что информация записана в память.

Работа блока 8 прерывания анало- гична работе блока 6, При этом блок 9 формирует сигнал запуска программного прерывания по выходу 35,

Формула изобретения

ч

1, Устройство для обмена информацией между ЭВМ и периферийными уст .;.ойствами, содержащее дешифратор адре- - са, два блока прерывания, регистр команд и состояний, регистр текущего адреса, регистр данных, блок формиро- нателей сигналов обмена и два блока усиления причем первая .группа входов-выходов первого блока усиления является группой влодов- выходов устройства для подсоединения к группе выходов-входов данных и управления ЭВМ, -вторая группа входов-выходов первого блока усиления соединена с

первой группой информационных входовзО

оманд и состояний, I pynn a входов и группа выходов первого блока усиле - кия соединены с группой информационных выходов регистра текущего адреса и группой информационных входов дешифратора адреса соответственно, первый выход разрешения, второй выход разрешения, выходы синхронизации 35 блока формирователей сигналов обмена соединены соответственно с входом

разрешения первого блока прерывания, входо разрешения второго блока прерывания, с первым входом первого бло40 ка усиления, второй и третий входы которого соединены соответственно с выходом запроса прерывания и выходом запроса захвата первого и второго блока прерывания, первый выход дашиф

4Ь ратора адреса соединен с входом ки блока формирователей сигнала обмена, выход первого блока усняеккя соединен с входом стробирования блока формирователей сигналов обмена,, выход

50 подтверждения первого блока прерывания соединен с первым входом подтв р - дения блока формирователей сигналов обмена, выход подтверждения второго блока прерывания соединен с вторым .

55 входом подтверждения блока формирователей сигналов обмена и с первыми вхо- дами стробирования регистров данных, команд и состояний,, текущего адреса группа входов-выходов второго блока

усиления является группой входов-выходов устройства ;1ля подсоединения к группам выходов-входов данных и управления периферийных устройств, отличающееся тем, что с целью расширения области применения, в устройство введены блок микропрограммного управления, блок синхронизации, блок регистров коррекции ошибок, блок регистрации состояния, регистр управляющих сигналов, регистр вывода, блок формирования признаков состояния, причем с первого по десятый выходы блока микропрограммного управле- ния соединены соответственно с вторым стробирующим входом регистра данных, вторым стробирующим входом регистра команд и состояний, вторым стробирующим входом регистра текущего адреса, входом запроса связи второго блока прерывания, входом внепроцес- сорной связи блока формирователей сиг налов обмена, входом запроса связи первого блока прерывания, входом стробировання блока регистров коррекции ощибки, входом режима блока формирования признаков состояния, входом стробирования регис-тра в.ывода, второй выход дешифратора адреса соединен с входом выборки блока микропрограммного управления, вход разрещения которого соединен с выходом блока формирования признаков состояния, группа командных входов-выходов блока микро- программного управления соединена со вторыми группами информационных входов-выходов регистров данных, команд и состояний, с группами информационных входов-выходов регистров текущего адреса, управляющих сигналов, вывода, с группой выходов блока регистров коррекции ошибок, выход режима блока формирователей сигналов обмена соединен с входом стробирования блока форми- рования признаков состояния, седьмой выход блока микропрограммного управления соединен с первыми входами режимов блоков синхронизации и регистра

ЦИИ состояния, группы информационных

выходов регистров управляющих сигналов и регистра вывода соединены соответственно с первой и второй группами входов второго блока усиления, первая группа выходов которого соединена с группой информационных входов блока формирования признаков состояния, вторая группа выходов второго блока усиления соединена с группами информационных входов блока регистров коррекции ошибок и блока регистрации состояния, -ВЫХОД которого соединен с информационным входом блока регистров коррекции ошибок и вторым входом режима блока синхронизации, выход которого соединен с входами стробирования блока реп страции состояния и блока ре- гистпс коррекции ошибок, первый и втсзрпй вг-;холы блока регистра коррекции ошибок соединены соответственно с третьим вход(5м режима блока синхро низации и вторым входом режима блока регистрпци.и состояния.

элемента НЕ соединен с третьим входом первого элемента И-ИЛИ-НЕ и второго элемента И--НЕ, вход первого элемента НЕ соединен с вторым входом шестого эле мента НЕ и четвертым входом первого эле - мента И-ИЛИ НЕ,выход которого соединен

Vx

с первым входом второго элемента И-НЕ второй вход которого соединен с вторым входом первого элемента И-НЕ, выход шестого элемента И-НЕ соединен с третьим входом второго элемента И-ИЛИ-НЕ.

.«г%

207

иг.1

ts

ЯПРК

45

т

81

в5

,

36

ии

-ссз

Фиг. I

КЗ

99

96 ,

Ю0

iW H-i«

(1ПРК1

и/щп

Ш-Ш

шм.

1

&ш.

SS

JOB

4Ч

-.-„ I H Э W H- -H

W

ПЧ

F

60

JL

t

1

да/

/77

J/

ш

1

Jf

4s

N

ссо CHO JLJL- Jil

JI

л

§ Ш -

e ш

m-TL

3 125-1-

J

n

n 36 j

H . Ш-

п W-U

р т-3- с m-i

т /./-

у 15i 7-i

X Ш-5 - ц

V -

л

л

П

Л JL

Т.

п

л

Х

гп„

JT

г

Г

.J

L.™

29

Из ff/ioxa 5

гч

РЗРЗП

Z3 РП

РПЛ

СВР

схи

уг.

ЗАИ

ЗАИПР

26 ТЭАН

f3P3n

25 ЯСТСКН

J9

Ри.г. Л

J87i

РПВН

27

т

рзпву г

183

т

дыдркао

a/f

саз

ВЬШМР

fS7i

вшди

rssi

F

гоо

СХНВН Z9

71 /Л

Л

СБРвН

УСТЗЛН

27 РПВН

2 ЗП

.

afjrvjKweiaca

ЗЙН

us. fJ

л

Авторы

Даты

1988-12-07—Публикация

1987-04-10—Подача