Изобретение относится к радиотехнике и может использоваться в радиотехнических устройствах контроля частоты и фазы импульсных последовательностей.

Цель изобретения - повышение точности цифрового фазочастотного компаратора.

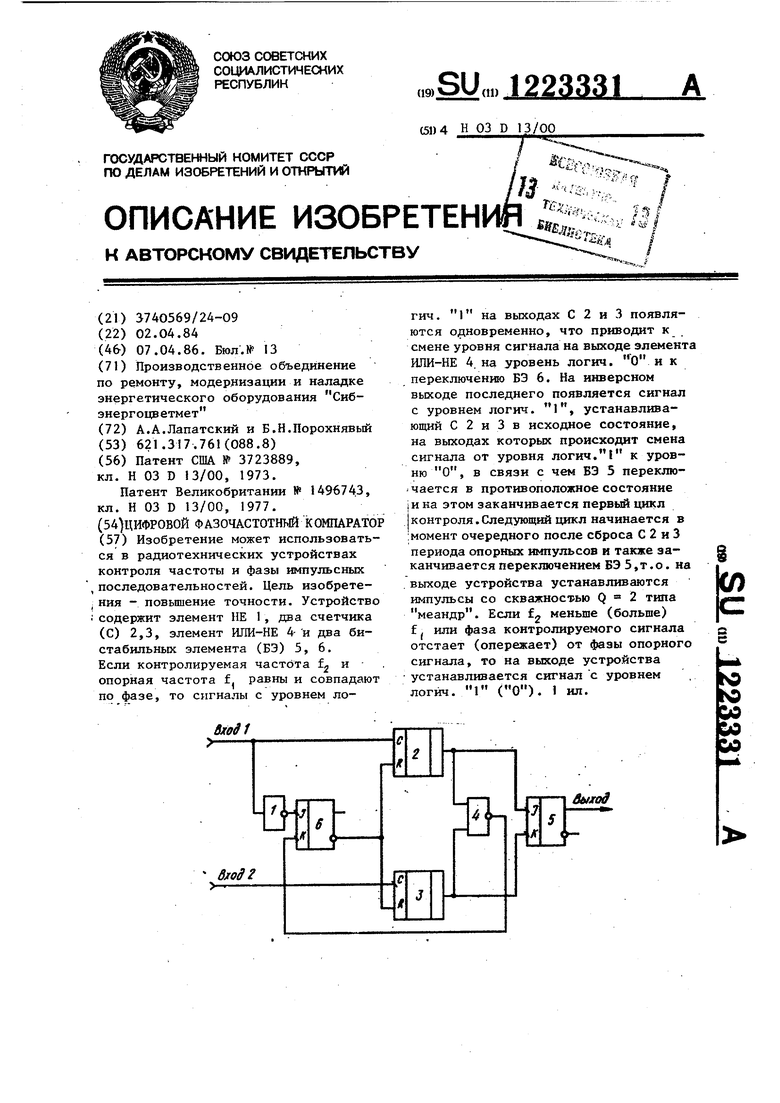

На чертеже приведена функцио- нальная электрическая схема цифрового фазочастотного компаратора.

Предлагаемый компаратор содержит элемент НЕ I, первый 2 и второй 3 счетчики, элемент ИЛИ-НЕ 4, первый 5 и второй 6 бистабильные элементы, В качестве бистабильных элементов могут использоваться, например, I-K- триггеры с динамическими входами I и К.

Цифровой фазочастотный компаратор работает следующим образом.

Контролируемая .последовательность, импульсов с частотой f поступает на счетньй вход второго счетчика 3, который является вторым входом цифрового фазочастотного компаратора. На счетный вход первого счетчика 2 поступает опорная последовательность импульсов с частотой и скважностью Q 2..

В исходном состоянии на инверсном входе второго бистабильного элемен- та 6 присутствует уровень логической единицы, который по входам сброса удерживает счетчики 2 и 3 в исходном состоянии. Очередной импульс опорной частоты t переключает второй бистабильньш элемент 6 в единичное состояние. При этом снимается сигнал сброса с входов счетчиков 2 и 3. В связи с этим начало счета импульсов обоими счетчиками 2 и 3, т.е. начало контроля, совпадает с моментом начала периода опорных сигналов.

Если частоты f и f равны и-совпадают по фазе, то сигналы с уровнем логической единищл на выходах счетчиков 2 и 3 появляются одновременно. Это приводит к смене уровня сигнала на выходе элемента ИПИ-НЕ на уровень логического О и переключению второго бистабильноро элемента 6. На его инверсном выходе устанавливается сигнал с уровнем логической 1, в связи с чем счетчики 2 и 3 уста- лавливаются в исходное состояние. На выходах счетчиков 2 и 3 происхо

5

5

дит смена сигнала от уровня логической 1 к уровню О. В связи с этим первый бистабильный элемент 5 переключается в противоположное сос- тояние. На этом заканчивается первый цикл контроля. Следующий цикл контроля начинается в момент очередного сброса счетчиков 2 и 3 периода опорных импульсов и также заканчивается переключением первого бистабильного элемента 5.

Таким образом, если частоты i и fj равны и фазовый сдвиг контролируемых импульсов отсутствует, то , на выходе цифрового фазочастотного компаратора устанавливаются импульсы со скважностью Q 2 типа меандр.

Если контролируемая частота fg ниже опорной f( или фаза контролируемого сигнала отстает от фазы опорного сигнала, то на выходе цифрового фазочастотного компаратора устанавливается сигнал с уровнем логической 1. Это вызвано тем, что после заполнения первого счетчика 2 счетчики 2 и 3 устанавливаются в исходное состояние и переключающие первый бистабильный элемент 5 импульсы поступают только на его первый вход. В-случае, когда контролируемая частота f больше опорной fj или фаза .контролируемого сигнала опережает фазу опорного, переключающие первый бистабильный элемент 5 им5 пульсы поступают только на второй его вход и на выходе цифрового фазочастотного компаратора устанавливается сигнал с уровнем логического О.

0

Формула изобретения

Цифровой фазочастотный компаратор ,, содержащий первый и второй

$ счетчики, входы сброса которых объединены, элемент НЕ и первьш бистабильный элемент, выход которого является выходом цифрового фазочастотного компаратора, отличаю0 щ и и с я тем, что, с целью повышения точности, в него введень второй бистабильный элемент и элемент ИЛИ-НЕ, причем счетный вход первого счетчика объединен с входом элемента

5 НЕ и является первым входом цифрового фазочастотного компаратора, выход первого счетчика соединен с первым входом первого бистабильного

0

3 1223331Л

элемента и первым входом элементакоторого соединен с выходом элементаИЛИ-НЕ, выход второго счетчика со-НЕ, а инверсный выход соединен с

единен с вторым входом первого би-входами сброса первого и второго

стабильного элемента и вторым входомсчетчиков, причем счетный вход втоэлемента ИЛИ-НЕ, выход которого со- рого счетчика является BTop№ вхоединен с первым входом второго би-дом цифрового фазочастотного компарастабильного элемента, второй вход тора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь ортогональных сигналов | 1989 |

|

SU1758581A1 |

| УСТРОЙСТВО СИНХРОНИЗАЦИИ | 2000 |

|

RU2167493C1 |

| Устройство для синхронизации и выделения данных | 1989 |

|

SU1675943A1 |

| Устройство для резервирования источников электропитания | 1988 |

|

SU1653075A1 |

| Устройство для числового программного управления | 1985 |

|

SU1352459A1 |

| Устройство для измерения нелинейности пилообразного напряжения | 1990 |

|

SU1777101A1 |

| Цифровой частотный дискриминатор | 1985 |

|

SU1363430A1 |

| Способ измерения амплитудных значений электрических сигналов | 1986 |

|

SU1509751A1 |

| Устройство для контроля тока | 1985 |

|

SU1290183A1 |

| Устройство для оценки характеристик узкополосного случайного процесса | 1983 |

|

SU1117650A1 |

Изобретение может использоваться в радиотехнических устройствах контроля частоты и фазы импульсных , последовательностей. Цель изобрете- ния - повышение точности. Устройство содержит элемент НЕ 1 , два счетчика (С) 2,3, элемент ИЛИ-НЕ 4- и два би- стабильных элемента (БЭ) 5, 6. Если контролируемая частота f и опорная частота f равны и совпадают по фазе, то сигналы с уровнем логич. 1 на выходах С 2 и 3 появляются одновременно, что приводит к смене уровня сигнала на выходе элемента ИЛИ-НЕ 4. на уровень логич. 0 и к переключению БЭ 6. На инверсном выходе последнего появляется сигнал с уровнем логич. 1, устанавливающий С 2 и 3 в исходное состояние, на выходах которых происходит смена сигнала от уровня логич. к уровню О , в связи с чем БЭ 5 переклю- чается в противоположное состояние |и на этом заканчивается первый цикл контроля.Следующий цикл начинается в момент очередного после сброса С 2 и 3 периода опорных импульсов и также заканчивается переключением БЭ 5, т. о. на выходе устройства устанавливаются импульсы со скважностью типа меандр. Если f меньше (больше) f, или фаза контролируемого сигнала отстает (опережает) от фазы опорного сигнала, то на выходе устройства устанавливается сигнал с уровнем логич. 1 (О). 1 ил.

| Патент США № 3723889, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ производства диетического пшеничного хлеба | 1987 |

|

SU1496743A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-04-07—Публикация

1984-04-02—Подача