1

Изобретение относится к измерительной технике и предназначено для использования в радиоэлектронных уст- ройствйх контроля и автоматического регулирования сравниваемых-частот.

Цель изобретения - повышение точности сравнения частот.

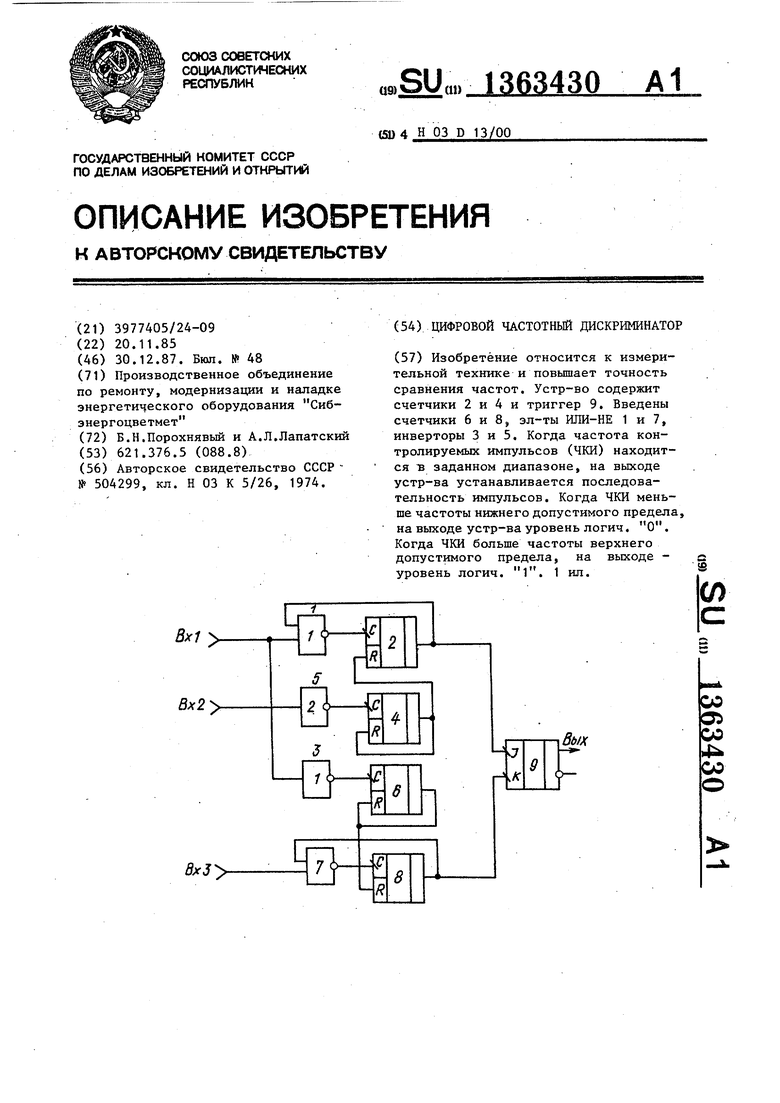

На чертеже приведена структурная

электрическая схема цифрового частот- ю счетчик 2 устанавливается в исходное ного дискриминатора.

Цифровой частотньй дискриминатор содержит первый элемент ИЛИ-НЕ 1, первый счетчик 2, первый инвертор 3, второй счетчик 4, второй инвертор 5, -jr. третий счетчик 6, второй элемент ИЛИ-НЕ 7, четвертый счётчик 8 и тригсостояние. Это приводит к смене состояния триггера 9. и на его выходе устанавливается уровень логической единицы. Таким образом, в случае, когда частота контролируемой последовательности импульсов находится в зоне допустимых значений, происходит последовательная смена состояний триггера 9 и на его выходе формируется последовательность импульсов.

гер 9. Первь№1 входом устройства является вход элемента ИЛИ-НЕ 1.

Вторым и третьим входами являются соответственно входы второго инвертора 5 и второго элемента ИЛИ-НЕ 7, Выходы триггера 9 являются выходами устройства.

Цифровой частотный дискриминатор работает следующим образом.

Контролируемая последовательность импульсов с частотой f, подается на первьй вход цифрового частотного дискриминатора. На второй вход посту- пает последовательность импульсов с частотой f/iH , равной нижнему допустимому пределу контролируемой последовательности. На третий вход посту- пает последовательность импульсов с частотой fjg,, равной верхнему допустимому пределу частоты контролируемой последовательности.

В случае, когда частота контролируемой последовательности импульсов находится в заданных пределах, т.е. .

-аи

f,faB

первым произойдет заполнение четвертого счетчика 8. После заполнения четвертого счетчика 8, возникающий на его выходе сигнал с уровнем ло: и- ческой единицы поступает на первый вход второго элемента ИЛИ-НЕ 7. На выходе второго элемента ИЛИ-НЕ 7 устанавливается уровень логического нуля, останавливающий четвертьй счетчик 8. После заполнения четвертого счетчика 8 происходит одновременно заполнение первого и третьего счетчиков 2 и 6. После заполнения этих счетчиков на выходе первого счетчик 2 удерживается уровень логической

34302

единицы, а на вход сброса R (установочный вход) четвертого счетчика 8 поступает импульс, устанавливающий его в исходное состояние. При этом, также происходит смена состояния триггера 9 и на его выходе устанавливается уровень логического нуля. Затем заполняется второй счетчик 4 и первь1й

счетчик 2 устанавливается в исходное

состояние. Это приводит к смене состояния триггера 9. и на его выходе устанавливается уровень логической единицы. Таким образом, в случае, когда частота контролируемой последовательности импульсов находится в зоне допустимых значений, происходит последовательная смена состояний триггера 9 и на его выходе формируется последовательность импульсов.

В случае, когда частота контролируемой последовательности импульсов меньше нижнего допустимого предела, т.е.

25

f f

2Н

первым происходит заполнение четвертого счетчика 8. Второй счетчик 4 заполнится вторым и установит первый счетчик 2 в исходное состояние раньше момента его заполнения. Вследствие этого на выходе первого счетчика 2 будет постоянно присутствовать уровень логического нуля и переключение триггера по первому входу I происходить не будет. После заполнения третьего счетчика 6 произойдет установка в исходное состояние четвертого счетчика 8, что вызовет, в свою очередь, переключение триггера 9 по-, второму входу К в состояние логического нуля. Во всех последующих циклах это состояние не изменится.

В случае, когда частота контролируемой последовательности больше верхнего допустимого предела, т.е.

f,f

гв

50

5

первым произойдет заполнение первого и третьего счетчиков 2 и 6. При этом, сигнал с выхода третьего счетчика 6 установит четвертый счетчик 8 в исходное состояние раньше момента заполнения последнего. Таким образом, на выходе четвертого счетчика 8 будет постоянно присутствовать уровень логического нуля и переключение триг. 31363430

9 по второму входу К происходить единен

отл с цель частот счетчик инверт мента И объеди

не будет. После заполнения второго счетчика 4 произойдет установка в исходное состояние первого счетчика 2 и это вызовет переключение триггера 9 по первому входу I в состояние логической единицы. Во всех последу- щих циклах это состояние не изменится.

Таким образом, когда частота контролируемых импульсов находится в заданном диапазоне, на выходе цифрового частотного дискриминатора устанавливается последовательность импульсов. Когда частота контролируемых импульсов меньше частоты нижнего допустимого предела, на выходе цифрового частотного дискриминатора устанавливается уровень логического нуля. Когда частота контролируемых импульсов больше частоты верхнего допустимого предела, на его выходе устанавливается уровень логической единицы.

Формула изобретения

Цифровой частотный дискриминатор, содержащий первый и второй счетчики и триггер, первый вход которого соор И.Сегляник 6378/52

Составитель А.Колосов Техред М.Ходанич

Коррек

.«..

Подпис

Тираж 900 ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

единен

с выходом первого счетчика, отличающийся тем, что, с целью повышения точности сравнения частот, введены третий и четвертый счетчики, два элемента МПИ-ПЕ и два инвертора, первые .входы первого элемента ИЛИ-НЕ и первого инвертора объединены и являются входом первой

Q опорной частоты цифрового частотного дискриминатора, второй вход второго элемента ИЛИ-НЕ подключен к выходу, а ВЫХОД - к счетному входу первого счетчика, вход второго инверто15 .ра является входом второй опорной частоты цифрового частотного дискриминатора, а выход - к счетному входу второго счетчика, установочньш п вход которого соединен с его выходом

Q и установочным входом первого счетчика, выход первого инвертора подключен к счетному входу третьего счетчика, выход которого соединен с его установочным входом и установоч5 ным входом четвертого счетчика, выход которого подключен к второму входу триггера и первому входу второго элемента ИЛИ-НЕ, второй вход которого является входом сигнала контроди0 РУ6МОЙ частоты цифрового частотного дискриминатора, а выход подключен к счетному входу четвертого счетчика.

Корректор Л.Пилипенко

.«..IV M - HH B « - --«--- «

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| АППАРАТУРА РАДИАЦИОННОГО КОНТРОЛЯ ТЕХНОЛОГИЧЕСКОГО ПРОЦЕССА (АРКТ) | 2017 |

|

RU2661451C1 |

| Частотно-фазовый дискриминатор | 1986 |

|

SU1363432A1 |

| Преобразователь кода в скорость вращения вала | 1988 |

|

SU1599991A1 |

| Устройство контроля импульсной последовательности | 1983 |

|

SU1167520A1 |

| Частотно-фазовый дискриминатор | 1988 |

|

SU1589373A1 |

| ЧАСТОТНО-ФАЗОВЫЙ ДИСКРИМИНАТОР | 2010 |

|

RU2428785C1 |

| Фазовый дискриминатор | 1988 |

|

SU1598109A1 |

| Реверсивный измеритель скольжения механических передач | 1986 |

|

SU1619174A1 |

| ФАЗОВЫЙ ДИСКРИМИНАТОР | 2013 |

|

RU2541899C1 |

| СИНХРОННО-СИНФАЗНЫЙ ЭЛЕКТРОПРИВОД | 2006 |

|

RU2310971C1 |

Изобретение относится к измерительной технике и повышает точность сравнения частот. Устр-во содержит счетчики 2 и 4 и триггер 9. Введены счетчики 6 и 8, эл-ты ИЛИ-НЕ 1 и 7, инверторы 3 и 5. Когда частота контролируемых импульсов (ЧКИ) находится в заданном диапазоне, на выходе устр-ва устанавливается последовательность импульсов. Когда ЧКИ меньше частоты нижнего допустимого предела, на выходе устр-ва уровень логич. О. Когда ЧКИ больше частоты верхнего допустимого предела, на выходе - уровень логич. 1. 1 шт. § (Л

| Частотное пороговое устройство | 1974 |

|

SU504299A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1987-12-30—Публикация

1985-11-20—Подача