Изобретение относится к вычислительной технике и может быть использовано в устройствах сравнения, а также в качестве формирователя переноса в устройствах суммирования и - вычитания.

Цель изобретения - повышение надежности устройства.

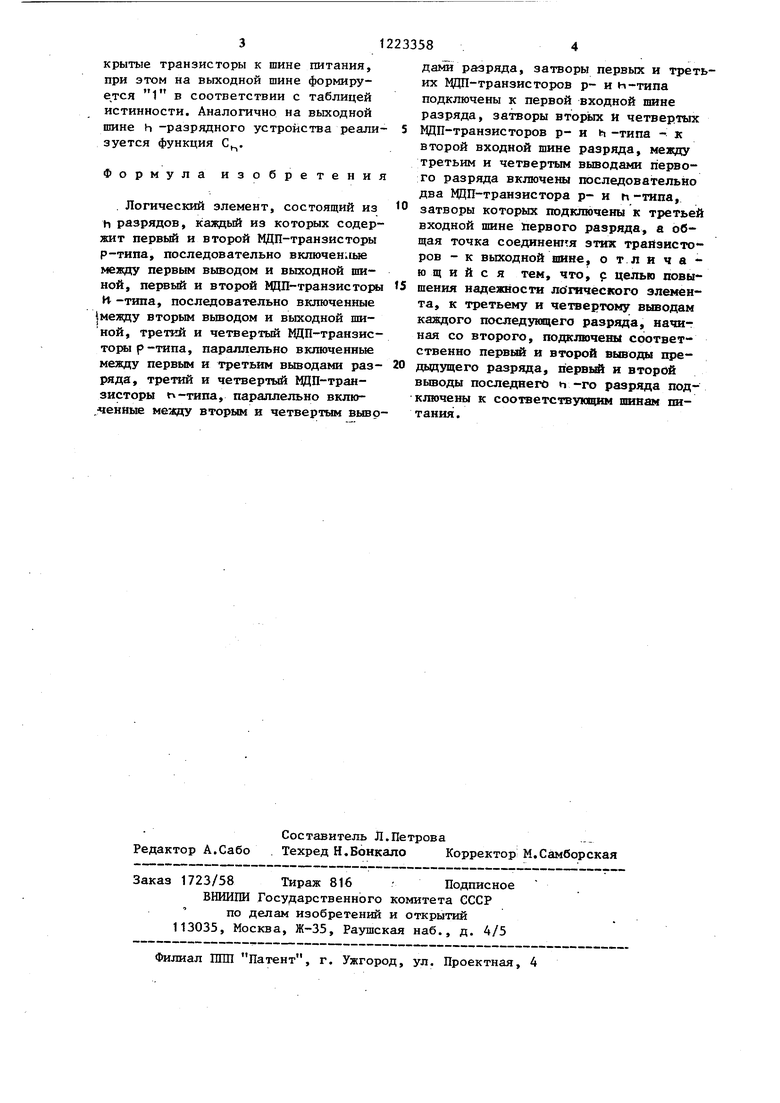

На чертеже представлена электрическая принципиальная схема устройства, содержащего три идентичных раз ряда 1, каждый из которых содержит первый и второй ВДП-транзисторы р-ти па 2 и 3, последовательно включенные между первым вьшодом 4 и выходной шиной 5, первый и второй МДП-транзис торы и -типа б и 7, последовательно включенные между вторым выводом 8 и выходной НИНОЙ 5, третий и четвертьй МДП-транзисторы р-типа 9 и 10, па- ращгельно включенные между лервым 4 и третьим 11 выводами разряда, третий и четвертый ЩП-транзисторы и- тила 12 и 13 параллельно включенные между вторым 8 и четвертым 14 выводами разряда, затворы первых 2 и 6 и третьих 9. и 12 ЩП-транзисторов р- ИИ -типа подключены к первой входной шине разряда 15, затворы вторых 3 и 7 и четвертых 10 и 13 ВДП-транзисторов р- и и-типа - к второй входной шине 16 разряда, между третьим 11 и четвертым 14 выfDiiMiB J Miti&iy®

о 000 о 1 о 1 110 1 1 1 00100101110111 01000101110111 01100101010011 10000101 1101 11 10100101010011 11000101010011 11100101010011

Из таблицы истинности следует, что при всех возможных наборах сигналов А, В, Aj, В,, значение функции Cj соответствует выражению (2).

водами первого разряда включены последовательно два МДП-транзистора р- и h-типа 17 и 18, затворы которых подключены к третьей входной шине 19

первого разряда, а общая точка соединения этих транзисторов - -к выходной шине 5, к третьему 11 и четвертому 14 вьшодам каждого последующего разряда, начиная со второго, подключены, соответственно, первый 4 и второй 8 вью оды предыдущего разряда, первый 4 и второй 8 выводы последнего (третьего) разряда подключены к соответствующим шинам питания.

Устройство работает следующим образом.

На первую входную шину 15 каждого из разрядов 1 поступают соответственно сигналы Aj., А,..., А, на вторую

входную шину 16 - сигналы В;,, Bjj,...,

В, на третью входную шину 19 первого разряда поступает сигнАл С. На выходной шине 5 h -разрядного устрой- сТВа реализуется функция

CK- и & и ( 6 J{A., В„.,+.. ().С,};

(.1)

в частности, для двухразрядного устройства

c, Aj (, Б,ЧА,®В,) сЛ

(2

Например, при значении входных сигналов ,А, открыты все транзисторы р-типа и выходная щи- на устройства подключена- через открытые транзисторы к шине питания, при этом на выходной шине формиру- 1 в соответствии с таблицей истинности. Аналогично на выходной шине h -разрядного устройства реализуется функция С

Ь

о р м у л а

изобретения

. Логический элемент, состоящий из h разрядов, каждый из которых содержит первый и второй МДП-транзисторы р-типа, последовательно включен ше между первым выводом и выходной шиной, первый и второй МДП-транзисторяя К -типа, последовательно включенные

|между вторым вьшодом и выходной шиной, третий и четвертый ВДП-транзис- р -типа, параллельно включенные между первым и третьим выводами разряда, третий и четвертый ОДП-тран- зисторы м-типа, параллельно вклю.ченные вторым и четвертым выврРедактор А.Сабо

Составитель Л.Петрова

Техред Н.Бонкало Корректор М.Самборская

Заказ 1723/58 Тираж 816 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Филиал ШШ Патент, г. Ужгород, ул. Проектная,

0

дани разряда, затворы первых и третьих ВДП-транзисторов р- и и-типа подключены к первой входной шине разряда, затворы вторых И четвертых 5 МДП-транзисторов р- и h -типа - к второй входной шине разряда, между третьим и четвертым выводами первого разряда включены последовательно два ЩП-транзистора р- и 1ч -типа, затворы которых подключены к третьей входной шине первого разряда, а общая точка соединештя этих трайзисторов - к выходной шине, отличающийся тем, что, с целью повышения надежности логического элемента, к третьему и четвертому выводам каждого последзтющего разряда, начиная со второго, подключены соответственно первый и второй выводы предыдущего разряда, первый и второй выводы последнего м -го разряда подключены к соответствзгеицш шинам питания .

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный коммутатор | 1985 |

|

SU1246362A1 |

| Преобразователь уровня | 1987 |

|

SU1471289A1 |

| Ключ на МДП-транзисторе | 1986 |

|

SU1610597A1 |

| Формирователь импульсов с преобразованием уровней сигналов | 1985 |

|

SU1378030A1 |

| Устройство для формирования группового переноса | 1985 |

|

SU1335981A1 |

| Преобразователь переменного напряжения в постоянное | 1986 |

|

SU1363406A1 |

| Одноразрядный двоичный сумматор | 1983 |

|

SU1149249A1 |

| Формирователь импульсов | 1987 |

|

SU1431054A1 |

| Электронный ключ | 1987 |

|

SU1465999A1 |

| Устройство реверсирования тока | 1985 |

|

SU1246359A1 |

Изобретение относится к вычислительной технике и может быть ис пользовано в качестве формирователя переноса в устройствах суммирования и вычитания. Цель изобретения - повышение надежности устройства. Устройство Содержит три идентичных разряда 1. Между первым выводом 4 и выходной шиной 5 включены первый и второй ВДП-транзисторы р-типа 2 и 3. Между вторым вьюодом 8 и выходной шиной 5 включены первый и второй МДП-транзисторы h-типа 6 и 7. Третий и четвертый ЩП-транзисторы р-типа 9 и 10 включены -первым 4 и третьим 11 вьгоодами разряда, а третий и чет- вертьй МДП-транзисторы h -типа.12 и 13 - между вторым 8 и четвертым 14 вьшодами разряда. К первой входной шине разряда 15 подключены затворы первых 2 и 6 и третьих 9 н 12 ЩЕ- транзисторов р- и ь-типа, к второй входной шине 16 разряда. - затворы вторых 3 и 7 и четвертых 10 и 13 МДП-транзисторов р- и н-типа. Затворы НДП-транзисторов р- и ъ-типа 17 и 18 подключены к входной шине 19 первого разряда; 1 ил.

| Мейзда Ф | |||

| Интегральные схемы | |||

| М.: Мир, 1981, с | |||

| Прибор для очистки паром от сажи дымогарных трубок в паровозных котлах | 1913 |

|

SU95A1 |

| Валиев К.А | |||

| Цифровые интегральные схемы на МДП-транзисторгах | |||

| Советское радио | |||

| Устройство станционной централизации и блокировочной сигнализации | 1915 |

|

SU1971A1 |

| Ленточный тормозной башмак | 1922 |

|

SU337A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1986-04-07—Публикация

1984-04-05—Подача