11У

Изобретение относится к г1втоматике и пычислительной технике и может использовано в устройствах суммирования, вычитания и сравнения.

Цель изобретения - упрощение устройства.

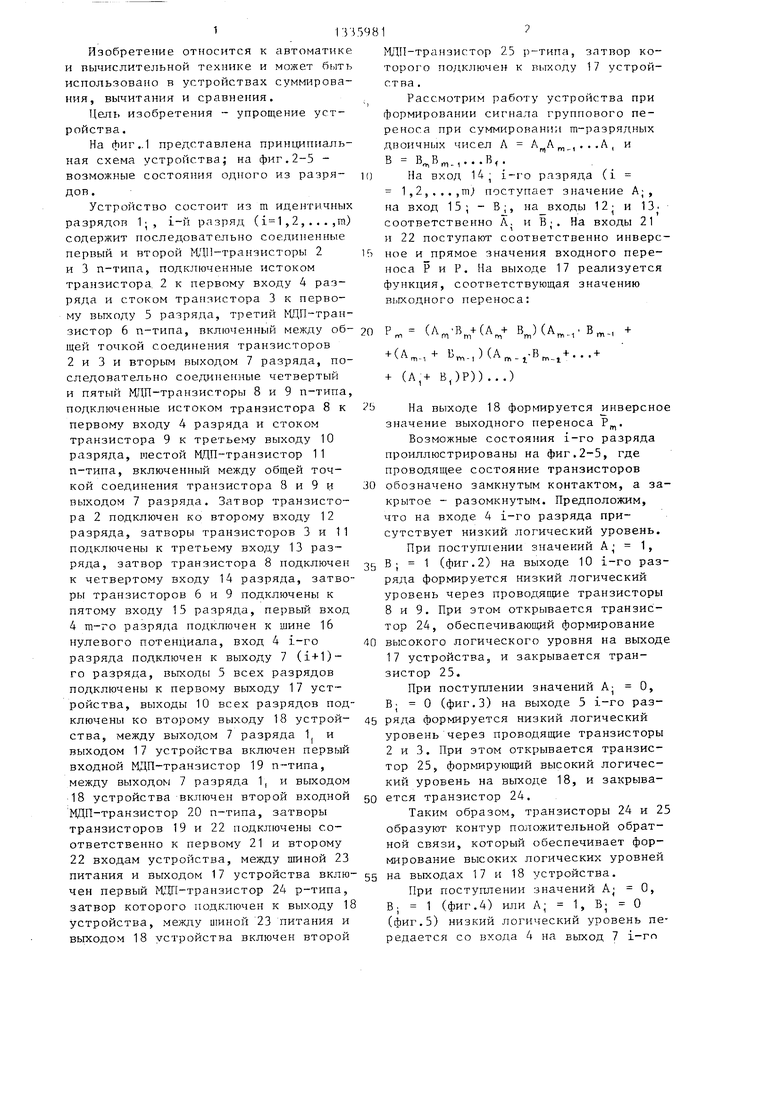

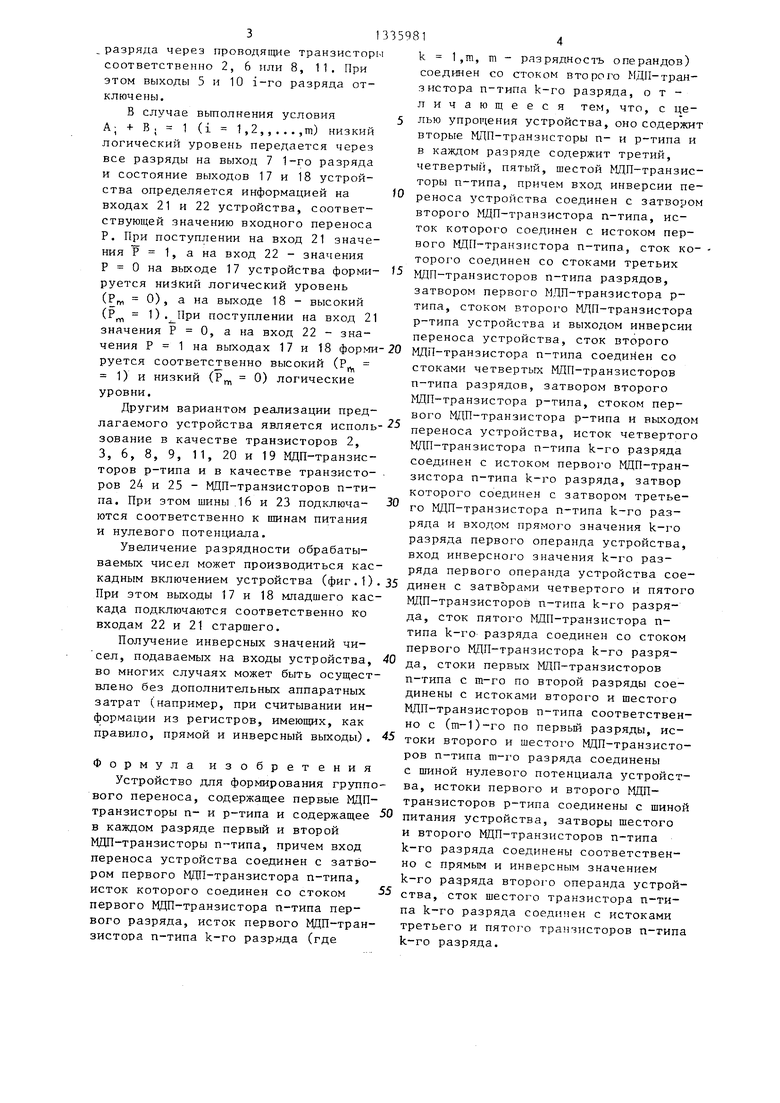

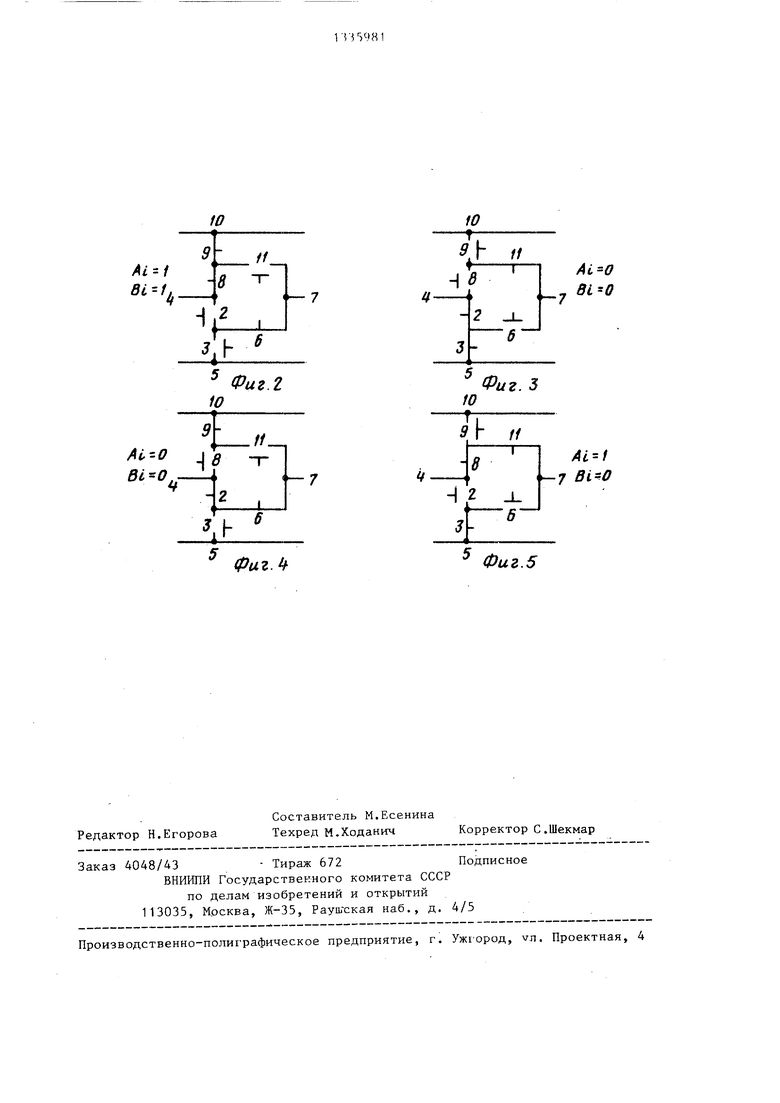

На фиг..1 представлена принципиальная схема устройства; на фиг.2-5 - возможные состояния одного из разрядов.

Устройство состоит из m идентичных разрядов 1;, i-й разряд (,2,...,т) содержит последовательно соединенные первый и второй МДП-транзисторы 2 и 3 п-типа, подключенные истоком тра} зистора 2 к первому входу 4 разряда и стоком транзистора 3 к первому выходу 5 разряда, третий ЩП-тран- зистор 6 п-типа, включенный между общей точкой соединения транзисторов 2 и 3 и вторым выходом 7 разряда, последовательно соединенные четвертый и пятый ИДП-транзисторы 8 и 9 п-типа, подключенные истоком транзистора 8 к первому входу 4 разряда и стоком транзистора 9 к третьему выходу 10 разряда, шестой МДП-транзистор 11 п-типа, включенный между общей точкой соединения транзистора 8 и 9 и выходом 7 разряда. Затвор транзистора 2 подключен ко второму входу 12 разряда, затворы транзисторов 3 и 11 подключены к третьему входу 13 разряда, затвор транзистора 8 подключен к четвертому входу 14 разряда, затворы транзисторов 6 и 9 подключены к пятому входу 15 разряда, первый вход 4 т-го разряда подключен к шине 16 нулевого потенциала, вход 4 i-ro разряда подключен к выходу 7 (i+1)- го разряда, выходы 5 всех разрядов подключены к первому выходу 17 устройства, выходы 10 всех разрядов подключены ко второму выходу 18 устройства, между выходом 7 разряда 1 и выходом 17 устройства включен первый входной МДП-транзистор 19 п-типа, между выходом 7 разряда 1, и выходом 18 устройства включен второй входной МДП-транзистор 20 п-типа, затворы транзисторов 19 и 22 подключены соответственно к первому 21 и второму 22 входам устройства, между шиной 23 питания и выходом 17 устройства включен первый МДП-трапэистор 24 р-типа, затвор которого подключен к выходу 18 устройства, между тиной 23 питания и выходом 18 устройства включен второй

1

МДП-транзистор 25 р-типа, затвор которого подключен к выходу 17 устройства .

Рассмотрим работу устройства при формировании сигнала группового переноса при суммировании т-разрядных двоичных чисел Л ,...Л, и

в ,...в,.

На вход 14; i-ro разряда (i l,2,...,nij поступает значение А;, на вход 15; - Bj, на входы 12; и 13. соответственно А, и В;. На входы 21 и 22 поступают соответственно инверсное и прямое значения входного переноса Р и Р. На выходе 17 реализуется функция, соответствующая значению выходного переноса:

Р (( В„)(А„,. В„, + + (А„.,+ В.,)(А....+ + (А,+ В,,)Р)) ...)

На выходе 18 формируется инверсное значение выходного переноса Р.

Возможные состояния i-ro разряда проиллюстрированы на фиг.2-5, где проводящее состояние транзисторов

обозначено замкнутым контактом, а закрытое - разомкнутым. Предположим, что на входе 4 i-ro разряда присутствует низкий логический уровень. При поступлении значений А; 1,

В ; 1 (фиг.2) на выходе 10 i-ro разряда формируется низкий логический уровень через проводящие транзисторы 8 и 9. При этом открЕ геается транзис;- тор 24, обеспечиваюищй формирование

высокого логического уровня на выходе 17 устройства, и закрывается транзистор 25.

При поступлении значений А О, В; 0 (фиг.З) на выходе 5 1-го разряда формируется низкий логический уровень через проводящие транзисторы 2 и 3. При этом открывается транзистор 25, формирующий высокий логический уровень на выходе 18, и закрывается транзистор 24.

Таким образом, транзисторы 24 и 25 образуют контур положительной обратной связи, который обеспечивает формирование высоких логических уровней

на выходах 17 и 18 устройства.

При поступлении значений А; 0, В; 1 (фиг.4) или А; 1, В; О (фиг.5) низкий логический уровень передается со входа 4 на выход 7 i-rn

разряда через проводя1цие транзисторы соответственно 2, 6 или 8, 11. При этом выходы 5 и 10 а-го разряда отключены.

В случае вьшолнения условия А; + В, 1 (i 1,2,,...,m) низкий логический уровень передается через все разряды на выход 7 1-го разряда и состояние выходов 17 и 18 устройства определяется информацией на входах 21 и 22 устройства, соответствующей значению входного переноса Р. При поступлении на вход 21 значения F 1, а на вход 22 - значения

k 1,m, m - рязрядноС1Ъ операндов) соединен со стоком второго МДП-тран- зистора п-типа k-ro разряда, отличающееся тем, что, с целью упрощения устрорЧства, оно содержит вторые МДП-транзисторы п- и р-типа и в каждом разряде содержит третий, четвертый, пятый, шестой МДП-транзис торы п-типа, причем вход инверсии пе реноса устройства соединен с затворо второго МДП-транзистора п-типа, исток которого соединен с истоком первого МДП-транзпстора п-типа, сток ко торого соединен со стоками третьих

)0

Р О на выходе 17 устройства форми- )5 1адп-транзисторов п-типа разрядов, руется низкий логический уровень затвором первого МДП-транзистора р- (Р„ 0), а на вькоде 18 - высокий (Р 1). При поступлении на вход 21

значения Р О, а на вход 22 - знатипа, стоком второго ОДП-транзистора р-типа устройства и выходом инверсии переноса устройства, сток второго чения Р 1 на выходах 17 и 18 форми-20 МДП-транзистора п-типа соединен со руется соответс твенно высокий (Р стоками четвертых МДП-транзисторов 1) и низкий ( 0) логические уровни.

Другим вариантом реализации пред-25

лагаемого устройства является исполь зование в качестве транзисторов 2, 3, 6, 8, 9, 11, 20 и 19 МДП-транзисторов р-типа и в качестве транзисторов 24 и 25 - МДП-транзисторов п-типа. При зтом шины .16 и 23 подключаются соответственно к шинам питания и нулевого потенциала.

Увеличение разрядности обрабаты30

п-типа разрядов, затвором второго МДП-транзистора р-типа, стоком первого МДП-транзистора р-типа и выходом переноса устройства, исток четвертог МДП-транзистора п-типа k-ro разряда соединен с истоком первого МДП-транзистора п-типа k-ro разряда, затвор которого соединен с затвором третьего МДП-транзистора п-типа k-ro разряда и входом прямого значения k-ro разряда первого операнда устройства, вход инверсного значения k-ro разряда первого операнда устройства соеп-типа разрядов, затвором второго МДП-транзистора р-типа, стоком первого МДП-транзистора р-типа и выходом переноса устройства, исток четвертого МДП-транзистора п-типа k-ro разряда соединен с истоком первого МДП-транзистора п-типа k-ro разряда, затвор которого соединен с затвором третьего МДП-транзистора п-типа k-ro разряда и входом прямого значения k-ro разряда первого операнда устройства, вход инверсного значения k-ro разряда первого операнда устройства соеда, сток пятого МДП-транзистора п- типа k-ro разряда соединен со стоком первого МДП-транзистора k-ro разряваемых чисел может производиться каскадным включением устройства (фиг.1).35 динен с затворами четвертого и пятого При этом выходы 17 и 18 младшего кас- МДП-транзисторов п-типа k-ro разря- када подключаются соответственно ко входам 22 и 21 старшего.

Получение инверсных значений чи сел, подаваемых на входы устройства, 40 д стоки первых МЦП-транзисторов во многих случаях может быть осущест- п-типа с т-го по второй разряды сое- влено без дополнительных аппаратных динены с истоками второго и шестого затрат (например, при считывании ий- МДП-транзисторов п-типа соответствен- формаггии из регистров, имеющих, как но с (m-l)-ro по первый разряды, исправило, прямой и инверсный выходы). 45 токи второго и шестого МДП-транзисторов п-типа m-ro разряда соединены Формула изобретения с шиной нулевого потенциала устройстУстройство для формирования группе- ва, истоки первого и второго МДП- вого переноса, содержащее первые МДП- транзисторы п- и р-типа и содержащее -50 в каждом разряде первый и второй МДП-транзисторы п-типа, причем вход переноса устройства соединен с затвором первого МДП-транзистора п-типа.

транзисторов р-типа соединены с шиной питания устройства, затворы шестого и второго МДП-транзисторов п-типа k-ro разряда соединены соответственно с прямым и инверсным значением k-ro разряда второго операнда устройисток которого соединен со стоком первого МДП-транзистора п-типа первого разряда, исток первого МДП-транзистора п-типа k-ro разряда (где

359814

k 1,m, m - рязрядноС1Ъ операндов) соединен со стоком второго МДП-тран- зистора п-типа k-ro разряда, отличающееся тем, что, с целью упрощения устрорЧства, оно содержит вторые МДП-транзисторы п- и р-типа и в каждом разряде содержит третий, четвертый, пятый, шестой МДП-транзисторы п-типа, причем вход инверсии переноса устройства соединен с затвором второго МДП-транзистора п-типа, исток которого соединен с истоком первого МДП-транзпстора п-типа, сток которого соединен со стоками третьих

)0

)5 1адп-транзисторов п-типа разрядов, затвором первого МДП-транзистора р-

типа, стоком второго ОДП-транзистора р-типа устройства и выходом инверсии переноса устройства, сток второго МДП-транзистора п-типа соединен со стоками четвертых МДП-транзисторов

п-типа разрядов, затвором второго МДП-транзистора р-типа, стоком первого МДП-транзистора р-типа и выходом переноса устройства, исток четвертого МДП-транзистора п-типа k-ro разряда соединен с истоком первого МДП-транзистора п-типа k-ro разряда, затвор которого соединен с затвором третьего МДП-транзистора п-типа k-ro разряда и входом прямого значения k-ro разряда первого операнда устройства, вход инверсного значения k-ro разряда первого операнда устройства соединен с затворами четвертого и пятого МДП-транзисторов п-типа k-ro разря-

да, сток пятого МДП-транзистора п- типа k-ro разряда соединен со стоком первого МДП-транзистора k-ro разрядинен с затворами четвертого и пятого МДП-транзисторов п-типа k-ro разря-

д стоки первых МЦП-транзисторов п-типа с т-го по второй разряды сое- динены с истоками второго и шестого МДП-транзисторов п-типа соответствен- но с (m-l)-ro по первый разряды, истоки второго и шестого МДП-транзисторов п-типа m-ro разряда соединены с шиной нулевого потенциала устройства, истоки первого и второго МДП-

транзисторов р-типа соединены с шиной питания устройства, затворы шестого и второго МДП-транзисторов п-типа k-ro разряда соединены соответственно с прямым и инверсным значением k-ro разряда второго операнда устройства, сток шестого транзистора п-типа k-ro разряда соединен с истоками третьего и пятого транзисторов п-типа k-ro разряда.

Ai -i ,

Ai-0 Bi-0.

Фиг.г

W

,9 H

-1

Ah

ф{лгЛ

Редактор Н.Егорова

Составитель М.Есенина Техред М.Ходанкч

Заказ 4048/43 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Рауш-ская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужг ород, vn. Проектная, 4

Фиг.5

Корректор С.Шекмар

| название | год | авторы | номер документа |

|---|---|---|---|

| Сумматор | 1986 |

|

SU1406591A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1287147A1 |

| Одноразрядный двоичный сумматор | 1983 |

|

SU1149249A1 |

| СУММАТОР | 1994 |

|

RU2049346C1 |

| Формирователь переноса | 1990 |

|

SU1702361A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1312567A1 |

| Сумматор по модулю два | 1984 |

|

SU1191906A1 |

| Формирователь переноса | 1991 |

|

SU1798778A1 |

| Арифметико-логическое устройство | 1987 |

|

SU1481742A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1291969A1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при разработке устройств сложения, арифметико-логических устройств и т.п. в составе интегральных схем на ЩЦП-транзисторах и отличается малым количеством используемых транзисторов. Цель изобретения - упрощение устройства. Устройство содержит m идентичных разрядов 1; (i 1,2...m), выполненных на МДП- транзисторах п-типа проводимости. На входы 14; и 15; поступают значения i-x разрядов соответственно первого и второго чисел, на входы 12; и 13; - их инверсные значения. На входы 21 и 22 поступают соответственно инверсное и прямое значения входного переноса. Сигнал группового переноса и его инверсное значение формируются соответственно на выходах 17 и 18, к которым подключены транзисторы 24 и 25 второго типа проводимости. 5 ил, (Л ей 22 СО СО СП 00 ЗГ-

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент США № 4425623, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Колосниковая решетка с чередующимися неподвижными и движущимися возвратно-поступательно колосниками | 1917 |

|

SU1984A1 |

Авторы

Даты

1987-09-07—Публикация

1985-12-27—Подача