ром второго МДП-транзистора л-типа и подключен к второму входу синхронизации сумматора, стрк соединен с шиной питания сумматора, а исток

соединен с истоком шестого 1УЩП-транзистора р-типа, стоки первого и второго МДП-транзисторов п -типа соединены с нулевой шиной сумматора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь импульсов | 1987 |

|

SU1431054A1 |

| Одноразрядный сумматор | 1983 |

|

SU1117634A1 |

| Сумматор | 1983 |

|

SU1100620A1 |

| Сумматор по модулю два | 1984 |

|

SU1191906A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1287147A1 |

| Сумматор | 1986 |

|

SU1406591A1 |

| Узел формирования переноса в сумматоре | 1985 |

|

SU1291969A1 |

| ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУММАТОР | 2009 |

|

RU2408922C1 |

| Комбинационный сумматор | 1988 |

|

SU1596321A1 |

| ОДНОРАЗРЯДНЫЙ СУММАТОР | 2009 |

|

RU2408058C2 |

ОДНОРАЗРЯДНЫЙ ДВОИЧНЫЙ СУШ&ТОр, содержащий узел формирования СУ1ФШ и узел формирования переноса, причем узел формирования суммы содержит НДП-транзисторы р-типа с первого по пятый и первый ЬЩП-траизистор п-типа, а узел формирования переноса содержит ЦЦП-траизисторы р-типа с шестого по десятый и второй ВДП-транзисторы л-типа, затворы -первого, второго и третьего ЬЩПтранзистора р-типа соединены соответственно с входами первого, второго и третьего слагаемых сумматора, сток первого ОДП-транзистора р-типа соедаснен с истоком второго ЩП-транзистора р-типа, сток которого соединен со стоком третьего 1Щ1транзистора р-типа, со стоком первого МДП-транзистора п-типа и подключен к инверсному выходу переноса сумматора, исток третьего ВДП-транзистора р-типа соединен со стокаьш четвертого и пятого ОДПтранзисторов р-типа, истоки которых соединены с истоком первого ВДП-транзистора р-типа, а затворы соединены соответственно с входами первого и второго слагаемых сумматора, сток шестого МДП-транзистора р-типа соединен со стоком седьмого НДП-транзнстора р-типа и с истоком восьмого ВДП-транзистора р-типа, затвор которого соединен с входом первого слагаемого .сумматора, а сток подключен к стоку девятого МДП-транзистора р-типа и второго МДП-транзистора п-типа и соединен с инверсным выходом суммы сумматора, затворы седьмого и восьмого МЦП-транзисторов р-типа соединены соответственно с входами второго и первого слагаемых сумматора, исток седьмого i ВДП-транзистора р-типа соедийен (Л с истоком девятого и со стоком десятого ВДП-транзисторов р-типа, затвор шестого ВДП-транзистора р-типа соединен с затвором девятого НЦП-транзистора .р-типа и подключен к стоку второго ВДП-транзистора р-типа, затвор десятого ВДП-транзистора р-типа соединен с входом 4i третьего слагаемого сумматора, а СО исток соединен с истоком шестого ч to ВДП-транзистора р-типа, отли( чающийся тем, что, с целью со упрощения его конструкции, он содержит одиннадцатый и двенадцатый ВДП-транзисторы р-типа, причем затвор одиннадцатого ВДП-транзистора Р-типа соединен с затвором первого ЩП-тpaнзиcтopa п-типа и подключен к первому входу синхронизации сумматора, исток соединен с истоком первого ВДП-транзистора р-тйпа, а сток подключен к шине питания сумматора, затвор двенадцатого ВДПтранзистора р-типа соединен с затво

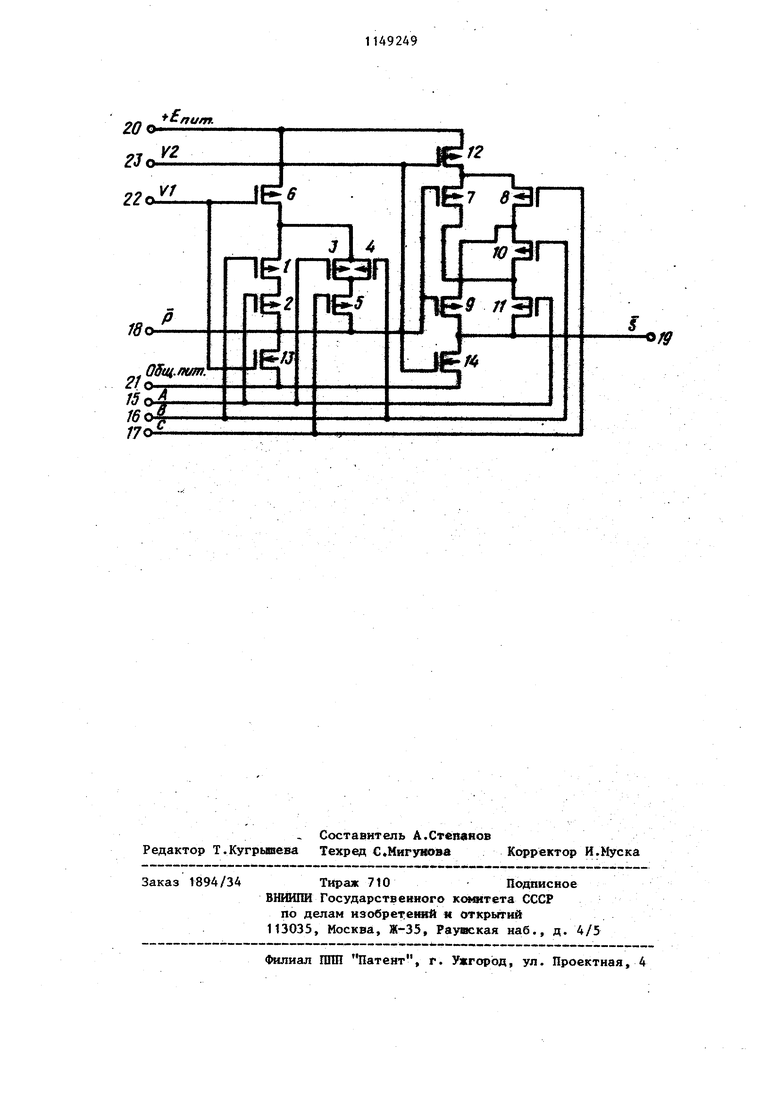

Изобретение относится к вычислительной технике и может быть использовано при создании больших интеграл ных схем (БИС) обработки цифровой информации. Известе н сумматор на ЩП-транзисторах, содержащий узел формирования суммы, содержащий восемь ЩП-транзисторов п -типа и восемь ВДП-транзисторов р-типа, и узел формироваНИН переноса, содержащий два ВДПтранзистора л -типа и два ЩП-тран зистора р -типа j. Недостатком данного сумматора является сложность конструкции, ЙЫражающаяся в большом количестве ВДП-транзисторов, используемых в сумматоре. Наиболее близким к предлагаемому по технической сущности является од норазрядный двоичный сумматор, содержащий узел формирования суммы и узел формирования переноса, причем узел формирования суммы содержит ВДП-транзиСторы р-типа с первого по пятьй и первый МДП-транзистор ti -типа, а узел формирования перено са содержит МДП-транзисторы р-тип с шестого по десятый и второй МДП-транзистор ц-типа, затворы первого, второго и третьего МДП-тра зисторов р-типа соединены соответ ственно с входами первого, второго и третьего слагаемых думматора, сток первого ЩП-транзистора р-ти соединен с истоком второго НЦП-тран зистора р-типа, сток которого сое динен со стоком третьего НЦП-транзистора р-типа, со стоком первого НДП-транзистора п-типа и подключе к инверсному выходу переноса сумматора, исток третьего ВДП-транзистор р-типа соединен со стоками четвертого и пятого МДП-транзисторов р-типа, истоки которых соединены с истоком первого 1уЩП-транзистора р-типа, а затворы соединены соответственно с входами первого и второго слагаемых сумматора, сток шее- того ЩЩ-транзистора р -типа соединен со стоком седьмого МЦП-транзистора р-типа и с истоком восьмого МДП-транзистора р-типа, затвор которого соединен с входом первого слагаемого сумматора, а сток подключен к стоку девятого МДП-транзистора р -типа и второго НДПтранзистора h -типа и соединен с инверсным выходе суммы сумматора, затворы седьмого и восьмого ВДПтранзисторов р-типа соединены соответственно с входами второго и первого слагаемых сумматора, исток седьмого ВДП-транэистора р-типа соединен с истоком девятого и со стоком десятого МЦП-транзисторов р-типа, затвор шестого МДПтранзистора р-типа соединен с затвором девятого ЩП-транзистора р-типа и подключен к стоку второго МДП-транзистора р-типа, затвор десятого ВДП-транзистора р-типа соединен с входом третьего слагаемого сумматора, а исток соединен с истоком шестого ВДП-транзистора р -типа, сумматор содержит дополнительно МДП-транзисторы п-типа с третьего по десятый С2 JНедостатком известного сумматора является сложность конструкции, выражающаяся в большом количестве использованных ВДП-транзисторов. Цель изобретения - упрощение конструкции одноразрядного двоичного сумматора. Поставленная цель достигается тем, что одноразрядный двоичный сумматор, содержащий узел формирования суммы и узел формирования переноса, причем узел формирования суммы содержит ВДП-транзисторы Р -типа с первого по пятый и первый МДП-транзистор n-типа, а узел фор мирования переноса содержит ЩИтранзисторы р-типа с шестого по десятый и второй ВДП-транзисторы П -типа, затворы первого, второго и третьего ЩП-тpaнзиcтopoв р-типа соединены соответственно с входами первого, второго и третьего слагаемых сумматора, сток первого ЩПтранзистора р-типа соединен с исто ком второго МДП-транзистора р -типа сток которого соединен со стоком третьего ВДП-транзистора р-типа, со стоком первого НЦП-транзистора -типа и подключен к инверсному вы ходу переноса сумматора, исток третьего ОДП-транзистора р-типа соединен со-стоками четвертого и пятого ЩЩ-транзисторов р-типа, истоки которых соединены с истоком первого ЩП-транзистора р-типа, а затворы соединены соответственно G входами первого и второго слагае: мых сумматора, сток шестого МДПтранзистора р-типа соединен со стоком седьмого ВДП-транзистора р-типа и с истоком восьмого ГОДПтранзистора р-типа, затвор которо го соединен с входом первого слагае мого сумматора, а сток подключен к стоку девятого ВДП-транзистора р -типа и второго ЩП-транзистора п-типа и соединен с инверсным выходом суммы сумматора, затворы седьмого и восьмого ЩЩ-транзистора р-типа соединены соответственно с входами второго и первого слагаемых сумматора, исток седьмого ОДП-транзистора р-тнпа соединен с истоке девятого и со стоком десятого ЩП-транзисторов р-типа, затвор шестого МДП-транзистора р-типа соединен с затвором девятого МДП-транзистора р-типа и подключен к стоку второго ЩП-транзистора р-типа, затвор десятого ВДП-транзистора р-типа соединен . с входом третьего слагаемого cy мaтора, а исток соединен с истоком шестого НЦП-транзистора р-типа, сумматор содержит одиннадцатый и двенадцатый ЩП-транзисторы р-типа, причем затвор одиннадцатого ВДП-транзистора р-типа соединен с затвором первого ЩП-транзистора h -типа и подключен к первому входу синхронизации сумматора, исток соединен с истоком первого ЩЩ-транзистора р-типа, а сток подключен к шине питания сумматора, затвор двенадцатого ВДП-транзистора р -типа соединен с затвором второго ЩПтранзистора n-типа и подключен к второму входу синхронизации сумматора, сток соединен с шиной питания сумматора, а исток - с истоком шестого ЩП-транзистора р-типа, стоки первого и второго ЩП-транзисторов n-типа соединены с нулевой шиной сумматора. На чертеже представлена принципиальная схема одноразрядного двоичного сумматора. Сумматор содержит ЩП-транзисторы 1-12 р-типа, ЩП-транзисторы 13 и 14 п-типа, входы слагаемых 15-17, выход 18 переноса, выход 19 суммы, шину 20 питания, нулевую шину 21, а также первый и второй входы 22 и 23 синхронизации. Сумматор работает следуювщм образом. На вход 22 подается сигнал уровня логической 1, при этом на выходе 15 и на затворах транзисторов 7 и 9 накапливается отрнцательцый заряд. Далее подаются сигналы слагаемых на входы15-17, и узел формирования переноса на транзисторах 1-6 и 13 вырабатывает инверсный сигнал переноса на выходе 18.. На вход 22 при этом подается сигнал уровня логического О. Далее на вход 23 поступает сигнал уровня логической 1 и на выходе 19 накапливается отрицательный потенгщал. Затем на вход 23 подается сигнал логического О, и узел форьшрования суммы на транзисторах 7-12 вьфабатывает инверсное значение суммы на выходе 19. По сравнению с известным предлагаемый сумматор содержит на 30% меньше ЩП-транзисторов, что вызывает также повышение надежности сумматора. 20 22 -num.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Одноразрядный двоичный сумматор | 1980 |

|

SU943712A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Одноразрядный двоичный сумматор на комплементарных МДП-транзисторах | 1982 |

|

SU1034031A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-04-07—Публикация

1983-11-05—Подача