Изобретение относится к радиотехнике, может быть использовано в качестве устройства переменной задержки управляемого посредством внешнего датчика кода.

Цель изобретения - расширение функциональных возможностей устройства за счет обеспечения перестраиваемой (с заданным дискретом) задержки пакета цифровой информации.

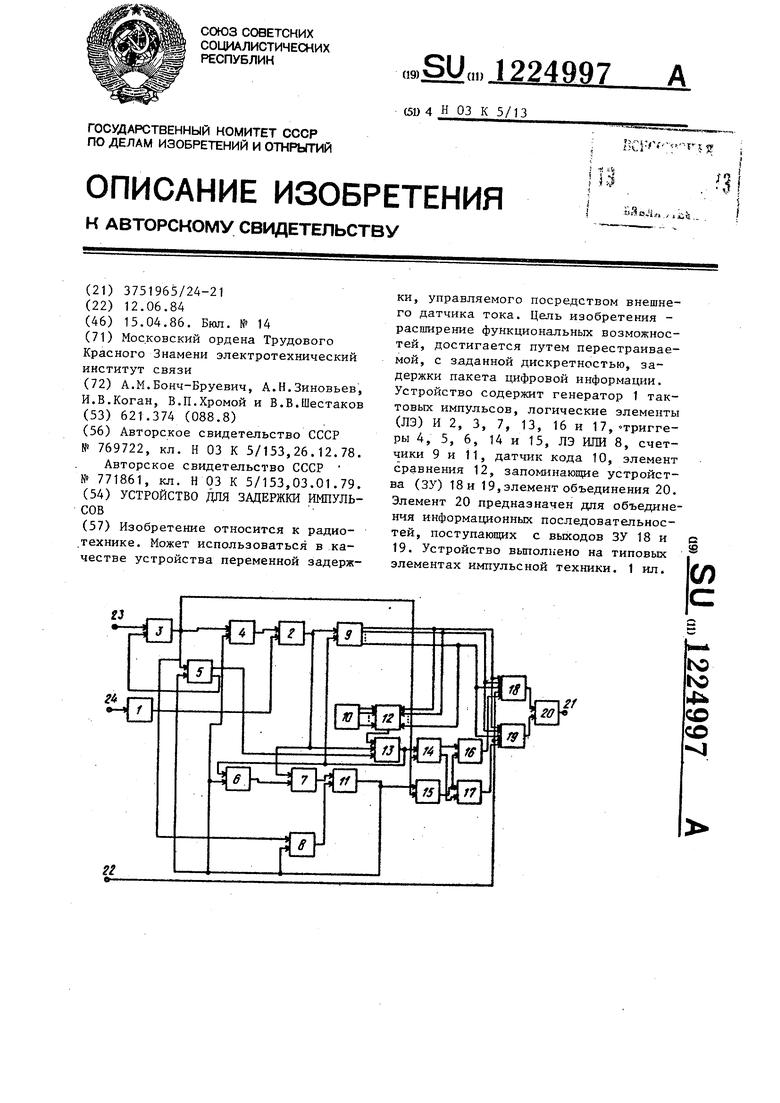

На чертеже представлена структурная электрическая схема предлагаемого устройства.

Устройство содержит генератор 1 тактовых импульсов, первьй 2 и второй 3 элементы И, первьм 4, второй 5 и третий 6 триггеры, третий элемент И 7, элемент ИЛИ 8, первьм счетчик 9, датчик 10 кода, второй Счетчик 11, элемент 12.сравнения, четвертый элемент И 13, четвертьш 14 и пятый 15 триггеры, пятьш 16 и шестой 17 элементы И,первое 18 и второе 19 запоминающие устройства,элемент 20 объединения.

Выход генератора 1 тактовых импульсов подключен к первому входу элемента И 2, выход второго элементе И 3 соединен с единичными входами первого триггера 4 и второго триггера 5, первым входом элемента ИЛИ 8, нулевыми входами четвертого 14 и пятого 15 триггеров. Инверсньй выход второго триггера 5 соединен со вторым входом второго элемента И 3, а прямой выход соединен с третьим входом четвертого элемента И 13. Второй вход первого элемента И 2 соединен с прямым выходом первого триггера 4, а выход соединен со счетным входом первого счетчика 9, вторым входом четвертого элемента И 13, а также с первым входом третьего элемента И 7, выход которого соединен со счетным входом второго счетчика 11, выход которого соединен с нулевыми входами первого 4, второго 5, третьего 6 триггера, с единичным входом пятого триггера 15 а также со вторым входом элемента И.ПИ 8, выход которого соединен с обнуляющим входом второго счетчика 11. Адресные входы первого запоминающего устройства 18 соединены с адресными входами второго запоминающего устройства 19 и с выходами первого счетчика 9, соединенными с первой группой входов элемента 12 сравнения кодов, вторая группа ЕХОДОВ которого соединена с датчиком 10 кода, а выход - с первым входом четвертого элемента И 13, выход которого соединен со счетным входом четвертого триггера 14 с обнуляющим входом первого счетчика 9, а также с единичным входом третьего триггера 6, прямой выход которого соединен со вторым входом третьего элемента И 7. Прямой выход четвертого триггера 14 соединен с первым входом пятого элемента И 16, а инверсный выход соединен со вторым входом

шестого элемента И 17. Инверсный выход пятого триггера 15 соединен с первым входом шестого элемента И 17 и со вторьм входом пятого элемента И 16, выход которого, соединен с управляющим входом Запись-считывание первого запоминающего устройства 18. Выход- шестого элемента И 17 соединен с управляюпрм входом Запись- считьюание второго запоминающего.

устройства 19.

Выходы первого и второго запоминающих устройств 18 и 19 соединены со входами элемента объединения 20, вы- ход которого является выходом 21

устройства.

Объединенные информационные входы первого 18 и второго 19 запоминающих устройств являются информационным входом 22 устройства для задержки

импульсов, первый вход второго элемента И 3 и вход генератора 1 тактовых импульсов являются соответственно его первым 23 и вторым 24 управляющими входами.

Используемые в устройстве элементы являются известными типовыми элементами импульсной техники.

Генератор 1 тактовых импульсов может быть выполнен по любой из известных схем с использованием фазовой автоподстройки частоты по импульсной последовательности, поступающей на устройство со второго управляющего входа 24.

Элемент объединения 20 предназначен для объединения информационных последовательностей, поступающих с выходов первого 18 и второго 19 запоминающих устройств, может быть

выполнен, например, в виде элемента ИЛИ.

Устройство задержки импульсов работает следующим образом.

3

в исходном состоянии первый 4, второй 5 и третий 6 триггеры и пер вьш счетчик 9 находятся в нулевом состоянии. Первый 2, второй 3, третий 7 и четвертый 13 элементы И закрыты, на обоих входах элемента ИЛИ 8 сигнал отсутствует. Код задержки с датчика кода 10 подается на первую группу входов элемента сравнения кодов 12. Импульс, определяющий начало пакета, через второй элемент И 3 подается на единичный вход первого триггера 4, на единичный вход второго триггера 5, на нулевые входы четвертого 14 и пятого 15 триггеров, а также через элемент ИЛИ 8 на обнуляющий вход второго счетчика 11. Первый триггер 4 устанавливается в единичное состояние, разрешая прохождение тактовых импульсов от генератора 1 на счетньй вход первого счетчика 9, на первый вход третьего элемента И 7, на первый вход четверг того элемента И 13. Второй триггер 5, подключенньй инверсным выходом ко второму входу второго элемента И 3, позволяет получить стартовые импульсы одинаковой и достаточно малой длительности, независимой от длительности импульса, определяющего начало пакета, а также исключает повторное срабатьтание устройства на время прохождения пакета. .Четвер- тьй 14 и пятый 15 триггеры устанавливаются в нулевое состояние. При этом на обоих входах шестого элемента И 1 7 окажется высокий потенциал, а на одном из входов пятого элемента И 16 - низкий. На вькоде шестого элемента И 17 установится единичное состояние, на выходе пятого элемента И 16 - нулевое. Таким образом, первое запоминающее устройство 18 окажется в режиме записи, а второе запоминающее устройство ,19 - в режиме считывания. Первый счетчик 9 начинает отсчет адресов ячеек памяти первого 18 и второго 19 запоминающих устройств. Как только код на выходах первого счетчика 9 совпадет с кодом, подаваемым с датчика кода 10, на выходе элемента сравнения кодов 12 появится импульс, который поступит на счетный вход четвертого триггера 14 и на единичный вход третьего триггера 6. Этот импульс с помощью четвертого элемента И 13 будет привязан к соответствующему тактово24997Л

му импульсу. Третий триггер 6 ус та- новится в единичное состояние, разрешая прохождение тактовых импульсов на счетный вход второго счетчика 11. 5 Второй счетчик 11, рассчитанный на длительность одного пакета, начнет .отсчет задержанного пакета.

Четвертьш триггер 14, работающий в счетном режиме, изменит свое нуле}0 вое состояние на единичное. При этом на выходе пятого элемента И 16 появится высокий потенциал, а на выходе шестого элемента И 17 - низкий. Таким образом, режимы работы первого

15 18 и второго 19 запоминающих устройств изменятся на противоположные. Первое запоминающее устройство 18 перейдет в ре;ким считывания, а второе запоминающее устройство 19 - в

20 режим записи. При этом на выходе элемента объединения 20, т.е. на выходе устройства 21, появятся первые импульсы задержанного пакета. Кроме того, импульс с выхода четвер25 того элемента И 13 обнулит первый счетчик 9, который снова начнет отсчет адресов ячеек памяти со следующего тактового импульса. Последую ц1-1е импульсы, поступающие с четвертого

, элемента И 13, будут повторно обнулять первый счетчик 9, а также изменять режимы работы первого 18 и второго 19 запоминающих устройств. Импульс с выхода второго счетчика 11, означающий окончание задержанного пакета, переведет первый 4, второй- 5 и третий 6 триггеры в нулевое состояние, обнулит второй счетчик 11, а пятый триггер 15 переведет в единич- ное состояние. При этом второй элемент И 3 окажется в состоянии ожидания начального импульса следующего пакета, тактовые импульсы перестанут проходить через первый 2 и третий 7 элементы И. Первое 18 и второе 19 запоминакяцие устройства низким потенциалом на выходах пятого 16 и шестого 17 элементов И будут переведены в режим.записи и останутся в этом режиме до прихода следукнцего

пакета. С приходом следующего пакета работа устройства повторится в соответствии с кодом, выставленным датчиком кода 10.

55 Формула изобретения

Устройство для задержки импульсов, содержащее четьфе элемента И,

35

40

45

три триггера, два запоминающих устройства, элемент сравнения кодов,, два счетчика, элемент ИЛИ, и.генератор тактовьпс импульсов, выход кото рого подключен к одному из входов первого элемента И, другой вход которого подключен к выходу первого триггера, а вькод - к счетному входу первого счетчика, выходы которого соединены с адресными входами первого запоминающего устройства, отличающееся тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения перестраиваемой (с заданным дискретом) задержки пакета цифровой информации, в него введены два элемента И, два триггера, датчик кода и элемент объединения, причем первьй вход второго элемента И является первым управляюа(им входом устройства, а его выход соеди- .кен с единичными входами первого и второго триггера, нулевыми входами четвертого и пятого триггера и первым входом -элемента ИЛИ, прямой выход второго триггера соединен с третьим входом четвертого элемента И, а инверсный выход - с вторым входом второго элемента И, выход первого элемента И соединен также с вторым, входом четвертого элемента Икс первым входом третьего элемента И, выход которого соединен со счетным входом второго счетчика, выход которого соединен с нулевыми входами первого, второго и третьего триггера, с единичным входом пятого триггера, а также с вторым входом эле2249976

мента ИЛИ, выход которого соединен с обнуляющим входом второго счетчика, выходы первого счетчика соединены также с адресными входами второ- 5 го запоминающего устройства и с первой группой входов элемента сравнения, вторая группа входов которого соединена с датчиком кода, а выход соединен с первым входом четвертого 10 элемента И, выход которого соединен со счетным входом четвертого триггера, с обнуляющим входом первого счетчика, а также с единичным,входом третьего триггера, прямой выход которо- 15 го соединен с вторым входом третьего элемента И, прямой выход четвертого триггера соединен с первым входом пятого элемента И, а инверсный выход соединен с вторым входом шес- 20 того элемента схемы И, выход которого соединен с управляющим входом Запись-считывание второго запоминающего устройства, инверсный выход пятого триггера соединен с первым 25 входом шестого элемента И и с вторым входом пятого элемента И, выход которого соединен с управляющим входом запись-считьтание первого запоминающего устройства, объединенные ин- 30 формационные входы первого и второго запоминающего устройства являются информационным входом устройства для задержки импульсов, а их выходы соединены с входами элемента объедине- 35 ния, вьгкод которого является выходом устройства, .вход генератора тактовых импульсов является вторым управляющим входом устройства.

Составитель А.Титов Редактор И.Сегляник Техред о.Сопко

Заказ 1964/58 Тираж 816Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб,, д.4/5

.Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4

Корректор М.Демчик

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования последовательностей импульсов | 1989 |

|

SU1653140A1 |

| Устройство для передачи информации | 1989 |

|

SU1700571A1 |

| Устройство контроля и управления реконфигурацией резервированной системы | 1989 |

|

SU1691990A1 |

| Устройство для сортировки информации | 1986 |

|

SU1365075A1 |

| Цифровой имитатор радиотелеграфного канала связи | 1985 |

|

SU1275465A1 |

| Устройство для кодирования сигналов частотных датчиков | 1985 |

|

SU1336246A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ДИСКРЕТНОЙ ИНФОРМАЦИИ | 1990 |

|

RU2022470C1 |

| Измеритель временных параметров случайных импульсных потоков | 1988 |

|

SU1575135A1 |

| Программируемый формирователь сложной функции | 1985 |

|

SU1290497A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1575182A1 |

Изобретение относится к радио- .технике. Может использоваться в качестве устройства переменной задержzu ки, управляемого посредством внешнего датчика тока. Цель изобретения - расширение функциональных возможностей, достигается путем перестраиваемой, с заданной дискретностью, задержки пакета цифровой информации. Устройство содержит генератор 1 тактовых импульсов, логические элементы (ЛЭ) И 2, 3, 7, 13, 16 и 17, «триггеры 4, 5, 6, 14 и 15, ЛЭ ИЛИ 8, счетчики 9 и 11, датчик кода 10, элемент сравнения 12, запоминающие устройства (ЗУ) 18и 19,элемент объединения 20. Элемент 20 предназначен для объединения информационных последовательностей, поступающих с выходов ЗУ 18 и 19. Устройство выполнено на типовых элементах импульсной техники. 1 ил. с (Л 18 го If

| Устройство задержки | 1978 |

|

SU769722A1 |

| Устройство для задержки импульсов | 1979 |

|

SU771861A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-04-15—Публикация

1984-06-12—Подача