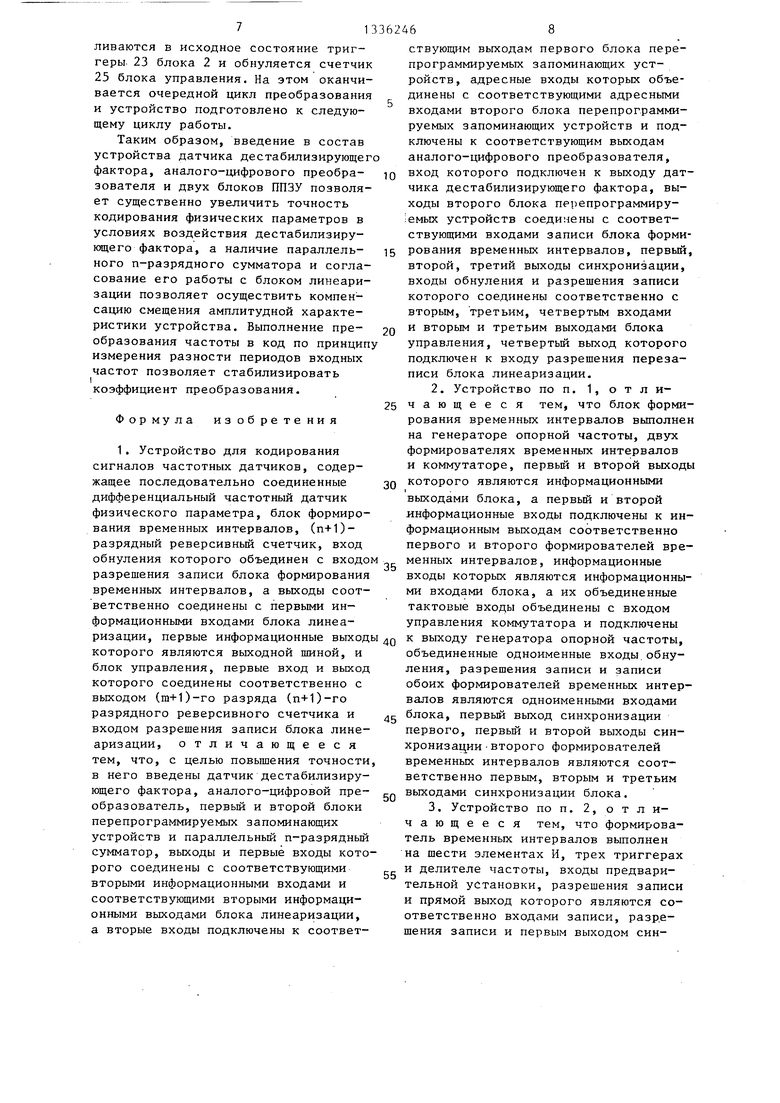

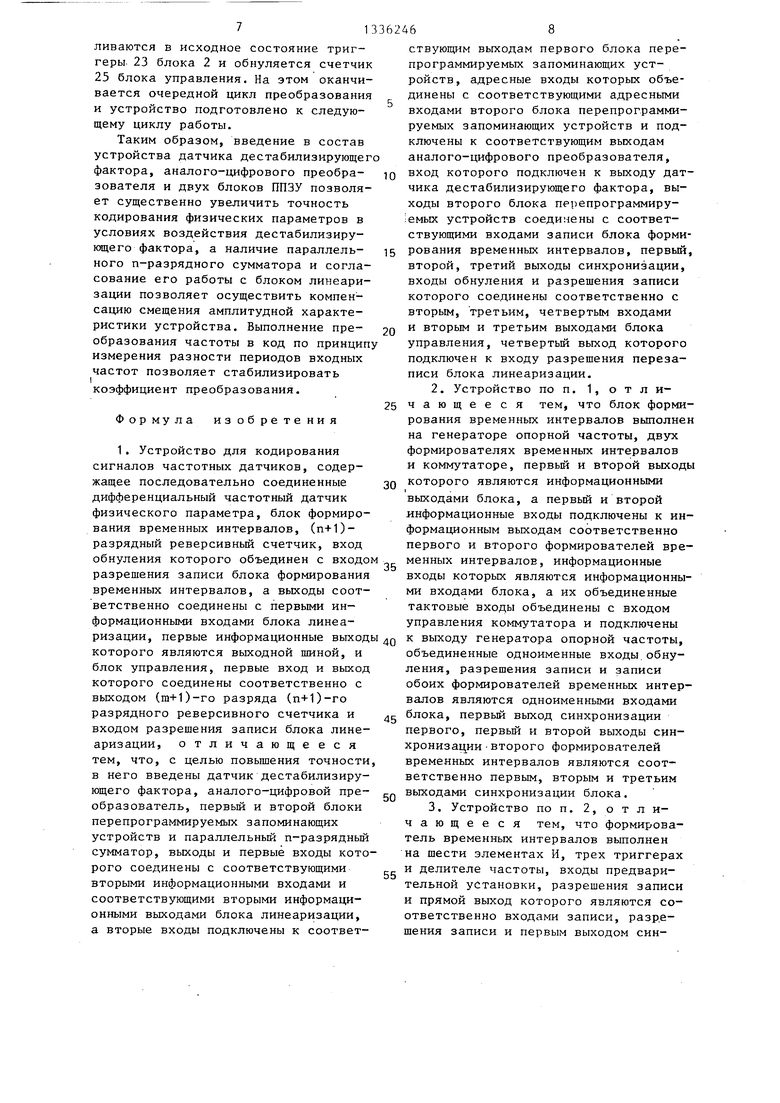

вания временных интервалов, n+1-раэ- рядный реверсивный счетчик 3, блок 4 линеаризации, блок 5 управления, датчик 6 дестабилизирующего фактора, аналого-цифровой преобразователь 7, два блока 8, 9 перепрограммируемьпс запоминающих устройств и параллельный п-разрядный сумматор 10. Блок 2 формирования временных интервалов выполнен на генераторе 11 опорной частоты, двух формирователях 12, 13 временных интервалов и коммутаторе 14, а формирователи 12, 13 включают в себя шесть элементов И 15-20, три триггера 21, 22, 23 и делитель 24 частоты. Блок 5 управления выполнен на счетчике 25, дешифраторе 26, элементе И 27, формирователе 28 импульИзобретение относится к автоматике и измерительной технике и может быть использовано для кодирования непрерывных неэлектрических величин.

Цель изобретения - повышение точности кодирования.

На чертеже представлена функциональная схема устройства.

Устройство содержит дифференциальный частотньй датчик 1 физического параметра, блок 2 формирования временных интервалов (п+1)-разрядный реверсивный счетчик 3, блок 4 линеаризации, блок 5 управления, датчик 6 дестабилизирующего фактора, аналого- цифровой прербразователь 7, два блока 8 и 9 перепрограммируемых запоминающих устройств и параллельный п-разрядный сумматор 10. Блок 2 формирования временных интервалов выполнен на генераторе 11 опорной частоты, двух формирователях 12 и 13 временных интервалов и коммутаторе 14, а формирователи 12 и 13 временных интервалов включают в себя шесть элементов И 15-20, три триггера 21-23 и делитель 24 частоты. Блок 5 управления выполнен на счетчике 25, дешифраторе 26, элементе И 27, формирователе 28 импульсов, элементе ИЛИ 29 и элементе 30 задержки.

сов, элементе ИЛИ 29 и элементе 30 задержки. Введение в состав устройства датчика 6 дестабилизирующего фактора, аналого-цифрового преобразователя 7 и двух блоков 8, 9 перепрог- раммируемых запоминающих устройств позволяет повысить точность кодирования в условиях воздействия дестабилизирующего фактора, а введение параллельного п-разрядного сумматора 10 позволяет осуществить компенсацию дрейфа нуля дифференциального частотного датчика 1 физического параметра. Выполнение преобразования частоты в код по принципу измерения разности периодов входных частот обеспечивает стабилизацию коэффициента преобразования частоты в код. 3 з.п. ф-лы 1 ил

Устройство для кодирования сигналов частотных датчиков работает следующим образом.

В исходном состоянии (п+1)-раз- t, рядный реверсивный счетчик 3, код на выходе которого функционально (в общем случае нелинейно) связан с частотой на выходе датчика 1, обнулен. В блоке 2 формирования временных интер0 валов выполнены начальные установки и .занесено по входам записи число,- хранящееся (по определенному адресу) в блоке 8 перепрограммируемьпс запоминающих устройств (ППЗУ). В блок 4

линеаризации по вторым информационным входам занесено число, равное сумме чисел, хранящихся в блоке 9 ППЗУ и в запоминающем устройстве блока 4 линеаризации. При этом значения

чисел, хранящихся в блоке 8 ППЗУ, равны тарировочным значениям величины изменения коэффициента передачи , тракта физическая величина-код, т.е. величине отклонения крутизны выходной характеристики от номинальной при воздействии дестабилизирующего фактора. Величины чисел, хранящихся в запоминающем устройстве блока 4 линеаризации, равны значениям кодов в

0 узлах интерполяции амплитудной характеристики устройства, и также значе- ниям кодов, задающих угол наклона

5

,

интерполяции, при отсутствии влияния дестабилизирующего фактора. Для этого весь диапазон измерения физического параметра разбивают на участки интерполяции одинаковой величины. Для каждого такого участка определяются и записьгоаются в запоминающее устройство три кода, а именно: коды узловой компенсации, устраняющие нелинейность в начале каждого участка интерполяции с помощью увеличения или уменьшения значений выходных кодов реверсивного счетчика 3 на величину кодов, являющихся постоянными заставками для каждого участка интер поляции; коды коэффициентов интерполяции, численно равные разности между последующим и предыдущим значениями кодов узловой компенсации и уменьшающие нелинейность внутри каждого участка; Лог. О, или Лог. Г - указывающие соответственно на положительное (сложение) или отрицательное (вычитание) направление воздействия кодов коэффициентов интерполяции на коды узловой компенсации внутри одноименных участков. Величины чисел, хранящихся в блоке 9 ППЗУ, равны тарировочным значениям кодов, на которые необходимо сдвигать параллельно самой себе амплитудную характеристику устройства при воздействии дестабилизирующего фактора.

В процессе кодирования сигналов частотного датчика 1 физического параметра блок 2 формирования временных интервалов преобразует приращени физического параметра относительно номинального значения во временной интервал, пропорциональный указанном приращению, который заполняется импульсами опорной частоты. В зависимости от знака приращения физическог параметра импульсы с выхода блока 2 поступают либо на суммирующий, либо вычитающий входы (п+1)-разрядного реверсивного счетчика 3. При этом в п разрядов счетчика 3 записывается значение кода, пропорциональное приращению физического параметра, а в (п+1)-ом разряде записывается информация о знаке приращения. Сформированный таким образом код поступает н первые информационные входы блока 4 линеаризации, в котором осуществляет ся аппроксимация нелинейной амплитудной характеристики устройства в виде линейно-ломаной кривой методом кусочно-линейной интерполяции.

10

15

20

25

40 55 30

35

45

50

При воздействии дестабилизирующего фактора его значение измеряется датчиком 6 и преобразуется в код аналого-цифровым преобразователем 7. Код на выходе преобразователя 7 является адресным для блоков 8 и 9 ППЗУ. В зависимости от величины дестабилизирующего фактора из блоков 8 и 9 соответственно в блок 2 формирования временных интервалов непосредственно и блок 4 линеаризации через сумматор 10 заносятся поправочные коды, компенсирующие влияние дестабилизирующего фактора на амплитудную характеристику устройства.

Блок 2 формирования временных интервалов работает следующим образом.

Частотные сигналы с выходов дифференциального частотного датчика 1 физического параметра поступают на информационные входы блока 2 формирования временных интервалов. При поступлении отрицательных полупериодов сигнала с датчика 1 происходит переключение и удержание триггеров 21 и 22 в нулевом состоянии, а элементов И 15 закрытыми. При положительных полупериодах входного сигнала элементы И 15 открываются, разрешая прохождение импульсов генератора 11 опорной частоты на схемы синхронизации, выполненные на элементах И 16 и 17 и триггерах 21 и 22. Схемы синхронизации осуществляют привязку импульсов входной частоты к импульсам опорной частоты генератора 11. При этом первый импульс генератора 11 через открытые элементы И 15 и 17 поступает на счетный вход триггера 14, переводя его в единичное состояние, открывая тем самым элемент И 16. Второй импульс генератора 11, совпадающий с первьм положительным полупериодом входной измеряемой частоты, переводит триггер 21 в единичное, а триггер 22 в нулевое и через откры- тьй элемент 19 - триггер 23 в единичное состояние. Третий и все последующие импульсы генератора 11 опорной частоты, совпадающие с первым положительным полупериодом входной измеряемой частоты, поглощаются.

При поступлении отрицательного полупериода входной измеряемой частоты с датчика 1 триггеры 21 переключаются и удерживаются, как и триггеры 22, в нулевых состояниях, а эпе- менты 16 закрываются, т.е. схема синхронизации возвращается в исходное

5состояние.. Таким образом, вместо каж доге из входных периодов частотного датчика 1 схема синхронизации формирует импульс, совпадающий с положительным полупериодом измеряемой частоты. При этом момент перехода триггера 23 в- единичное состояние соответствует переднему фронту формируемого временного интервала измерения, которьй поступает на информационные входы коммутатора 14.

Импульсы генератора 11 опорной частоты, совпадающие с вторым, третьим и т.д. положительными полупериодами измеряемой частоты, поступают на тактовьй вход делителей 24 частоты через открытые элементы И 18 первого и второго формирователей 12 и 13 временных интервалов. Поскольку частоты сигналов на первом и втором выходах дифференциального датчика равны только в середине диапазона измерения физического параметра, то и время заполнения делителя 24 частоты в этом случае будет одинаковым только в середине диапазона. В остальных случаях время заполнения делителя 24 част.оты первого и второго формирователей временных интервалов будет различно. В момент заполнения делителя 24 частоты уровнями Лог.О на их инверсных выходах закрываются элементы И 20, фиксируя окончание формирования измерительного интервала, а уровни Лог. 1 на прямых выходах определяют начало импульсов синхронизации, поступающих с выходов формирователей 12 и 13 на второй и третий входы блока 5 управления.. При воздействии дестабилизирующего фактора осуществляется соответствующее изменение емкости делителей 24 частоты, путем предварительного заполнения их по установочным входам кодом компенсации с выхода блока 8 ППЗУ. Информационные сигналы с выходов-формирователей 12 и 13 управляют работой коммутатора 14, обеспечивая, прохождение импульсов генератора 11 опорной частоты на суммирующий или вычитающий входы (п+1) разрядного реверсивного счетчика в зависимости от величины и знака приращения измеряемого физического параметра. После окончания формирования временных интервалов обоими формирователями 12 и 13 через некоторое время, равное четырем периодам частоты генератора

10

36246б

11, с помощью блока 5 управления производятся начальные установки в блоках 12 и 13, при этом в делитель 24 заносится по установочным входам значение корректирующего кода, обнуляется триггер 23, и блок 2 формирования временных интервалов подготовлен к следующему циклу работы. Блок 5 управления предназначен для синхронизации и управления функционированием отдельных блоков и узлов устройства и работает следующим образом.

г В исходном состоянии (в начале очередного цикла преобразования) на вьтходе элемента И 27 уровень сигнала соответствует Лог.О, счетчик 25 обнулен, на первом выходе (мпадший

20 разряд дешифратора 26 уровень Лог. 1, а на остальных выходах - Лог.О. В процессе преобразования по мере заполнения (п+1)-разрядного реверсивного счетчика 3 в момент появления на

25 выходе его (т+1)-.го разряда Лог.1 формирователь 28 импульсов вьфабаты- вает сигнал, которьй через элемент ИЛИ 29 и элемент 30 задержки поступает с первого выхода блока управле30 ния на вход записи блока 4 Линеаризации, осуществляя .занесение нового значения кода узла интерполяции с учетом воздействия дестабилизирукнцего фактора.

После окончания цикла формирования временных интервалов блоком 2 сигналами с его первого и второго выходов синхронизации открывается элемент И 27 блока управления и так40 товые импульсы с третьего выхода синхронизации блока 2 поступают на тактовьй вход счетчика 25, изменяя уровни сигналов на выходе дешифратора 26. После первого тактового им4g пульса задним фронтом сигнала с первого выхода дешифратора 26 осуществляется перезапись-очередного результата преобразования в выходной регистр, блока 4 линеаризации, а импульgQ coM с четвертого выхода дешифратора 26 (второй разряд) осуществляется запись информации в реверсивный счетчик блока 4 линеаризации. Импульсом со второго выхода дешифратора (третий

gc разряд) обнуляется (п+1)-разрядный счетчик 3 и записывается новая информация в делитель 24 частоты блока 2 . Импульсом с третьего выхода дешифратора (старший разряд) устанав35

ливаются в исходное состояние триггеры 23 блока 2 и обнуляется счетчик 25 блока управления. На этом оканчивается очередной цикл преобразования и устройство подготовлено к следующему циклу работы.

Таким образом, введение в состав устройства датчика дестабилизирующег фактора, аналого-цифрового преобра- зователя и двух блоков ППЗУ позволяет существенно увеличить точность кодирования физических параметров в условиях воздействия дестабилизиру- клцего фактора, а наличие параллель- ного п-разрядного сумматора и согласование его работы с блоком линеаризации позволяет осуществить компенсацию смещения амплитудной характеристики устройства. Выполнение пре- образования частоты в код по принцип измерения разности периодов входных частот позволяет стабилизировать коэффициент преобразования.

Формула изобретения

1. Устройство для кодирования сигналов частотных датчиков, содержащее последовательно соединенные дифференциальный частотный датчик физического параметра, блок формирования временных интервалов, (п+1)- разрядный реверсивный счетчик, вход обнуления которого объединен с входо разрешения записи блока формирования временных интервалов, а выходы соответственно соединены с первыми информационными входами блока линеаризации, первые информационные выход которого являются выходной шиной, и блок управления, первые вход и выход которого соединены соответственно с выходом (т+1)-го разряда (п+1)-го разрядного реверсивного счетчика и входом разрешения записи блока линеаризации, отличающееся тем, что, с целью повышения точности в него введены датчик дестабилизирующего фактора, аналого-цифровой пре- образователь, первый и второй блоки перепрограммируемых запоминающих устройств и параллельный п-разрядный сумматор, выходы и первые входы которого соединены с соответствующими вторыми информационными входами и соответствующими вторыми информационными выходами блока линеаризации, а вторые входы подключены к соответ

g

5

5

о д g ,,

5

ствующим выходам первого блока перепрограммируемых запоминающих устройств, адресные входы которых объединены с соответствующими адресными входами второго блока перепрограммируемых запоминающих устройств и подключены к соответствующим выходам аналого-цифрового преобразователя, вход которого подключен к выходу датчика дестабилизирующего фактора, выходы второго блока перепрограммиру- :емых устройств соединены с соответствующими входами записи блока формирования временных интервалов, первый, второй, третий выходы синхронизации, входы обнуления и разрешения записи которого соединены соответственно с вторым, третьим, четвертым входами и вторым и третьим выходами блока управления, четвертый выход которого подключен к входу разрешения перезаписи блока линеаризации,

2.Устройство по п. 1, о т л и- чающееся тем, что блок формирования временных интервалов выполнен на генераторе опорной частоты, двух формирователях временных интервалов

и коммутаторе, первый и второй выходы которого являются информационными выходами блока, а первьй и второй информационные входы подключены к информационным выходам соответственно первого и второго формирователей временных интервалов, информационные входы которых являются информационными входами блока, а их объединенные тактовые входы объединены с входом управления коммутатора и подключены к выходу генератора опорной частоты, объединенные одноименные входы,обнуления, разрешения записи и записи обоих формирователей временных интервалов являются одноименными входами блока, первьй выход синхронизации первого, первьй и второй выходы синхронизации второго формирователей временных интервалов являются соответственно первым, вторым и третьим выходами синхронизации блока.

3.Устройство по п. 2, о т л и- чающееся тем, что формирователь временных интервалов вьшолнен на шести элементах И, трех триггерах и делителе частоты, входы предварительной установки, разрешения записи и прямой выход которого являются соответственно входами записи, разрешения записи и первым выходом син.хронизации формирователя, а тактовый вход и инверсньй выход подключены соответственно к выходу первого и, первому входу второго элементов И, выход последнего из которых объединен с первым входом первого элементг И и является информационным выходом форютрователя, второй вход второго элемента И подключен к прямому выход первого триггера, инверсный выход и тактовый вход которого соединены соответственно с первым входом и выходом третьего элемента И, второй вход которого объединен с вторым вхо дом первого элемента И, тактовым входом второго триггера подключен к выходу четвертого элементов И и является вторым выходом синхронизации формирователя, прямой выход третьего и инверсный выход второго тригге- рой соединены с первыми входами соот ветственно четвертого и пятого элементов И, выход последнего из которых соединен с тактовым входом третьего триггера, второй вход пятого элемента И объединен с вторым входом четвертого элемента И и подключен к выходу шестого элемента И, первый и второй входы которого являются соответственно тактовь1м и информационным входами формирователя, входы обнуле

Редактор С. Патрушева Заказ 4055/56

Составитель Н. Капитанов

Техред И.Попович Корректоре. Шекмар

Тираж 901Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, уп. Проектная, 4

ния второго и третьего триггеров объединены и подключены к второму входу шестого элемента И, а вход обнуления первого триггера является

одноименным входом формирователя.

4. Устройство по п. 1, отличающееся тем, что блок управления выполнен на счетчике, дешифраторе, формирователе импульсов, элементе задержки, элементе ИЛИ и элементе И, входы которого являются соответственно вторым, третьим и четверть входами блока, а выход соединен с тактовым входом счетчика, выходы которого соответственно соединены с входами дешифратора, первый, второй и третий выходы которого являются соответственно вторым, третьим и четвертым выходами блока, а четвертый выход дешифратора соединен с первым входом элемента ИЛИ, второй вход и выход которого соединены соответственно с выходом формирователя импульсов и входом элемента задержки, выход которого является первым выходом блока управления, вход формирователя импульсов является первым входом блока, а вход обнуления делителя соединен с третьим выходом дешифратора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой линеаризатор | 1982 |

|

SU1056453A1 |

| Многоканальное устройство для обработки первичной информации | 1984 |

|

SU1234851A1 |

| Синхрогенератор | 1989 |

|

SU1672586A1 |

| Преобразователь частоты в двоичный код | 1981 |

|

SU995319A1 |

| Многокоординатное устройство для управления | 1987 |

|

SU1522155A1 |

| Умножитель частоты | 1989 |

|

SU1649538A1 |

| Преобразователь кода во временной интервал | 1986 |

|

SU1439741A1 |

| Многоканальное устройство для сбора данных | 1983 |

|

SU1095163A1 |

| Устройство для отображения информации на экране цветного видеоконтрольного блока | 1988 |

|

SU1529280A1 |

| Многокоординатное устройство для управления | 1989 |

|

SU1777121A2 |

Изобретение относится к области автоматики и измерительной техники и может быть использовано для кодирования непрерывных неэлектрических величин. Цель изобретения - повьшение точности. Устройство содержит диффе- ,ренциальный частотный датчик 1 физического параметра, блок 2 формиро(Л со 00 ф кэ Ot

| Преобразователь сигнала дифференциального частотного датчика в код | 1980 |

|

SU949813A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Цифровой линеаризатор | 1982 |

|

SU1056453A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-09-07—Публикация

1985-05-11—Подача