блока управления основного устройства задержки, а третий - с выходом счетчика основного устройства задержки, подключенным одновременно к входу регистра, второй вход которого соединен со вторым выходом формирователя тактовых импульсов, иричем выходы блоков управления подключены ко входам счетчнков основного и дополнительного устройств задержки соответственно, третий вход блока управления основного устройства задержки подключен к первому выходу формирователя тактовых импульсов, второй вход блока управления дополнительного устройства задержки соединен с выходом регистра, третий - с выходом счетчика дополнительного устройства задержки 3.

Недостатком этого устройства является техннческая и функциональная сложность, а вместе с этим низкая надежность.

Целью изобретения является сокращение объема аппаратуры при задержке импульсов на время, превышающее период их повторения.

Для достижения указанной цели в устройство задержки, содержащее датчик кода, генератор, подключенный ко входу счетчика, регистр сдвига, введены блок унравления, блок ввода и сумматор, информационные входы которого норазрядно объединены с выходами разрядов регистра и датчика кода, а выход сумматора присоединен к первому входу блока управления и входу датчика кода, второй и третий входы блока управления подключеиы соответственно к выходу генератора и дополнительному выходу регистра, а его выход соединен с вычитающим входом сумматора, вход устройства нараллельно подключен к первым входа. ключей блока ввода, подключенного ко входам регистра, вторые входы которых присоединены соответственно к выходам разрядов счетчика, выходом подключенного к входу синхронизации регистра, а вторая группа выходов датчика кода подключена к соответствующим входам регистра.

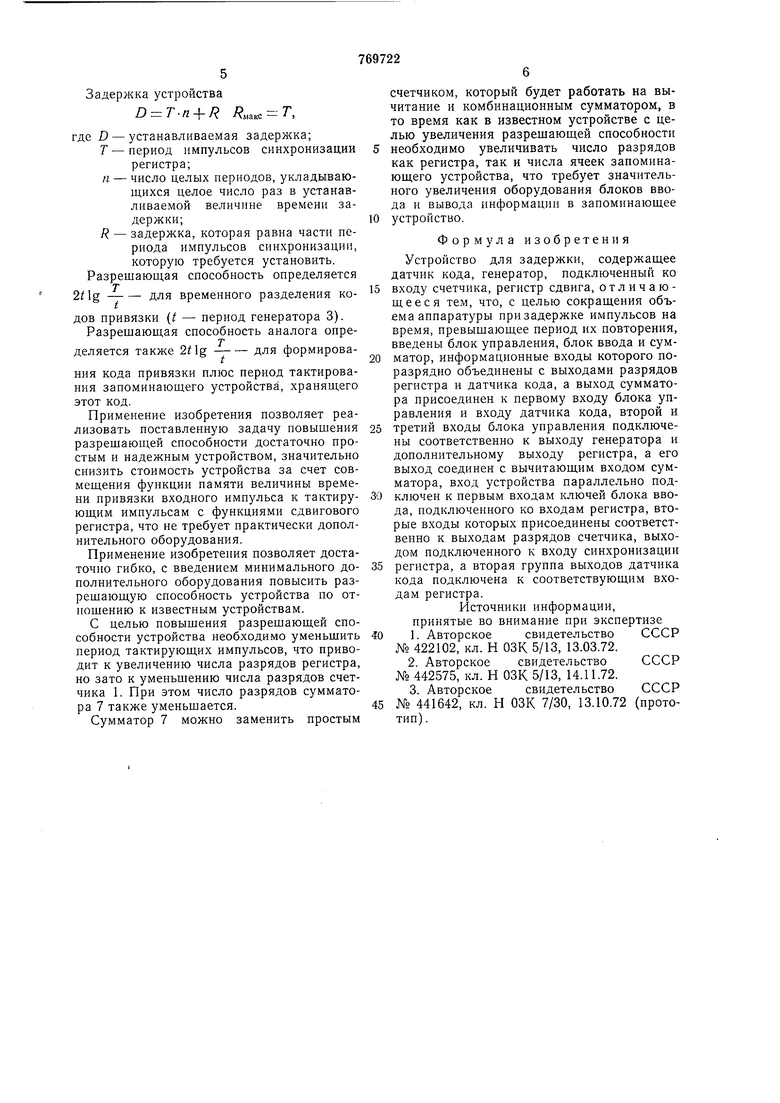

На чертеже представлена функциональная схема предлагаемого устройства.

Устройство задержки содержит счетчик 1, датчик кода 2, генератор 3, регистр 4, блок ввода 5, блок управления 6, сумматор 7, выходную клемму 8, входную клемму 9.

Выходная шина генератора 3 нараллельно соединена со входом счетчика 1 (формирователь тактовых импульсов) и вторым входом блока управления 6. Выходы разрядов счетчика 1 подключены к первым входам ключей блока ввода 5 в регистр 4. Блок ввода 5 состоит из двухвходовых ключей, выходы которых подключены к входам нараллельной записи в регистр 4. Вторые входы ключей блока ввода 5 параллельно подключены к входной клемме 9 устройства. Выход счетчика 1 соединен с входом синхронизации регистра 4. Выходы разрядов

регистра 4 присоединены к входам нараллельной записи в разряды сумматора 7, которые параллельно подключены к выходам датчика кода 2. Выходная клемма 8 сумматора 7 - она же является и выходной клеммой устройства - присоединена параллельно к входу датчика кода 2 и первому входу блока управления 6, выход которого подключен к вычитающему входу сумматора 7.

Третий вход блока управления 6 присоединен к выходу регистра 4.

Устройство работает следующим образом. В исходном состоянии импульсы с выхода генератора 3 поступают на вход счетчика 1 и второй вход блока уиравления 6. Блок управления в исходном состоянии запрещает прохождение импульсов на вычитающий вход сумматора 7, так как отсутствуют импульсы управления с выхода регистра 4 по третьему входу блока управления 6. Тактовые импульсы с выхода счетчика 1 поступают на вход синхронизации регистра 4, но ири отсутствии входного импульса на входной клемме 9 устройства на выходе

регистра 4 импульс будет отсутствовать, а на выходах разрядов регистра 4 будет присутствовать нулевая информация. На выходной клемме устройства имиульсы отсутствуют.

При подаче импульса на клемму 9 входа устройства посредством блока ввода 5 будет переписана в соответствующие разряды регистра 4 информация с разрядов счетчи-, ка 1, соответствующая величине времени

привязки входного импульса к импульсу синхронизации (тактовому) регистра 4. После записи информации в регистр устройство задержки готово к нриходу очередного входного импульса. Записанная в регистр

4 информация носледующими имиульсами синхронизации будет нродвигаться но нему, и при достижении его конца, определяемого установленным значением кода с выходов датчика кода 2, будет сформирован импульс, который перепишет информацию величины времени иривязки входного импульса к импульсам синхронизации регистра 4 с выходов разрядов регистра 4 на входы разрядов сумматора 7, причем предыдущий

импульс с выхода устройства переписал на. входы разрядов сумматора информацию о величине установленной задержки с датчика кода 2. Импульс с выхода регистра 4, также воздействуя по третьему входу блока управления 6, разрешает прохождение импульсов генератора 3 через блок управления 6 на вычитающий вход сумматора 7. В момент обнуления сумматора 7 в нем формируется импульс, который поступает

иа выход устройства, запрещая при этом прохождение импульсов с выхода генератора 3 через блок управления 6 на вычитающий вход сумматора, и переписывает в сумматор 7 значение кода задержки, установленное на выходных щинах датчика кода 2,

Задержка устройства

D T-n + R 7,

где D - устанавливаемая задержка;

Г - период импульсов синхронизации регистра;

п - число целых периодов, укладывающихся целое число раз в устанавливаемой величине времени задержки;

R - задержка, которая равна части периода импульсов синхронизации, которую требуется установить. Разрешающая способность определяется

Т

2t gдля временного разделения кодов привязки (t - период генератора 3). Разрешающая способность аналога опрет

деляется также 2ngдля формирования кода привязки плюс период тактирования запоминающего устройства, хранящего этот код.

Применение изобретения позволяет реализовать поставленную задачу повышения разрешающей способности достаточно простым и надежным устройством, значительно снизить стоимость устройства за счет совмещения функции памяти величины времени привязки входного импульса к тактирующим импульсам с функциями сдвигового регистра, что не требует практически дополнительного оборудования.

Применение изобретения позволяет достаточно гибко, с введением минимального дополнительного оборудования повысить разрешающую способность устройства по отношению к известным устройствам.

С целью повышения разрешающей способности устройства необходимо уменьшить период тактирующих импульсов, что приводит к увеличению числа разрядов регистра, но зато к уменьщению числа разрядов счетчика 1. При этом число разрядов сумматора 7 также уменьщается.

Сумматор 7 можно заменить простым

счетчиком, который будет работать на вычитание и комбинационным сумматором, в то время как в известном устройстве с целью увеличения разрешающей способности необходимо увеличивать число разрядов как регистра, так и числа ячеек запоминающего устройства, что требует значительного увеличения оборудования блоков ввода и вывода информации в запоминающее устройство.

Формула изобретения

Устройство для задержки, содержащее датчик кода, генератор, подключенный ко

входу счетчика, регистр сдвига, отличающееся тем, что, с целью сокращения объема аппаратуры призадержке импульсов на время, превышающее период их повторения, введены блок управления, блок ввода и сумматор, информационные входы которого поразрядно объединены с выходами разрядов регистра и датчика кода, а выход сумматора присоединен к первому входу блока управления и входу датчика кода, второй и

третий входы блока управления подключены соответственно к выходу генератора и дополнительному выходу регистра, а его выход соединен с вычитающим входом сумматора, вход устройства параллельно подключен к первым входам ключей блока ввода, подключенного ко входам регистра, вторые входы которых присоединены соответственно к выходам разрядов счетчика, выходом подключенного к входу синхронизации

регистра, а вторая группа выходов датчика кода подключена к соответствующим входам регистра.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 422102, кл. Н ОЗК 5/13, 13.03.72.

2.Авторское свидетельство СССР № 442575, кл. Н ОЗК 5/13, 14.11.72.

3.Авторское свидетельство СССР № 441642, кл. Н ОЗК 7/30, 13.10.72 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство задержки импульсов | 1980 |

|

SU917326A1 |

| Устройство задержки | 1980 |

|

SU884111A1 |

| Шифратор-дешифратор | 1981 |

|

SU1005295A1 |

| Преобразователь интервалов времени в цифровой код | 1984 |

|

SU1255984A2 |

| Цифровой фазометр-частотомер | 1987 |

|

SU1471148A1 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

| Устройство умножения частоты следования импульсов | 1975 |

|

SU528695A1 |

| Устройство для контроля дальномера системы "запрос-ответ | 1982 |

|

SU1054808A1 |

| Регистратор сигналов с усреднением | 1982 |

|

SU1112230A1 |

| Формирователь импульсов | 1986 |

|

SU1383468A1 |

Авторы

Даты

1980-10-07—Публикация

1978-12-26—Подача