Изобретение относится к радиотех- нике и может найти применение в цифровых системах передачи информации по радио или проводньм каналам связи с использованием сигналов с дискретной частотной манипуляцией.

Целью изобретения является повышение помехоустойчивости.

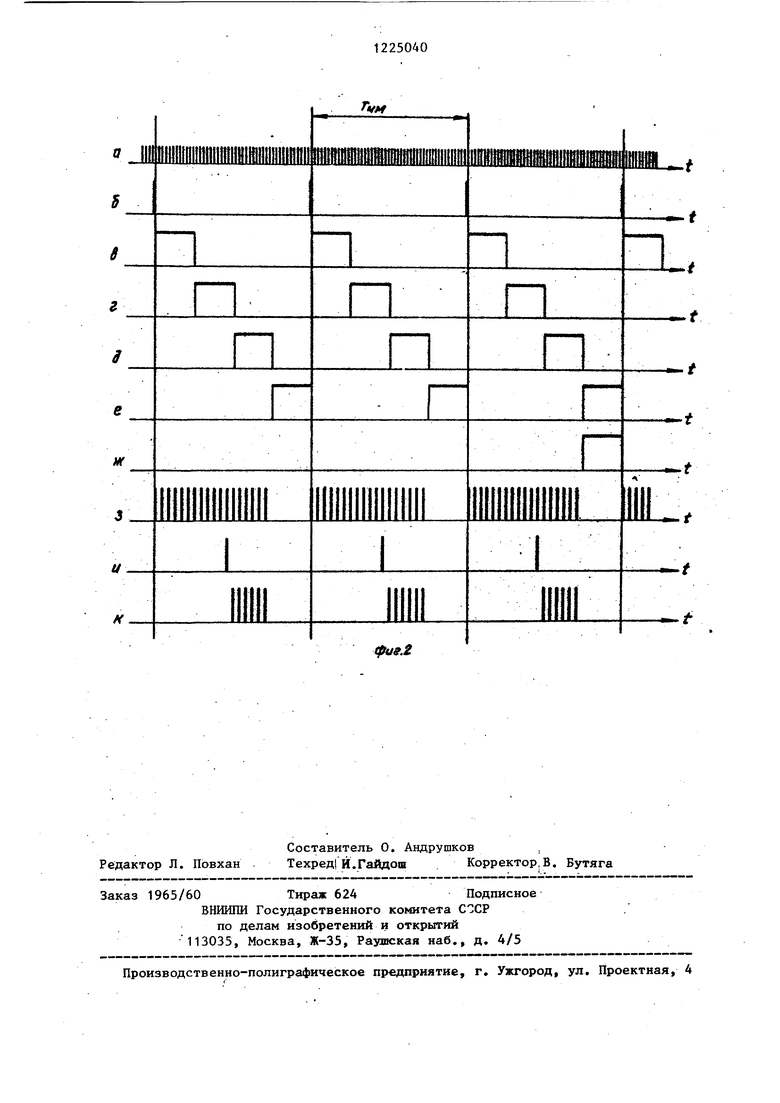

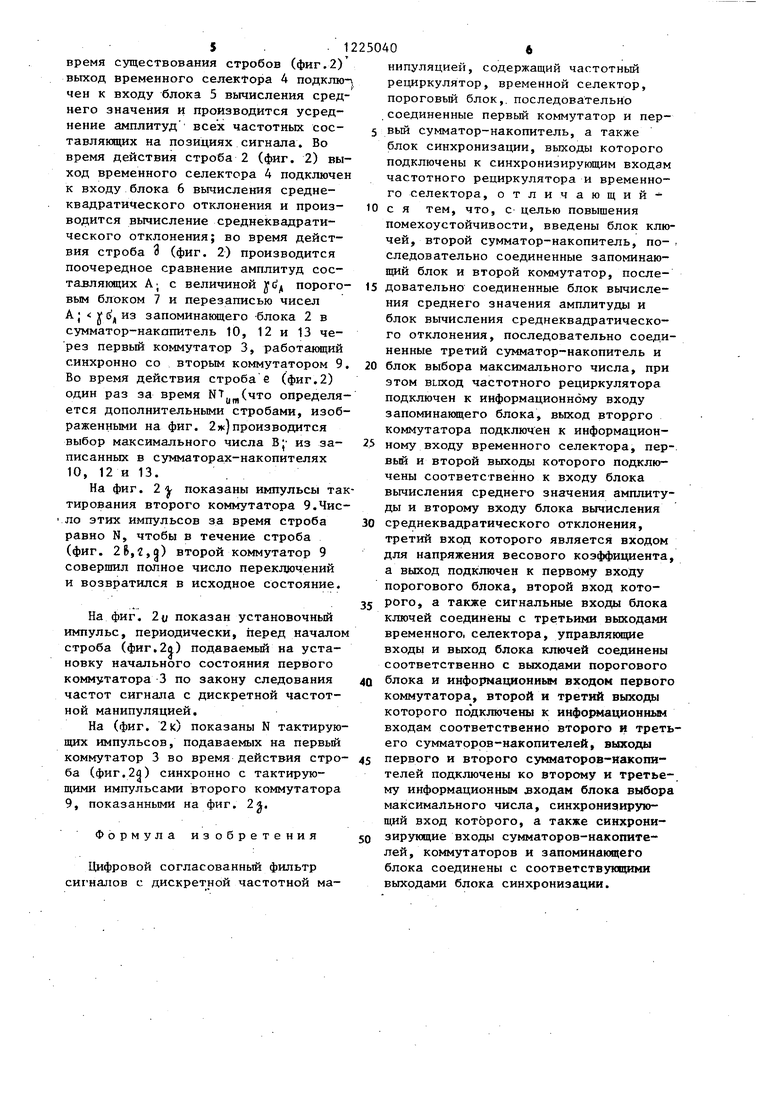

На фиг. 1 изображена структурно- электрическая схема устройства; на фиг. 2 - эпюры напряженийу поясняющие работу устройства.

Цифровой согласованный фильтр сигналов с дискретной частотной манипуляцией содержит частотньй рецир- кулятор 1, запоминающий блок 2,пер- вьй коммутатор 3, временной селектор 4, блок 5 вычисления среднего значения амплитуды, блок 6 вычисления, среднеквадратического отклонения, пороговый блок 7, блок 8 ключей, второй коммутатор 9, перый сумматор-накопитель 10, блок выбора максимального числа 11, второй сумматор-накопитель 12 и третий сумматор-накопитель 13, блок синхронизации 14.

Устройство работает следующим образом.

Сигнал поступает на вход частотного рециркулятора 1, с выхода которого сигнал в цифровой форме подается на вход запоминакицего блока 2. Частотный рециркулятор 1 осуществляет накопление амплитуд гармонических составляющих в полосе анализа с разрешающей способностью, определяемой расстановкой частот в полосе сигнала, а аппа- ра гурно - числом рециркуляции за время Т , равное длительности посыпки сигнала. Оценки амплитуд гармоник после заданного числа циклов выдаются в цифровой форме последовательно, .начиная с первой, в запоминающий блок 2. Вместимость запоминающего блока должна быть такова, чтобы в него могли быть записаны N двоичных чисел установленной разрядности, где каждое число представляет оценку амплитуды частотной составляющей сигнала с дисперсной частотной манипуляцией (N - число анализируемых частотных позиций сигнала, равное числу используемых частот), Двоичные числа А; хранятся в запоминающем блоке 2 в течение времени Т, пока частотным рецикулятором 1 осуществляется новое накопление амплитуд на всех N

щего, блока 2, второй коммутатор 9 вы водит двоичные числа Aj на вход временного селектора 4. Второй коймута- тор 9 -и временный селектор 4 в ра5 боте синхронизированы между собой: временный селектор 4 не изменит свое го состояния до тех пор, пока второй коммутатор 9 не подключит к нему все двоичные слова А; , хранящиеся

О в запоминающем блоке 2.

Первый выход временного селектора

4соединен с входом блока 5 вычисления среднего значения амплитуды, который суммирует поступающие на его

15 вход числа Aj с первого по N-ное. В том случае, когда число N представляет степень числа 2, на выход блока

5вычисления среднего значения ампли туды подаются только старшие разряды

20 накопленного числа с тем, чтобы за счет этого осуществилось деление сум мы чисел на N т 1

25

30

35

50

55

М

N - ,|

Выход блока 5 вычисления среднего значения амплитуды соединен с входом блока 6 вычисления среднеквадратичес кого отклонения, второй- вход которог соединен с вторым выходом временного селектора 4. С переходом временного селектора 4 во второе положение второй коммутатор 9 снова поочередно, начиная с перв ого, подключает выходы запоминающего блока 2 к второму входу блока 6 вычисления среднеквадратического отклонения, который вычисляет результат по формуле

40

М г

HN 5,

(А; - А)

Значение (дд умножается на весовой коэффициент у , выбираемьш опытным путем при настройке в условиях реальной обстановки. Весовой коэф- 45 фициент )С поступает на третий вход блока 6 вычисления среднеквадрати- ческого отклонения в виде калиброванного напряжения.

Выходное напряжение с блока 6 вычисления среднеквадратичрского отклонения в виде двоичного числа поступает на первый вход порогового блока 7, второй вход которого соединен с третьим выходом временного селектора 4. После завершения вычисления числа временньй селектор 4 переключается в третье положение.

частотах. Подключая выходы запоминаю- при этом второй коммутатор 9 подклющего, блока 2, второй коммутатор 9 выводит двоичные числа Aj на вход временного селектора 4. Второй коймута- тор 9 -и временный селектор 4 в работе синхронизированы между собой: временный селектор 4 не изменит своего состояния до тех пор, пока второй коммутатор 9 не подключит к нему все двоичные слова А; , хранящиеся

в запоминающем блоке 2.

Первый выход временного селектора

4соединен с входом блока 5 вычисления среднего значения амплитуды, который суммирует поступающие на его

вход числа Aj с первого по N-ное. В том случае, когда число N представляет степень числа 2, на выход блока

5вычисления среднего значения амплитуды подаются только старшие разряды

накопленного числа с тем, чтобы за счет этого осуществилось деление суммы чисел на N т 1

М

N - ,|

Выход блока 5 вычисления среднего значения амплитуды соединен с входом блока 6 вычисления среднеквадратического отклонения, второй- вход которого соединен с вторым выходом временного селектора 4. С переходом временного селектора 4 во второе положение второй коммутатор 9 снова поочередно, начиная с перв ого, подключает выходы запоминающего блока 2 к второму входу блока 6 вычисления среднеквадратического отклонения, который вычисляет результат по формуле

М г

HN 5,

(А; - А)

Значение (дд умножается на весовой коэффициент у , выбираемьш опытным путем при настройке в условиях реальной обстановки. Весовой коэф- 45 фициент )С поступает на третий вход блока 6 вычисления среднеквадрати- ческого отклонения в виде калиброванного напряжения.

Выходное напряжение с блока 6 вычисления среднеквадратичрского отклонения в виде двоичного числа поступает на первый вход порогового блока 7, второй вход которого соединен с третьим выходом временного селектора 4. После завершения вычисления числа временньй селектор 4 переключается в третье положение.

чает поочередно выходы запоминающего блока 2 к второму входу порогового блока 7 и одновременно к сигнальным выходам блока ключей- 8. В том случае когда А| , разрешающий потен- .циал с выхода порогового блока 7 подается на управляющие входы блока 8 ключей, при этом ключи открываются и число AJ с запоминающего блока 2 проходит на вход первого коммутатора 3, который работает синхронно с вторым коммутатором 9: первое число А- из запоминающего блока 2 заносится в первый сумматор-накопитель 10, второе число А 2 - во второй сумматор- накопитель 12, а третье - в третий сумматор-накопитель 13.

Во втором цикле работы фильтра (длина цикла равна Т) все его эле- енты работают аналогично. Но с каждым новым циклом первый коммутатор 3 изменяет свое начальное состояние таким образом, чтобы к первому по порядку сумматору-накопителю подключался тот выход первого коммутатора 3, порядковый номер которого меняется в соответствии с порядком перебора частот в сигнале. Если, например, частоты следуют во времени в порядке их возрастания, и согласованный фильтр случайно включился так, что за время существования первой частоты накоплённьй сигнал записан первьи в запоминающий блок 2, то во втором цикле накопления полезный сигнал записьюается в запоминакяций блок 2 вторым как число А,, и так далее - с кажлым циклом он заносится в соответствующие ячейки запоминающего блока 2. Через N циклов по лезный сигнал снова записывается в запоминакщий блок 2 как число А j. Первый коммутатор 3 должен с каждым циклом изменять свое начальное состояние: при начале работы его первый выход бьш соединен с первым сумматором - накопителем 10, куда и запишется число А, первого цикла. При втором цикле нужно установить начальное состояние первого коммутатора 3 так, чтобы его второй вход бьш соединен с входом первого сумматора-накопителя 10, при этом полезньй сигнал,записанный как Аг в запоминающий блок 2, на втором щаге первого коммутатора 3 за- письшается тоже в первый сумматор- накопитель 10, куда на первом цикле было записано первое число AI. Далее

с каждым новым циклом накопления.полезный сигнал, записанный числом А; в запоминающий блок 2, накапливается на i-oM шаге коммутаторов в том же 5 первом сумматоре-накопителе 10. В реальных случаях, когда порядок следования частот произволен и когда устройство включилось в произвольный момент времени относительно на- 0 чала перебора частот сигнала, накопление сигнала при данном способе управления первым коммутатором 3 происходит в одном, хотя и произвольном сумматоре-накопителе 10, 12 и 13. Та 5 КИМ образом, после N шагов накопления в одном из сумматоров-накопителей 10,- 12 и 13 накоплено число В: пропорциональное амплитуде составляющих сигнала,и числа с выходов всех сумматоров- 0 -накопителей 10,12 и 13 сравниваются между собой в блоке выбора максимального числа 11. Выбранное число В/ подается как вьЬсодной сигнал на пороговое / устройство обнаружителя. 5 Временные соотношения между различными импульсными последовательностями блока синхронизации 14, определяющими работу устройства, приведены на фиг.2.Тонкие вертикальные линии 0 обозначак1Т интервалы времени, равные длительности Т одной частоты посылки сигнала.

На фиг. 2акаяф(ый из отрезков делится на более мелкие временные интервалы СрцПо числу рециркуляции частотного рециркулятора 1 за время Т,. Число рециркуляции зависит от требуемой разр ающей способности рециркулятора и может достигать нескольких тысяч.

В течение последнего отрезка Z

РЧ

э каждом интервале вырабатьшает- ;я строб перезаписи содержимого ч. готного рециркулятора 1 в запс..юнаю- щий блок 2. При перезаписи двоичные числа счетными импульсами переносятс в отведенные участки запоминакицего блока 2. Строб перезаписи показан на фиг. 2. Число импульсов считьшания 0 за время строба зависит от числа N, разрядности чисел и способа перезаписи - последовательного или параллельного.

На фиг. 28,2,J,e показаны стробы, 55 управляющие работой временного селектора 4, первого 3 и второго 9 коммутаторов. Этими стробами интервал Т дцделится на четыре части. Во

время существования стробов (фиг.2) выход временного селектора 4 подклю

чен к входу блока 5 вычисления среднего значения и производится усреднение амплитуд всех частотных составляющих на позициях сигнала. Во время действия строба 2 (фиг. 2) выход временного селектора 4 подключен к входу блока 6 вычисления средне- квадратического отклонения и производится вычисление среднеКвадрати- ческого отклонения; во время действия строба 3 (фиг. 2) производится поочередное сравнение амплитуд составляющих А; с величиной ytf пороговым блоком 7 и перезаписью чисел А; У(д из запоминающего -блока 2 в сумматор-някапитель 10, 12 и 13 че- рез первый коммутатор 3, работакнций синхронно со вторым коммутатором 9. Во время действия строба е (фиг.2) один раз за время NT|(4TO определяется дополнительными стробами, изображенными на фиг. 2ж)производится выбор максимального числа В| из записанных в сумматорах-накопителях 10, 12 и 13.

На фиг. 2 показаны импульсы тактирования второго коммутатора 9.Число этих импульсов за время строба равно N, чтобы в течение строба (фиг. 2&,г,д) второй коммутатор 9 совершил полное число переключений и возвратился в исходное состояние.

На фиг. 2о показан установочньш импульс, периодически, перед началом строба (фиг.2а) подаваемый на установку начального состояния первого коммутатора 3 по закону следования частот сигнала с дискретной частотной манипуляцией.

На (фиг. 2 к) показаны N тактирующих импульсов, подаваемых на первьй коммутатор 3 во время действия строба (фиг.2а) синхронно с тактирующими импульсами второго коммутатора 9, показанными на фиг. 2.

Формула изобретения

Цифровой согласованный фильтр сигналов с дискретной частотной манипуляцией, содержащий частотный рециркулятор, временной селектор, пороговый блок,, последовательно соединенные первый коммутатор и пер- 5 вый сумматор-накопитель, а также блок синхронизации, выходы которого подключены к синхронизирующим входам частотного рециркулятора и временного селектора, отличающий0 с я тем, что, с целью повышения

помехоустойчивости, введены блок ключей, второй сумматор-накопитель, последовательно соединенные запоминающий блок и второй коммутатор, после5 довательно соединенные блок вычисления среднего значения амплитуды и блок вычисления среднеквадратическо- го отклонения, последовательно соединенные третий сумматор-накопитель и

0 блок выбора максимального числа, при этом вькод частотного рециркулятора подключен к информационному входу запоминающего блока, выход вторрго коммутатора подключен к информацион5 ному входу временного селектора, пер-, вьй и второй выходы которого подключены соответственно к входу блока вычисления среднего значения амплитуды и второму входу блока вычисления

0 среднеквадратического отклонения, третий вход которого является входом для напряжения весового коэффициента, а выход подключен к первому входу порогового блока, второй вход кото5 рого, а также сигнальные входы блока ключей соединены с тре тьими выходами временного селектора, управляющие входы и выход блока ключей соединены соответственно с выходами порогового

0 блока и информациониьм входом первого коммутатора, второй и третий выходы которого подключены к инфо1Я4ационньш входам соответственно второго и третьего сумматоров-накопителей, выходы

5 первого и второго сумматоров-Накопителей подключены ко вторсжу и третьему информационным входам блока выбора максимального числа, синхронизирующий вход которого, а также синхрони0 зирутощие входы сумматоров-накопителей, коммутаторов и запоминающего блока соединены с соответствующими выходами блока синхронизации.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1992 |

|

RU2114514C1 |

| Цифровой согласованный фильтр сигналов с дискретной частотной манипуляцией | 1986 |

|

SU1438017A1 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1990 |

|

RU2022485C1 |

| МОДАЛЬНЫЙ ДАЛЬНОМЕР ИМПУЛЬСНО-ДОПЛЕРОВСКОЙ РАДИОЛОКАЦИОННОЙ СТАНЦИИ | 2004 |

|

RU2277714C1 |

| Цифровой согласованный фильтр | 1988 |

|

SU1653174A1 |

| Согласованный фильтр сигналов с дискретной частотной манипуляцией | 1982 |

|

SU1092751A1 |

| СПОСОБ ПЕЛЕНГАЦИИ ГИДРОБИОНТОВ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1996 |

|

RU2093856C1 |

| УСТРОЙСТВО СТАБИЛИЗАЦИИ УРОВНЯ ЛОЖНЫХ ТРЕВОГ ПОМЕХОЗАЩИЩЕННОГО РАДИОЛОКАЦИОННОГО ПРИЕМНИКА, РАСПОЛОЖЕННОГО НА ВОЗДУШНЫХ НОСИТЕЛЯХ | 1990 |

|

SU1840162A1 |

| СПОСОБ И УСТРОЙСТВО ВИБРОДИАГНОСТИКИ РОТОРНЫХ МЕХАНИЗМОВ | 1999 |

|

RU2153660C1 |

| Устройство выделения периодических импульсных последовательностей | 1980 |

|

SU938231A1 |

Изобретение относится к радиотехнике. Повышается помехоустойчивость. Устройство содержит частотный рециркулятор 1, запоминающий блок 2, два коммутатора 3 и 9, временной се- лект.ор 4, блок в ьгчисления среднего значения амплитуды (БВСЗА) 5, блок выполнения среднеквадратического отклонения (БВСО) 6, пороговый блок 7, блок ключей- 8, три сумматора-накопителя 10, 12 и 13, блок выбора максимального числа (БВМЧ) 11. и блок синхронизации 14. Сигнал с выхода частотного рециркулятора 1 в цифровой форме подается на вход запоминающего блока 2, из которого коммутатор 9 вьшодит на- вход временного селектора 4 двоичные числа А.- . Числа А суммируются в БВСЗА 5, вычисляются в БВСО бив виде двоичного числа поступают на вход порогового блока 7. Его разрешающий потенциал подается на управлякицие входы блока ключей 8, которые открываются, и через коммутатор 3 число А (А|, А, А) из запоминающего блока 2 заносится в сумматоры-накопители 10, 12 и 13. Числа с выходов всех сумматоров-накопителей 10, 12 и 13 сравниваются, между собой в БВМЧ 11 и выбранное им число В- является выходным сигналом. 2 ил.

/г

ж

Редактор Л. Повхан Заказ 1965/60

Составитель О. Андрушков ,

Техред И.Гайдош Корректоров. Бутяга

Тираж 624Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| Кук И и др | |||

| Радиолокационные сигналы | |||

| М.: Советское радио, 1971, с | |||

| Телефонно-осведомительный аппарат | 1921 |

|

SU306A1 |

| Согласованный фильтр сигналов с дискретной частотной манипуляцией | 1982 |

|

SU1092751A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1986-04-15—Публикация

1984-10-12—Подача