О5

ел

оэ

Изобретение относится к радиотехнике и может быть использовано в об- наружительпых цифровых сигналах с дискретной частотной манипуляцией (ДЧМ).

Цель изобретения - повышение быстродействия.

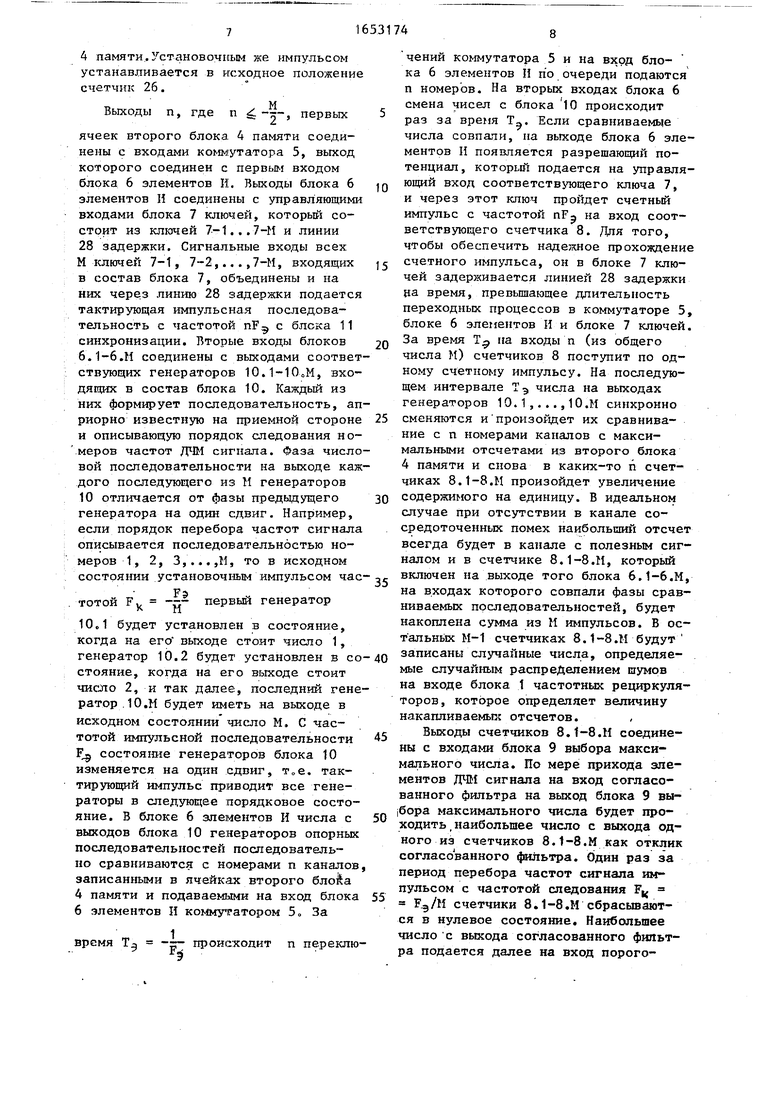

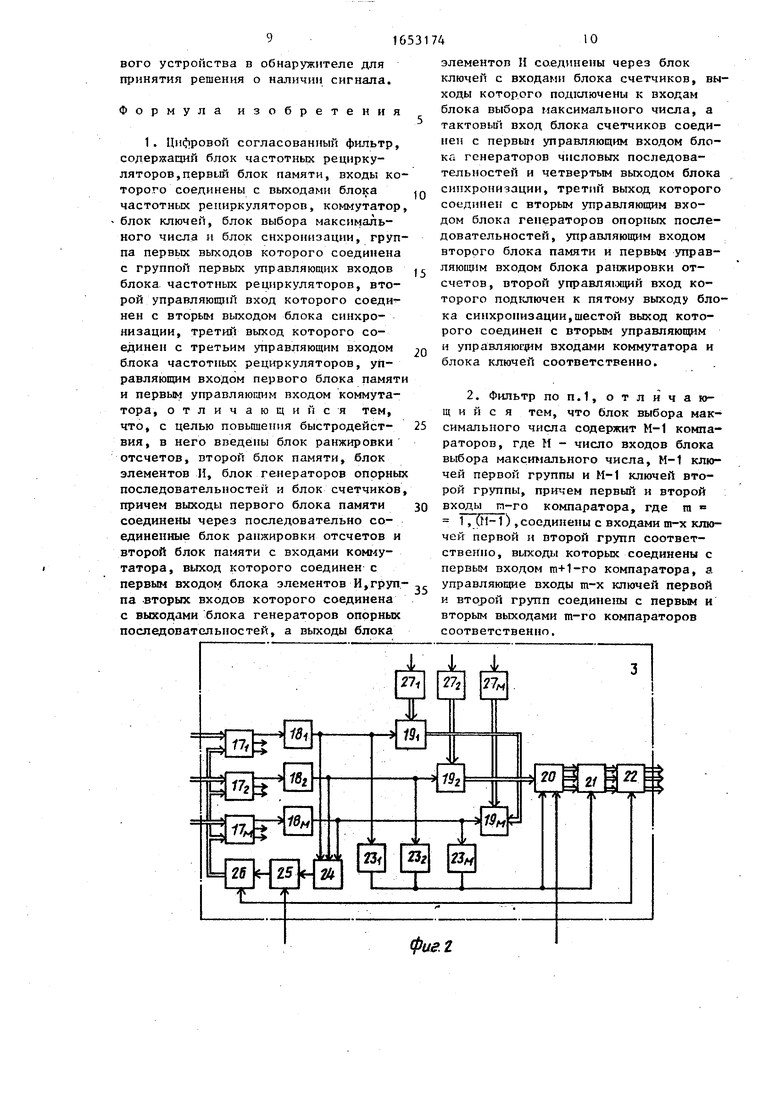

На фиг.1 приведена электрическая структурная схема цифрового согласо- ванного фильтра; на фиг.2-4 - электрические структурные схемы блока ранжирования отсчетов, блоков элементов И, ключей и генераторов опорных последовательностей и блока вы- бора максимального числа.

Цифровой согласованный фильтр содержит блок 1 частотных peциpкvлятo- ров, первый бпок 2 памяти, блок 3 ранжировки отсчетов, второй блок 4 памяти, коммутатор 5, блок 6 элементов И, блок 7 ключей, блок 8 счетчиков, счетчик 8.1-8.М, блок 9 выбора максимального числа, блок 10 генераторов опорных последователь- ностей, блок 11 синхронизации, генератор 12, делители 13-15 частоты и частотные рециркуляторы 16.1-16.М.

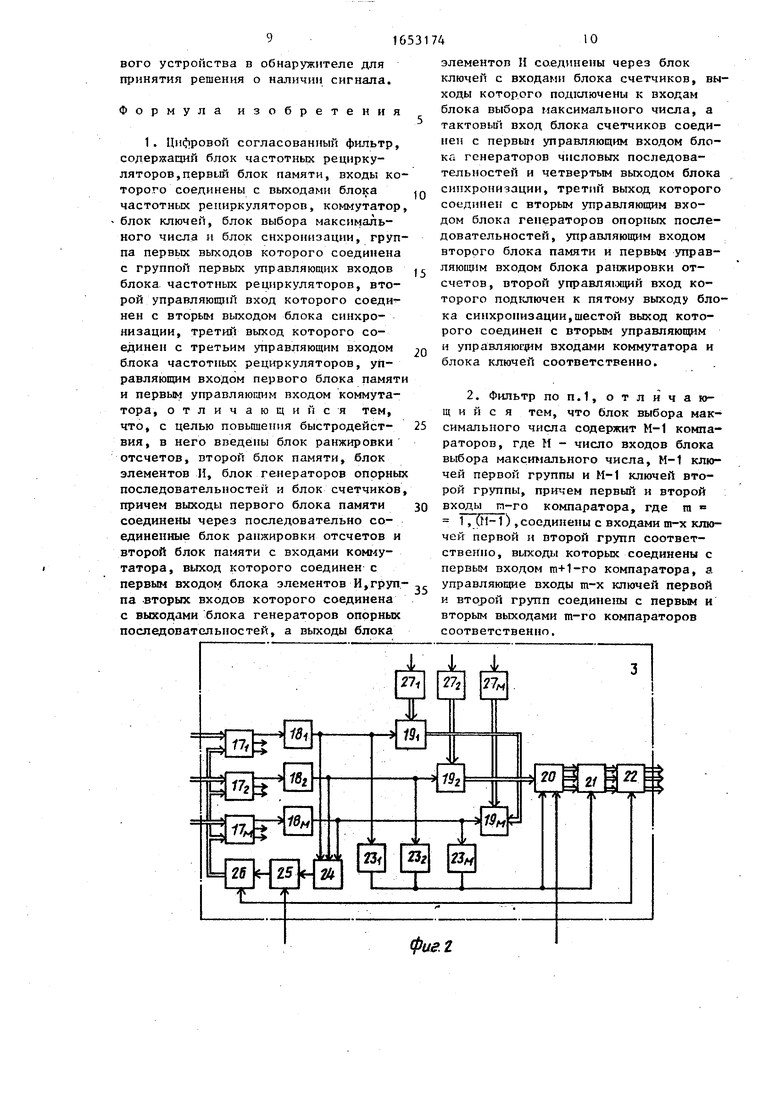

Блок 3 ранжировки отсчетов содержит компараторы ,М, одновиб- раторы 18.1-18.М, канальные ключи 19.1-19.М, коммутатор 20, блок 21 памяти, блок 22 ключей, формирователи 23.1-23.М импульсов, элемент ИЛИ-НЕ 24, ключ 25, счетчик 26, регистры 27.1-27«М.

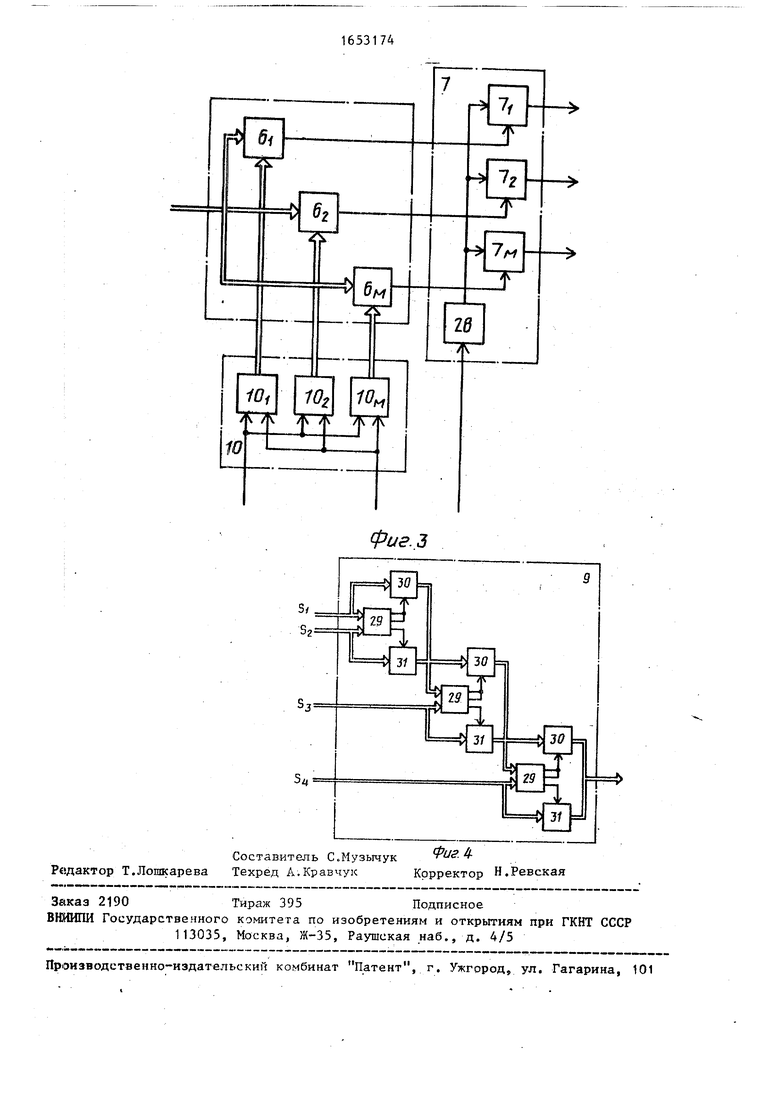

Блок 6 элементов И содержит блоки 6.1-6.М совпадения.

Блок 7 ключей содержит ключи 7„1- 7„М и линию 28 задержки.

Блок 10 содержит генераторы опорных последовательностей 10„1 -10„М.

Блок 9 выбора максимального числа содержит компараторы 29, ключи 30 певой группы и ключи 31 второй группы.

Цифровой согласованный фильтр работает следующим образом.

Входной сигнал в виде аддитивной смеси сигнала, шумов и импульсных и узкополосных помех посту- пает на вход блока 1 частотных ре- циркуляторов. ДЧМ сигнал представляет собой последовательность радиоимпульсов, передаваемых на скачкообразно меняющихся, отличных одна от другой частотах 00С- гДе i ,... М. Блок 1 состоит из одинаковых частотных рециркуляторов 16.1, являющихся накопителями амплитуды. Входы

всех накопнтелей-рециркулятсров объединены и являются входом согласованного фильтра, На опорный вход каждого из частотных рецнркуляторов 16.1 с блока 11 синхронизации подается опорное гетеродинное напряжение С00;, на все частотные рециркуляторы 16.1 подается также импульсная последовательность с частотой дискретизации F и импульсная последовательность с частотой следования элементов ДЧМ сигнала F, импульсы которой определяют моменты выдачи накопленных отсчетов входного сигнала. Каждый из блоков 16.1 выполняет функцию узкополосного фильтра, настроенного на одну из частот сигнала СО;;, обладающего

полосой пропускания Д F -- F,

Ј П

с выхода которого с частотой F- снимаются в цифровом виде отсчеты, пропорциональные мощности входного сигнала в полосе пропускания узкополосного фильтра„ На выходе М рециркуля- торов-накопителей в каждый момент считывания будет М отсчетов, которые запишутся кагсдый в свою ячейку первого блока 2 памяти. Затем в течение

времени Т

1

накопители-рециро

Q

5

5

куляторы 16.1 будут снова накапливать очередные отсчеты входного сигнала, а отсчеты с выхода первого блока 2 памяти подаются на входы блока 3 ранжировки отсчетов.

Блок 3 ранжировки отсчетов состоит из М компараторов 17 двоичных чисел, с каждым из которых последовательно пключены одновибратор 18 и канальный ключ 19. Выходы всех М канальных ключей 19 объединены и соединены с входом коммутатора 20, последовательно с которым включен блок 21 памяти и блок 22 ключей, выходы которых являются выходом блока 3 ранжировки отсчетов. Кроме того, выход каждого из одновибраторов 18 соединен с входом формирователя 23 импульсов и с одним из М входов элемента ИЛИ-НЕ 24 о Объединенные выходы формирователей 23 импульсов соединены с тактирующим входом коммутатора 20, а выход элемента ИЛИ-НЕ 24 через ключ 25 соединен с вычитающим входом счетчика 26, выходы разрядов которого соединены с вторыми входами компара51653174

торов 17, при этом на установочные входы коммутатора 20, счетчика 26 и управляющие входы блока 22 ключа подается импульсная последовательность

1 25 н

с частотой F, а сигнальные пходы канапьных ключей соединены с выходами регистров 27.

В момент снятия с выходов блока 1 частотньгх рециркуляторов на установочные входы г Ммутатора 20 и счетчика 26 подается импульс, который устанавливает коммутатор и счетчик в исходное состояние, а именно коммутатор 20 в положение, когда его вход соединяется с его первым выходом, а счетчик 26 устанавливается в состояние, соответствующее внесению в него какого-тс исходно о числа NC(, . При этом на первые входи компараторов 17 подаются двоичные числа N1, предегаьляющие отсчеты г ячеек первого блока 2 памяти, а на вторые входы компараторов 17 одновременно с выходов счетчика 26 подается двоичное число N

сч

заведомо большее самого большего из отсчетов входного сигнала (ам При этом на выходах компараторов 17 установятся соответствующие потенциалы, определяемые соотношением N ; L М; vcv,с d N fy Через нормально замкнутый ключ 23 ла вычитающий вход счетчика 26 поступают импульсы последовательности

Г..

э

N,

1 - к хэ

где Iое

тельность импульса одновибратора 18, при этом содержимое счетчика 2b начинает уменьшаться на единицу с поступлением каждого импульса FC4. В момен-

раторе 17 произойдет повышение от счета входного сигнала (числа HI пер вом входе), что приведет к формированию скачка потенциала на выходе этогг компаратора. Далее все будет развиваться аналогично описанному выше и во вторую ячейку блока 21 памяти будет записан номер канала, в 45 котором рециркулятор блока 1 накопил второй по величине отсчет. После завершения цикла работы в ячейки блока 21 памяти с первой по М-ю будут по порядку записаны номера каналов пс стеты времени, когда на одном из компараторов число на первом (сигнальном) входе превысит текущее значение числа NC4 на выходе счетчика 26, произойдет скачкообразное изменени потенциала на выходе данного компаратора 17. Скачок потенциала запустит одновибратор 18 данного канала, кото- 50 пени убывания уровня накопленных от- рый сформирует кратковременный строб, счетов входного сигнала, то есть бу- подаваемый на вход управления канального ключа 19, на вход формирователя импульсов и на один из выходов элемента ИЛИ-НЕ 24. На время действия 55 строба откроется нормально разомкнутый канальный ключ 19 и пропустит содержимое регистра 27 данного канала на вход коммутатора 20. Содержимым

дет произведена их ранжировка и произведена замена отсчетов на номера каналов, в которых сформированы эти отсчеты. С приходом установочного импульса откроются ключи блока 22 и содержимое блока 21 памяти будет подано на вход блока 3 ранжировки отсчетов и записано во втором блоке

регистра 27 является постоянно записанное число - номер данного канала, Таким образом, на первый выход коммутатора 20 пройдет двоичное число i 1 , 2,. . .,М, означающее номер канала, в котором накопитель 16 накопил наибольпий отсчет. Это число запишется и первой ячейке блока 21 памяти. Срезом импульса одновибратора 18 в формирователе 23 импульса сформируется тактовий импульс, который переведет коммутатор 20 во второе положение. Для того, чтобы в момент формирования ш рвого импульса одно- нибрагора 10 не происходило уменьшение содержимого Мсч счетчика 26, импульс одногшбратора через элемент 1ШИ-НГ, 24, подаваемый на управляющий вход кпюча 25, размыкает его, при этом прекращается доступ считывающих импульсов на вход счетчика 26. Этим предотвращается возможность одновре- вромснного открывания двух каналь- 5 ньгх ключей 19 и подключение выходов одновременно двух регистров 27 к входу коммутатора 20. Через время,равное длительности формируемого импульса, / одновибплтор 18 данного канала возвращается в исходное состояние, и его заставит сработать только скачок потенциала в следующем периоде анализ.- отсчетов (через орпмя, равное

5

0

O

35

VПо мере уменьшения содержимого NC счетчика 26 уже в другом компа

40

раторе 17 произойдет повышение от счета входного сигнала (числа HI первом входе), что приведет к формированию скачка потенциала на выходе этогг компаратора. Далее все будет развиваться аналогично описанному выше и во вторую ячейку блока 21 памяти будет записан номер канала, в 45 котором рециркулятор блока 1 накопил второй по величине отсчет. После завершения цикла работы в ячейки блока 21 памяти с первой по М-ю будут по порядку записаны номера каналов пс сте50 пени убывания уровня накопленных от- счетов входного сигнала, то есть бу- 55

пени убывания уровня накопленных от- счетов входного сигнала, то есть бу-

дет произведена их ранжировка и произведена замена отсчетов на номера каналов, в которых сформированы эти отсчеты. С приходом установочного импульса откроются ключи блока 22 и содержимое блока 21 памяти будет подано на вход блока 3 ранжировки отсчетов и записано во втором блоке

4 памяти.Установочным же импульсом устанавливается в исходное положение счетчик 26.

М Выходы п, где п Ј-ъ первых

ячеек второго блока 4 памяти соединены с входами коммутатора 5, выход которого соединен с первым входом блока 6 элементов И. Выходы блока 6 элементов Н соединены с управляющими входами блока 7 ключей, который состоит из ключей 7-1...7-М и линии 28 задержки. Сигнальные входы всех М ключей 7-1, 7-2,...,7-М, входящих в состав блока 7, объединены и на них через линию 28 задержки подается тактирующая импульсная последовательность с частотой nF с блока 11 синхронизации. Вторые входы блоков 6.1-6.М соединены с выходами соответствующих генераторов 10.1-10„М, входящих в состав блока 10. Каждый из них формирует последовательность, априорно известную на приемной стороне и описывающую порядок следования номеров частот ДЧМ сигнала. Фаза числовой последовательности на выходе каждого последующего из М генераторов 10 отличается от фазы предыдущего генератора на один сдвиг. Например, если порядок перебора частот сигнала описывается последовательностью номеров 1, 2, 3,...,М, то в исходном состоянии установочным импульсом частотой FK - первый генератор

10.1 будет установлен в состояние, когда на его выходе стоит число 1, генератор 10.2 будет установлен в со стояние, когда на его выходе стоит число 2, и так далее, последний генератор 10.М будет иметь на выходе в

исходном состоянии число М. С частотой импульсной последовательности F состояние генераторов блока 10 изменяется на один сдвиг, т„е. тактирующий импульс приводит все генераторы в следующее порядковое состояние. В блоке 6 элементов И числа с выходов блока 10 генераторов опорных последовательностей последовательно сравниваются с номерами п каналов записанными в ячейках второго блока 4 памяти и подаваемыми на вход блока 6 элементов И коммутатором 5 За

1 время Tj -- происходит п переклюF9

чений коммутатора 5 и на вход блока 6 элементов И по очереди подаются п номеров. На вторых входах блока 6 смена чисел с бпока 10 происходит раз за время Т. Если сравниваемые числа совпали, на выходе блока 6 элементов И появляется разрешающий потенциал, который подается на управляющий вход соответствующего ключа 7, и через этот ключ пройдет счетный импульс с частотой nF на вход соответствующего счетчика 8. Для того, чтобы обеспечить надежное прохождение счетного импульса, он в блоке 7 ключей задерживается линией 28 задержки на время, превышающее длительность переходных процессов в коммутаторе 5, блоке 6 элементов И и блоке 7 ключей. За время Т на входы п (из общего числа М) счетчиков 8 поступит по одному счетному импульсу. На последующем интервале Т э числа на выходах генераторов 10.1,...,10.М синхронно сменяются и произойдет их сравнивание с п номерами каналов с максимальными отсчетами из второго блока 4 памяти и снова в каких-то п счетчиках 8.1-8.И произойдет увеличение содержимого на единицу. В идеальном случае при отсутствии в канале сосредоточенных помех наибольоий отсчет всегда будет в канале с полезным сигналом и в счетчике 8.1-8.М, который включен на выходе того блока 6.1-6.М, на входах которого совпали фазы сравниваемых последовательностей, будет накоплена сумма из П импульсов. В остальных М-1 счетчиках 8.1-8.М будут записаны случайные числа, определяемые случайным распределением шумов на входе блока 1 частотных рециркуля- торов, которое определяет величину накапливаемых отсчетов.

Выходы счетчиков 8.1-8.М соединены с входами блока 9 выбора максимального числа. По мере прихода элементов ДЧМ сигнала на вход согласованного фильтра на выход блока 9 выбора максимального числа будет проходить ,наибольшее число с выхода одного из счетчиков 8.1-8.М как отклик согласованного фильтра. Один раз за период перебора частот сигнала импульсом с частотой следования F счетчики 8.1-8.М сбрасываются в нулевое состояние. Наибольшее число с выхода согласованного фильтра подается далее на вход порого

вого устройства в обнаружителе для принятия решения о наличии сигнала.

Формула изобретения

1. Цифровой согласованный фильтр, содержащий блок частотных рецирку- ляторов,первый блок памяти, входы которого соединены с выходами блока частотных рецнркулятороп, коммутатор блок ключей, блок выбора максимального числа и блок снхронизации, группа первых выходов которого соединена с группой первых управляющих входов блока частотных рециркуляторов, второй управляющий вход которого соединен с вторым выходом блока синхронизации, третий выход которого соединен с третьим управляющим входом блока частотных рециркуляторов, управляющим входом первого блока памят и первым управляюпгим входом коммутатора, отличающийся тем, что, с целью повышения быстродействия, в него введены блок ранжировки отсчетов, второй блок памяти, блок элементов И, блок генераторов опорны последовательностей и блок счетчиков причем выходы первого блока памяти соединены через последовательно соединенные блок ранжировки отсчетов и второй блок памяти с входами коммутатора, выход которого соединен с первым входом блока элементов И,труп па вторых входов которого соединена с выходами блока генераторов опорных последовательностей, а выходы блока

0

5

0

элементов И соединены через блок ключей с входами блока счетчиков, выходы которого подключены к входам блока выбора максимального числа, а тактовый вход блока счетчиков соединен с первым управляющим входом блока генераторов числовых последовательностей и четвертым выходом блока синхронизации, третий выход которого соединен с вторым управляющим входом блока генераторов опорных последовательностей, управляющим входом второго блока памяти и первым управляющим входом блока ранжировки отсчетов, второй управляющий вход которого подключен к пятому выходу блока синхронизации,шестой выход которого соединен с вторым управляющим и управляюгдим входами коммутатора и блока ключей соответственно.

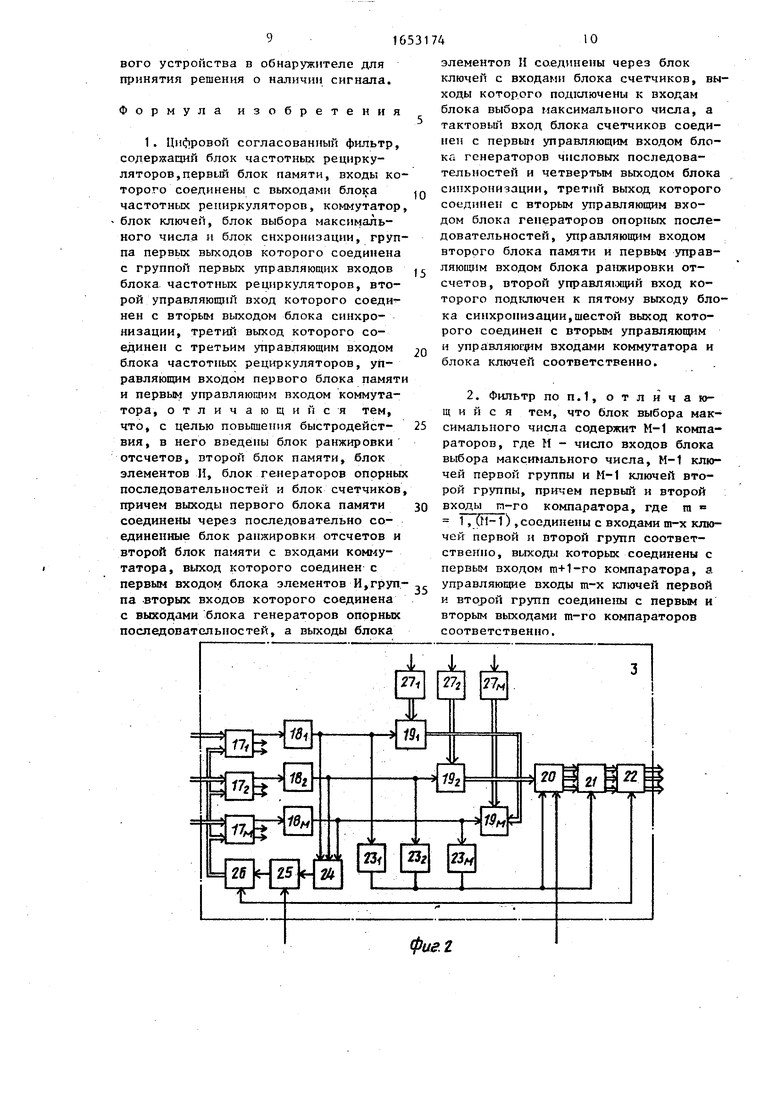

2. Фильтр поп.1, отличающийся тем, что блок выбора максимального числа содержит М-1 компараторов, где М - число входов блока выбора максимального числа, М-1 ключей первой группы и М-1 ключей второй группы, причем первый и второй входы п-го компаратора, где га « 1 ,(М-Т) .соединены с входами т-х ключей первой и второй групп соответственно, выходы которых соединены с первым входом m+1-ro компаратора, а управляющие входы т-х ключей первой и второй групп соединены с первым и вторым выходами т-го компараторов соответственно.

| название | год | авторы | номер документа |

|---|---|---|---|

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1992 |

|

RU2114514C1 |

| Цифровой согласованный фильтр сигналов с дискретной частотной манипуляцией | 1986 |

|

SU1438017A1 |

| ЦИФРОВОЙ СОГЛАСОВАННЫЙ ФИЛЬТР СИГНАЛОВ С ДИСКРЕТНОЙ ЧАСТОТНОЙ МАНИПУЛЯЦИЕЙ | 1990 |

|

RU2022485C1 |

| Многоканальное запоминающее устройство | 1985 |

|

SU1275547A1 |

| МНОГОКАНАЛЬНЫЙ ПАНОРАМНЫЙ ПРИЕМНИК | 1996 |

|

RU2115997C1 |

| Устройство для измерения защищенности сигнала от помех | 1989 |

|

SU1658400A2 |

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ И ПРИЕМА МОДУЛИРОВАННЫХ ПО ФАЗЕ И ЧАСТОТЕ СИГНАЛОВ | 2005 |

|

RU2288539C1 |

| Кодек для передачи информации с помощью имитостойких последовательностей сигналов сложной формы | 1987 |

|

SU1451719A1 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

| Устройство для определения характеристик случайного процесса | 1981 |

|

SU962978A1 |

Изобретение относится к радиотехнике и может быть использовано п обнаружителях цифровых сигналов с дискретной частотной манипуляцией„ Цель изобретения - повышение быстродействия, Цифровой согласованный фильтр содержит блок 1 частотных рециркуляторов, блоки 2 и 4 памяти, блок 3 ранжировки отсчетов, коммутатор 5, блок 6 элементов II, блок 7 ключей, блок 8 счетчиков, блок 9 выбора максимального числа, блок 10 генераторов опорных последовательностей и блок 11 синхронизации. Отсчеты входного сигнала на всех М частотах, формирующих сигнал, накопленные за время, равное длительности элемента сигнала Т ранжируются по степени их убывания, -«аменяются номерами частотных каналов, в которых они накоплены, и по л М/2 номерам каналов производится проверка порядка следования частот в каналах. Сигнал на выходе счетчика с наибольшим числом совпадений является откликом согласованного фильтра.1 з.п. ф-лы, 4 ил € (Л

фиг 2

Фиг.З

| Цифровой согласованный фильтр сигналов с дискретной частотной манипуляцией | 1984 |

|

SU1225040A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-05-30—Публикация

1988-07-04—Подача