головки,, имеющей пару контактов на каждый вывод схемы. Цель изобретения - повышение достоверности и информативности контроля.Это достигается путем обеспечения самоконтроля, исключения возбуадения одновременно всех импульсных трансформаторов, индикации порядкового номера контакта. Устройство содержит контактную голов ку 1, контакты 2, испытуемую ИС 3, импульсные трансформаторы 4.1-4.N (по одному на каждый вывод ИС 3), общую шину 5, резисторы 6.1-6.N, ло1

Изобретение относится к электронной промьшшенности и может быть-использовано в установках контроля электрических параметров интегральных схем для предварительной провер- ки наличия контактирования выводов контролируемой интегральной схемы с контактами контактной головки,имеющей пару контактов на каждый вывод схемы.

Цель изобретения - повыщение достоверности и информативности контроля за Счет обеспечения самокон,- троля, исключения возбуждения одновременно всех импульсных трансфор- маторов, индикации порядкового номера контакта.

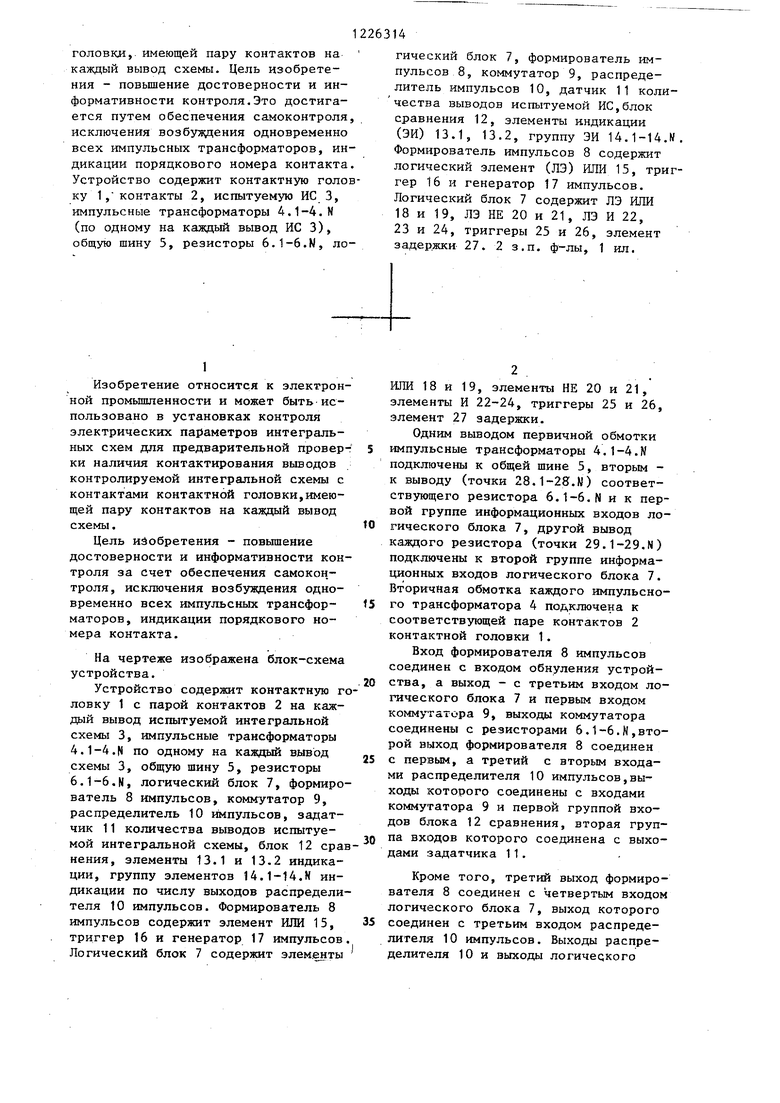

На чертеже изображена блок-схема устройства.

Устройство содержит контактную головку 1 с парой контактов 2 на каждый вывод испытуемой интегральной схемы 3, импульсные трансформаторы 4.1-4.N по одному на каждай вывод схемы 3, общую шину 5, резисторы 6.1-6.N, логический блок 7, формирователь 8 импульсов, коммутатор 9, распределитель 10 импульсов, задат- чик 11 количества выводов испытуемой интегральной схемы, блок 12 сравнения, элементы 13.1 и 13.2 индикации, группу элементов 14.1-14.N индикации по числу выходов распределителя 10 импульсов. Формирователь 8 импульсов содержит элемент ИЛИ 15, триггер 16 и генератор 17 импульсов Логический блок 7 содержит элем.е:нты

26314

гический блок 7, формирователь импульсов 8, коммутатор 9, распределитель импульсов 10, датчик 11 количества выводов испытуемой ИС,блок сравнения 12, элементы индикации (ЭЙ) 13.1, 13.2, группу ЭЙ 14.1-14.W, Формирователь импульсов 8 содержит логический элемент (ЛЭ) ИЛИ 15, триггер 16 и генератор 17 импульсов. Логический блок 7 содержит ЛЭ ИЛИ 18 и 19, ЛЭ НЕ 20 и 21, ЛЭ И 22, 23 и 24, триггеры 25 и 26, элемент задержки 27. 2 з.п. ф-лы, 1 ил.

5 О

15

20

25

35

30

ИЛИ 18 и 19, элементы НЕ 20 и 21, элементы И 22-24, триггеры 25 и 26, элемент 27 задержки.

Одним выводом первичной обмотки импульсные трансформаторы 4.1 -4.N подключены к общей шине 5, вторым - к выводу (точки 28.1-28.11) соответствующего резистора 6.1-6.N и к первой группе информационных входов логического блока 7, другой вывод каждого резистора (точки 29.1-29.N) подключены к второй группе информационных входов логического блока 7. Вторичная обмотка каждого импульсного трансформатора 4 подключена к соответствующей паре контактов 2 контактной головки 1.

Вход формирователя 8 импульсов соединен с входом обнуления устройства, а выход - с третьим входом логического блока 7 и первым входом коммутатсфа 9, выходы коммутатора соединены с резисторами 6.1-6.N,второй выход формирователя 8 соединен с первым, а третий с вторым входами распределителя 10 импульсов,выходы которого соединены с входами коммутатора 9 и первой группой входов блока 12 сравнения, вторая группа входов которого соединена с выходами задатчика 11.

Кроме того, третий выход формирователя 8 соединен с четвертым входом логического блока 7, выход которого соединен с третьим входом распределителя 10 импульсов. Выходы распределителя 10 и выходы логического

3

блока 7 соединены соответственно с элементами индикации 14.1 -14.N, 13.1 и 13.2

Первый, второй и третий входы формирователя 8 подключены соответ- 5 ственно к первому входу триггера 16, входам элемента ИЛИ 15, выход ко- тор ого подключен к первому выходу формирователя и к второму входу триггера 16, выход которого через генера- 10 тор 17 импульсов подключен к второму и непосредственно к третьему выходам

ходе распределителя 10 появляется сигнал, и элемент 14.1 индикации загорается, одновременно разрешается коммутатор 9 по первому входу.После 5 установки испытуемой схемы в контактную головку 1 , на первый вход формирователя 8 импульсов подается сигнат Пуск. По этому сигналу триггер 16 устанавливается в состояние 1 . Потенциалом с соответствующего выхода триггера 16 разрешается работа генератора 17 импульсов, блока.Первый импульс генератора с первого

(Выхода коммутатора 9 поступает на

Первая и вторая группы входов бло-15 1 й вход элемента ИЛИ 19, а через ка 7 соединены соответственно с входами элементов ИЛИ 18 и 19,. выход

резистор 6.1 на первичную обмотку трансформатора 4.1. Одновременно импульс с генератора 17 поступает на элемент 27, где задерживается на

элемента ИЛИ 18 подключен непосредственно к первому входу элемента И 22 и через элемент НЕ 20 к первым входам элементов И 23 и 24, Выход элемента ИЛИ 19 подключен непосредственно к вторым входам элементов и 22 и 23 и через элемент НЕ 21 к второму входу элемента И 24, второй вход блока непосредственно, третий через элемент 27 задержки подключены соответственно к первым входам триггеров 25 и 26 и третьим входам элементов И 22 и 24, выходы которых под-JQ выхода элемента ИЛИ 18 через элемент НЕ 20 будет разрешен по перво му входу элемент И 23, на второй вход которого через элемент ИЛИ 19 поступает импульс с точки 29.1, разрешающий прохождение стробирующ го импульса С с выхода элемента 27 задержки. Таким образом, на выходе элемента И 23, реализующего логиче кое произведение о Аbлс,появится им пульс, поступающий на первый вход рагпределителя 10 импульсов. По за нему фронту этого импульса состояние распределителя 10 изменится на следующее и сигнал появится на сле дующем, втором, его выходе, элемен 14.1 индикации погаснет, а 14.2 за горится, а коммутатор будет разреш по следующему, второму, входу и вт рой импульс с генератора 17 постуключены соответственно к второму входу триггера 25, первому выходу блока, второму входу триггера 26, выходы триггеров 25 и 26 подключены .соответственно к второму и третьему выходам блока.

Логический блок 7, распределитель 10 импульсов, блок 12 сравнения и формирователь 8 импульсов выполнены на микросхемах 533 серии, коммутатор 9 импульсов - на микросхемах 564 КТЗ трансформаторы 4 типа ТИМ1 32В ОЮ0.472. 045 ТУ, в качестве элементов индикации использованы светодиоды типа АЛ307БМ, а задатчик количества контактов выполнен на переключателях типа П2К ЕЩО.360.032 с соответствующим преобразователем кодов на микросхемах 533 серии.

Устройство работает следующим об- пит на опрос состояния следующей.

разом.

При включении питания устройства или при нажатии кнопки Сброс при включенном питании на первый вход элемента ИЛИ 15 подается сигнал обнуления триггеров 16, 25 и 26 и установки в исходное состояние распределителя 10 импульсов, на первом вы55

второй, пары контактов 2.

Если есть контактирование и эт пары контактов с выводом схемы 3, то аналогично указанному распреде тель 10 переключится в третье сос тояние.

Если контактирование есть по в выводам схемы 3, количество котор

5 10

263144

ходе распределителя 10 появляется сигнал, и элемент 14.1 индикации загорается, одновременно разрешается коммутатор 9 по первому входу.После 5 установки испытуемой схемы в контактную головку 1 , на первый вход формирователя 8 импульсов подается сигнат Пуск. По этому сигналу триггер 16 устанавливается в состояние 1 . Потенциалом с соответствую1 й вход элемента ИЛИ 19, а через

резистор 6.1 на первичную обмотку трансформатора 4.1. Одновременно импульс с генератора 17 поступает на элемент 27, где задерживается на

длительность переходного процесса в цепи прохождения импульса с выхода коммутатора 9. Если во вторичной обмотке есть контактирование между первым выводом интегральной схемы 3

и контактами 2 головки 1, амплитуда импульса в точке 28.1 равна уровню логического нуля элемента ИЛИ 18, а в точке 29.1 уровню логической единицы для элемента ИЛИ 19. Тогда с

выхода элемента ИЛИ 18 через эле

мент НЕ 20 будет разрешен по первому входу элемент И 23, на второй вход которого через элемент ИЛИ 19 поступает импульс с точки 29.1, разрешающий прохождение стробирующе- го импульса С с выхода элемента 27 задержки. Таким образом, на выходе элемента И 23, реализующего логическое произведение о Аbлс,появится импульс, поступающий на первый вход рагпределителя 10 импульсов. По заднему фронту этого импульса состояние распределителя 10 изменится на следующее и сигнал появится на следующем, втором, его выходе, элемент 14.1 индикации погаснет, а 14.2 загорится, а коммутатор будет разрешен по следующему, второму, входу и второй импульс с генератора 17 посту

второй, пары контактов 2.

Если есть контактирование и этой пары контактов с выводом схемы 3, то аналогично указанному распределитель 10 переключится в третье состояние.

Если контактирование есть по всем выводам схемы 3, количество которьпс

512

определено задатчиком 11, то по сигналу с выхода блока 12 сравнения кодов состояния распределителя 10 и задатчика 11 через второй вход элемента ИЛИ 15 триггер 16 обнуляется, запрещая работу генератора 17, а распределитель 10 импульсов установится в исходное состояние.

Если нет контактирования любого из выводов интегральной схемы 3, например i -го вывода, то в точке 28. i появится импульс с амплитудой, соответствуюпдей уровню логической единицы для элемента ИЛИ 18, Тогда элемент И 22 окажется разрешвнньм по двум.входам и стробирующий импульс с через этот элемент, реализующий логическое произведение а; л ,1 Ь; л с, установит триггер 25 в единичное состояние, загорится элемент 13,1 индикации, индицирующий некон-- тактирование го вывода схемы 3 с контактной парой 2. i головки 1, а порядковый номер этой кон-г актной пары будет индицироваться .элементом 14. 1 индикации, так как элемент И 23 по первому входу через элемент НЕ 20 запрещен, то стробирующий. импульс не проходит на вход распределителя 10 импульсов и последний „ своего состояния не меняет.

.После определения неконтактирования нажатием кнопки Сброс через третий вход формирователя 8 сов подается сигнал обнуления триггров 16, 25 и 26 и установки в исходное состояние распределителя 10 импульсов. Оператор поправляет испытуемую схему 3 нажатием кнопки Пуск подает сигнал запуска на первый вход формирователя 8 импульсов, начинается контроль контактирования выводов схемы 3 аналогично указанному.

Если же по тем или другим причинам импульс на любом из выходов в:ом мутатора 9 не появится, то через элементы ИЛИ 18 и 19 на входы элементов НЕ 20 и 21 поступит уровень логического нуля и импульс с выхода элемента 27 задержки пройдет через элемент И 24, реализующий логическо произведение а л Ь АС, устанавливая триггер 26 в единичное состояние, Загорится элемент 13,2 индикации, индицирующий возникновение неисправности в устройстве.

Формула изобретения

1.Ус7ройство для контроля контак- тргрова.ния выводов интегральной схемы, содержащее контактную головку с парой контактов на каждый вывод испытуемой интегральной схемы, импульсные трансформаторы, по одному на каждый вывод испытуемой интегральной схемы, первым выводом первичных обмоток соединенные с общей шиной, вторым выводом - с первым выводом соответствующего резистора и соот- ветствутадим входом первой группы входов лО Гического блока, вторичная обмотка каж,дого импульсного трансформатора, соединена с соответствую-. щей парой: контактов контактной, головки, формирователь импульсов, первый вход которого соединен с первым входом устройства, а первый выход - с вторым входом логического б.лока, от.пи чающееся тем, что, с целью повышения достоверности и информативности контроля, в него введены распределитель импульсов, коммутатор, задатчик количества выводов испытуемой интегральной схемы, блок сравнения и элементы индикации, причем вторые выводы ре- резисторов соединены с соответст- .зующим.и выходами коммутатора и с соответствующими входами второй группы входов логического блока, третий вход которого соединен с первым входом коммутатора и вторым выходом формирователя ш.1пульсов, информационные входы коммутатора соединены с первой группой входов блока сравнения н с соответствующими выходами распределителя импульсов, первый и второй входы которого соединены соответственно с первым и третьим вь ходами формирователя импульсов, а третий вход соединен с первым выходом логического блока, выходы задатчика количества выводов испытуемой интегральной схемы соединены с )зторой группой входов блока срав- пения, выход которого соединен с выходом устройства и вторым входом формирс1вателя импульсов, третий вход которог о соединен с вторым входом устройства, первый и второй элементы индикации подключены к второму и третьему выходам логического блока, группа элементов индикации соединена с соответствующими выходами распределителя импульсов.

2. Устройство по п.1, о т л и- чающееся тем, что логически блок содержит два элемента НЕ, два элемента ИЛИ, три элемента И, два триггера, элемент задержки, причем входы первого и второго элементов ИЛИ соединены соответственно с первой и второй группами входов блока, выход первого элемента ИЛИ соединен с первыми входами второго и третьего элементов И и через первый эле- мент НЕ - с первым входом первого элемента И, выход второго элемента ИЛИ соединен с вторым входом второго элемента И и через второй элемент НЕ - с вторыми входами первого и третьего элементов И, выводы первого, второго и третьего элементов соединены соответственно с первыми входами первого и второго триггеров и первым выходом блока, вторые входы первого и второго триггеров

Редактор. Цидика Заказ 2124/41

Составитель Н. Помякшева

Техред Л.Олейник Корректор м. Демчик

Тираж 728Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д,4/5

. Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная,4

соединены с вторым входом блока, третий вход которого через элемент задержки соединен с третьими входами элементов И, выходы первого и второго триггеров соединены соответственно с вторым и третьим выходами блока.

3, Устройство по П.1, о т л и- чающееся тем, что формирователь импульсов с одержит элемент ИЛИ, триггер и генератор импульсов, причем, первый вход триггера соединен с первьм входом блока, второй вход триггера соединен с первым выходом блока и выходом элемента ИЛИ, входы которого соединены соответственно с вторым и третьим входами блока, выход триггера соединен че- рез генератор импульсов с вторым выходом блока и непосредственно - с третьим выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля контантирования выводов интегральной схемы | 1980 |

|

SU890280A1 |

| УСТРОЙСТВО КОНТРОЛЯ КОНТАКТИРОВАНИЯ ИНТЕГРАЛЬНЫХ СХЕМ | 1991 |

|

RU2020498C1 |

| Устройство для контроля и сигнализации | 1990 |

|

SU1795494A1 |

| Устройство для контроля контактирования выводов интегральной схемы | 1989 |

|

SU1712907A1 |

| Устройство для контроля параметров электромагнитных реле | 1978 |

|

SU765783A1 |

| Устройство для контроля переходного сопротивления электрических контактов коммутационных изделий | 1983 |

|

SU1129566A1 |

| РЕЗЕРВИРОВАННЫЙ УСИЛИТЕЛЬ | 2001 |

|

RU2199843C1 |

| Устройство для предварительной проверки транзисторов | 1982 |

|

SU1101762A1 |

| Устройство автоматизированного контроля | 1987 |

|

SU1525680A2 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 1997 |

|

RU2116670C1 |

Изобретение относится к электронной промышленности и может быть использовано в устройствах контроля электрических параметров интегральных схем (ИС) для предварительной проверки наличия контактирования вы- водов ИС с контактами контактной W П.2 П.Н (Л N3 ND о: со

| Устройство для подключения электронных приборов к измерителю параметров | 1973 |

|

SU473132A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для контроля контантирования выводов интегральной схемы | 1980 |

|

SU890280A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-04-23—Публикация

1984-10-17—Подача