Изобр.етение относится к измериельной технике и может быть использовано для измерения мгновенных значений фазы сложного сигнала.

Целью изобретения является повыение точности за счет пол чения воичных кодов квадратурных составяющих, определения номера соответствующего квадранта и получение дво- -гчного кода о фазе в результате оразрядного сравнения двоичных коов квадратурных составляюпщх в соответствующих квадрантах,

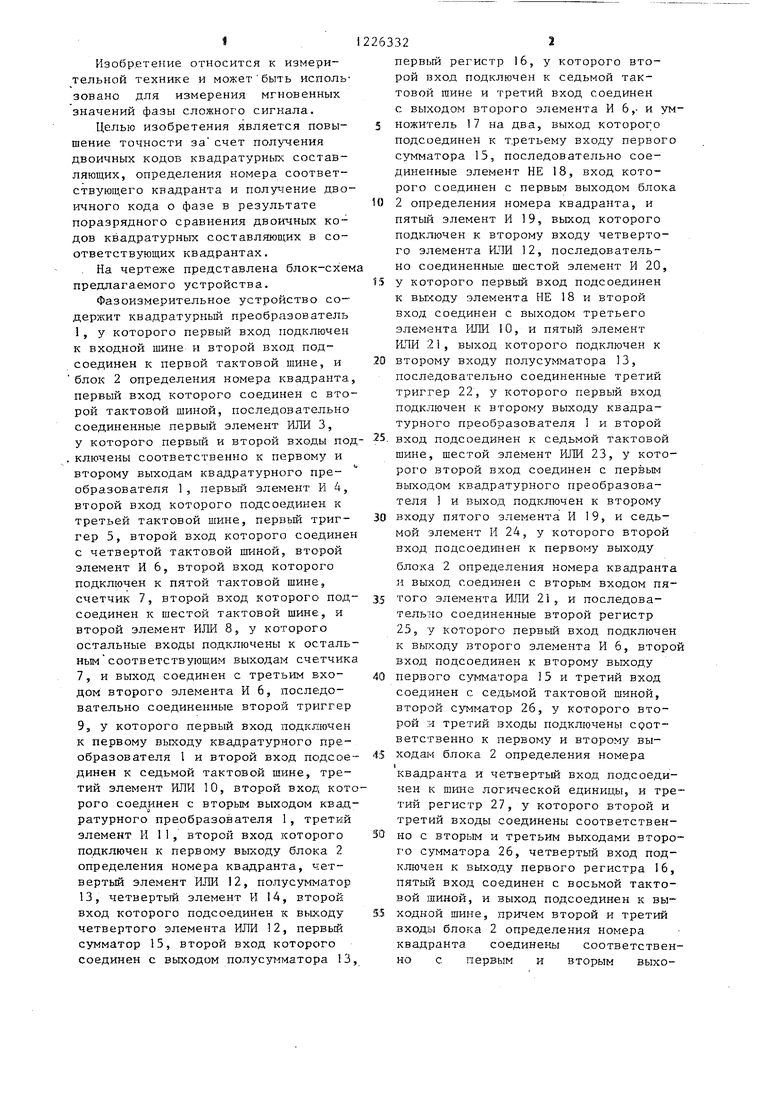

, На чертеже представлена блок-схема предлагаемого устройства.

Фазоизмерительное устройство соержит квадратурный преобразователь I, у которого первый вход подключен к входной шине и второй вход подсоединен к первой тактовой шине, и

блок 2 определения номера квадранта, первый вход которого соединен с второй тактовой шиной, последовательно соединенные первый элемент ИЛИ 3, у которого первый и второй входы подключены соответственно к первому и второму выходам квадратурного преобразователя 1, первый элемент И 4, второй вход которого подсоединен к третьей тактовой шине, первьш триггер 5, второй вход которого соединен с четвертой тактовой щиной, второй элемент И 6, второй вход которого подключен к пятой тактовой шине, счетчик 7, второй вход которого подсоединен к шестой тактовой шине, и второй элемент ИЛИ 8, у которого остальные входы подключены к остальным соответствующим выходам счетчика 7, и выход соединен с третьим входом второго элемента И 6, последовательно соединенные второй триггер

9j у которого первый вход подключен к первому ВЫХОДУ квадратурного преобразователя I и второй вход подсоединен к седьмой тактовой шине, третий элемент ИЛИ 10, второй вход которого соединен с вторым выходом квадратурного преобразователя 1, третий элемент И 11, второй вход которого подключен к первому выходу блока 2 определения номера квадранта, четвертый элемент ИЛИ 12, полусумматор 13, четвертый элемент И 14, второй вход которого подсоединен к вькоду четвертого элемента ИЛИ 12, первый сумматор 15, второй вход которого соединен с выходом полусумматора 13,

2263322

первый регистр 16, у которого второй вход подключен к седьмой тактовой шине и третий вход соединен с выходом второго элемента И 6,- и ум5 ножитель 7 на два, выход которог;о подсоединен к третьему входу первого сумматора 15, последовательно соединенные элемент НЕ 18, вход которого соединен с первым выходом блока

10 2 определения номера квадранта, и пятый элемент И 19, выход которого подключен к второму входу четвертого элемента ИЛИ 12, последовательно соединенные шестой элемент И 20,

1:5 у которого первый вход подсоединен к выходу элемента НЕ 18 и второй вход соединен с выходом третьего элемента ИЛИ 10, и пятый элемент {ПИ 21, выход которого подключен к

20 второму входу полусумматора 13, последовательно соединенные третий триггер 22, у которого первый вход подключен к второму выходу квадратурного преобразователя I и второй

25. вход подсоединен к седьмой тактовой

шине, шестой элемент ШЖ 23, у которого второй вход соединен с первым выходом квадратурного преобразователя i и выход подключен к второму входу пятого элемента И 19, и седьмой элемент И 24, у которого второй вход подсоединен к первому выходу

блока 2 определения номера квадранта и выкод соединен с вторым входом пятого элемента ИЛИ 21, и последовательно соединенные второй регистр 25, у которого первый вход подключен к вглкоду второго элемента И 6, второй вход подсоединен к второму выходу

первого сумматора 15 и третий вход соединен с седьмой тактовой шиной, второй сумматор 26, у которого второй и третий входы подключены соответственно к первому и второму выходам блока 2 определения номера i

квадранта и четвертый вход подсоединен к шине логической единицы, и третий регистр 27, у которого второй и третий входы соединены соответственно с вторым и третьим выходами второго сумматора 26, четвертый вход подключен к выходу первого регистра 16, пятый вход соединен с восьмой тактовой шиной, и выход подсоединен к выходкой шине, причем второй и третий входы блока 2 определения номера квадранта соединены соответственно с первым и вторым выхоами квадратурного преобразователя 1 , .

Фазоизмерительное устройство работает следующим образом.

Отсчетные значения сложного сигнала поступают на первый вход квадратурного преобразователя 1, на второй вход которого с первой тактовой шины подается двоичный код первого тактового сигнала. В момент появления двоичного кода первого тактового сигнала на первом и втором выходах квадратурного преобразователя 1 формируются двоичные коды синфазной и квадратурной составляющих сложного сигнала, которые являются косинусои- дальной и синусоидальной проекциями вектора аналитического сложного сигнала соответственно на оси X и У в прямоугольной системе координат, а фаза отсчитьшается от оси X против часовой стрелки до вектора аналитического сложного сигнала.

Синфазная и квадратурная составяющие с первого и второго выходов квадратурного преобразователя 1 поаются соответственно на второй и третий входы блока 2 определения номера квадранта, на первый вход которого с второй тактовой шины подается второй тактовьй сигнал. В блоке 2 определения номера квадранта в омент появления двоичного к ода второго тактового сигнала определяют номер квадранта в зависимости от знаков синфазной и квадратурной составляющих . .

. Например, если квадратурные составляющие положительны, то на первом и втором выходах блока 2 определения номера квадранта в момент появления двоичного кода второго тактового сигнала вырабатьшаются логические нули, соответствующие первому квадранту. При отрицательной синфазной составляющей и положительной квадратурной составляющей на первом и втором выходах блока 2 определения номера квадранта вырабатьшаются соответственно логические О и 1 соответствующие второму квадранту. При. отрицательных квадратурных составляющих на первом и втором выходах блока 2 определения номера квадранта вырабатьшаются соответственно логические 1 и О, соответствующие третьему квадранту. Наконец, при положительной синфазной и отрицательной квадратурной составляющих на первом и втором выходах блока 2 определения номера квадранта в момент появления двоичного кода второго

тактового сигнала вьфабатьгоаются логические единицы, соответствующие четвертому квадранту окружности, в который попадает вектор аналити ческого сложного сигнала при измерении мгновенных значений фазы этого сигнала.

Рассмотрим случай, когда динамический диапазон уменьшается в 4 раза и измеряется 219-й сектор и когда шестиразрядные двоичные коды

синфазной и квадратурной составляющих соответственно 010010 и 111000 будут иметь вид после уменьшения в 4 раза 000100 и 100110 с первого по шестой такты.

С первого и второго выходов квадратурного преобразователя 1 на второй и третий входы блока 2 определения номера квадранта, на первый вход

которого поступает двоичный код 100000 второго тактового сигнала с второй тактовой шины, подаются соответственно Ои,ОиО,ОиО, 1 и 1, О и 1, О и О, причем на второй вход квадратурного преобразователя поступает двоичный код 11I1П первого тактового сигнала с первой тактовой шины.

На первом и втором выходах блока

2 определения номера квадрацта формируются двоичные коды 111111 и 111111, которые соответствуют четвертому квадранту.

С первого и второго выходов квадратурного преобразователя 1 на первый и второй входы первого элемента ИЛИ 3 подаются соответственно двоичные коды 000100 и 100110 синфазной и квадратурной составляющих, в результате чего на выходе первого элемента ИЛИ 3 появляется двоичный код 100110, который поступает на первый, вход первого элемента И 4, на второй вход первого элемента И 4 подается

двоичный код 011111 третьего тактового сигнала с третьей тактовой шины, так что на выходе первого элемента И 4 получается двоичный код 000110, который поступает на первый

вход первого триггера 5. На второй вход первого триггера 5 с четвертой тактовой шины подается двоичный код 100000 четвертого тактового сигнала,

5

так что на выходе первого триггера 5 формируется двоичный код 000111 который поступает на первый вход второго элемента И 6. На второй вход второго элемента 6 с пятой тактовой шины подается двоичный код 11111 пятого тактового сигнала. На второй вход счетчика 7 с шестой тактовой шины подается двоичный код 100000 шестого тактового сигнала, перебра- сывающий счетчик 7, например, в кодовое состояние 010, так что логическая с второго выхода счетчика 7 поступает на второй вход второго элемента ИЛИ 8, остальные входы которого подключены к соответствующ выходам счетчика 7, и проходит на выход второго элемента ИЛИ 8, подсоединенный к, третьему входу второг элемента И 6, Таким образом, на вы- ходе второго элемента И 6 формируется двоичный код 000111, поступающи на первый счетньш вход счетчика 7, который будет принимать следующие кодовые состояния: 010, 010, 010, 011, 100 и 101, формируя на выходе второго элемента ИЛИ 8 логическую единицу.

С первого выхода квадратурного преобразователя 1 подается двоичный код 000100 синфазной составляющей на первый вход второго триггера 9, на второй вход которого поступает двоичный код 100000 седьмого такто- вого сигнала с седьмой тактовой шины, причем логическая единица, поступающая на второй вход второго триггера 9, по длительности более широкая, чем сигнал, поступающий в первый такт на первьм вход второ го триггера 9, так что на выходе второго триггера 9 получается двоичный код 1ПООО. Этот код подается на первый вход третьего элемен- .та ИЛИ 10, на второй вход которого поступает двоичный код 100110 квадратурной составляющей с второго выхода квадратурного преобразовател , так что на выходе третьего эле- мента ИЛИ 10 формируется двоичный код 111110, поступающий на первый вход третьего элемента И 11. На второй вход третьего элемента И 1i подается двоичный код 1П 1 11 с первог выхода блока 2 определения номера квадранта. На выходе третьего элемента И 1} получается двоичный

326

код 111110, который подается на первый вход четвертого элемента ИЛИ 12.

С второго выхода квадратурного преобразователя 1 подается двоичный код 100110 квадратурной составляющей на первый вход .третьего триггера 22, на второй вход, которого поступает двоичный: код 100000 седьмого тактового сигнала с седьмой тактовой шины причем логическая единица, поступающая на второй вход третьего триггера 22, по длительности более широкая, чем сигнал, поступаюпщй в первый такт на первый вход третьего триггера 22, так что на выходе третьего триггера 22 получается двоичный КОД 111000. Этот код подается на первый вход шестого элемента ИЛИ 23, на второй вход которого поступает двоич ньш код 000100 синфазной составляющей с первого выхода квадратурного преобразователя 1, так что на выходе шестого элемента ИЛИ 23 формируется двоичный код 111100, поступающий на первьш вход седьмого элемента И 24. На второй вход седьмого элемента И 24 подается двоичный код 111П1 с первого выхода блока 2 определения номера квадранта. На выходе седьмого элемента И 24 получается двоичный код 111100, который подается на второй вход пятого элемента. ИЛИ 21, Двоичный код 111111 с первог выхода блока 2 определения номера квадранта поступает также на вход элемента FIE 18, так что на его выходе формируется двоичный код 000000, который подается на первые входы пятого 19 и BjecToro 20 элементов И. Двоичный код с выхода шестого элемента 23 подается также на второй вход пятого элемента И 19, так что на выходе пятого элемента 19 получается двоичный код 000000, поступающий на второй вход четвертого элемента ИЛИ 12, на выходе которого в свою очередь формируется двоичный код 111110, подаваегфш на первый вход полусумматора 13 и на второй вход четвертого элемента И 14. Двоичный код с выхода третьего элемента ИЛИ

10 подается также на второй вход шестого элемента И 20, так что на выходе Бзестого элемента И 20 получается двоич1п 1Й код 000000, поступающий на первьш вход пятого элемента ИЛИ 21, на выходе которого в свою очередь формируется двоичный код

Ill 100, подаваемый на второй вход полусумматора. На выходе полусумматора 13 формируется двоичный код 000010, поступающий на первьш вход четвертого элемента И 14 и на второ вход первого сумматора 15, На выход четвертого элемента И 14 получается двоичный код 000010, поступающий на первый вход первого сумматора 15. Двоичный код 000111 с выхода второго элемента И 6 подается на первьш вход второго регистра 25, на вт рой вход которого поступает двоичны код с второго выхода первого сумматора 15, и поступает на т эетий вход первого регистра 16,на первый вход которого подается двоичный код с первого выхода первого сумматора 15. На второй и третий входы первог и второго регистров 16 и 25 соответственно поступает двоичный код 100000 седьмого тактового сигнала с седьмой тактовой шины, причем логическая единица, поступающая соответственно на второй и третий входы первого и второго регистров 16 и 25 по длительности более.широкая, чем сигналы, поступающие в первый такт с первого и второго выходов первого сумматора 15, так что первый и второй регистры 16 и 25 в первый такт находятся в нулевом логическом состоянии. Поэтому с выхода четвертого элемента И 14 и с выхода полусумматора 13 соответственно на первьш и второй входы, соответствующие нечетной группе входов, первого сумматора 15 поступают двоичные коды 000010 и 000010, совокупность которых составляет кодовую комбинацию, соответствующую отдельным двоичным кодам с первого по щестой такты: 000000, 000000, 000000, 000000, 111111 и 000000. Эти двоичные коды суммируются с двоичными соответствующими кодами, поступающими с выхода умножителя 17 на два на третий вход первого сумматора 15, соответствующий четным входам первого сумматора 15. Умножитель 17 на два удваивает кодовые комбинации, поступающие с выхода первого регистра 16.

В первый такт независимо от состяний первого сумматора 15 первый и второй регистры 16 и 25 находятся в нулевом состоянии, так как на их соответственно втором и третьем вхо263328

дах наблюдается логическая единица, поступающая с седьмой тактовой шины.

Во второй и третий такты первый и второй регистры 16 и 25 будут также 5 находиться в нулевом состоянии, так как на их соответственно третий и первый входы подаются логические нули с выхода второго элемента И 6. В четвертый такт на первый, вто10 рой и третий входы первого су 1мато- ра 15 подаются нулевые двоичные коды, которые соответствуют нулевьм состояниям на первом и втором выходах первого сумматора 15, так что первый

15 и второй регистры 16 и 25 останутся в нулевых состояниях, хотя на их соответственно третьем и первом входах наблюдается логическая единица, пос-. тупающая с выхода второго элемента И 6

20 В пятьш такт на первый и второй входы первого сумматора 15 подаются логические единицы, соответствующие отрицательной логической единице в дополнительном коде, которая, сумми25 руясь с логическим нулем, поступающим с выхода умножителя 17 на два на третий вход первого сумматора 15, появляется на первом и втором выходах первого суьматора 15. Знак отрица30 тельной логической единицы с второго выхода первого сумматора 15 поступает на второй вход второго регистра 25, а ее мантисса 11111 подается с первого выхода первого сумматора 15 на 35 первый вход первого регистра 16,

так что на выходах первого и второго регистров 16 и 25 появятся соответственно двоичные коды 11111 и 1 в момент появления логической единицы 40 в пятый такт на выходе второго элемента И 6 . 1

В щестой такт на первый и второй

входы первого сумматора 15 подаются логические нули, а на третий вход

первого сумматора 15 поступает дво- ичньш код , который соответствует отрицательным двум единицам младщего разряда (е.м.р.), получающимся в результате удвоения мантиссы

0 11111 отрицательной логической единицы, по ступающей с выхода первого регистра 16 на вход умножителя 17 на два. В результате суммирования на первом выходе первого сумматора

55 15 появится двоичный код 11110, а на втором выходе первого сумматора I5 будет наблюдаться логическая единица, которые соответственно повторятся

на выходах первого и второго регистров 16 и 25 в момент появления логической единицы в шестой такт на выходе второго элемента И 6.

Таким образом, в Шестой такт на , первый, второй, третий и четвертый входы второго сумматора 26 подаются логические единицы соответственно с выхода второго регистра 25, с первого и второго выходов блока 2 опре- 10 деления номера квадранта и с шины логической единицы, так что логические единицы на втором, третьем и четвертом входах второго сумматора 26 соответствуют двоичному коду 311 15 на четной группе входов второго сумматора 26, на первый вход которого поступает двоичный код 111 (нечетная группа входов второго сумматора 26) с выхода второго регистра 25. Резуль- 20 тат от суммирования этих двоичных кодов на первом, втором и третьем выходах второго сумматора 26 соот- ветствершо будет иметь вид 110. Этот двоич1Еый код с первого, второго 25 и третьего выходов второго сумматора 26 подается соответственно на первый, второй и третий входы третьего регистра 27, соответствующие старп1им разрядам третьего регистра 27. На ЗО остальные младшие разряды третьего регистра 27 с выхода первого регистра 16, подключенного к четвертому входу третьего регистра 27,поступает двоичный код 11110, так что в момент 5 появления логической единицы в двоичном коде 000001 восьмого тактового сигнала, поступающего с восьмой тактовой шины на пятьш вход третьего регистра 27, на выходе третьего ре- 40 гистра 27 и выходной шине появится двоичный код 1101111 О, соответствующий в десятичной системе счисления 222-му сектору, т.е. при снижении динамического диапазона в четьфе. 45 раза ошибка измерения составила 3 е.м.р,, что соответствует высокой точности измерения фазы.

Следует отметить, что восемь тактовых сигналов подаются с выходов 50 формирователя тактовых импульсов, запускаемого от задающего генератора, который генерирует, например, синусоидальный сигнал.

Сравнительные испытания предлага- 55 емого и известного фазоизмерительных устройств показали, что введение в предлагаемое фазоизмерительное устройство указанных блоков и связей позволило увеличить точность измерения мгновенных значений фазы сложного сигнала в 15 раз в предельном случае по сравнению с известным при условии, что разрядность двоичного кода квадратурных составляющих сложного сигнала равна 8 и динамический диапазон изменения квадратурных составляющих сложного сигнала уменьшен вдвое по отношению к его максимальному значению.

Формула и зобретения

Фазоизмерительное устройство, содержащее квадратурный преобразователь, у которого первый вход подключен к входной шине, второй вход подсоединен к первой тактовой шине, и блок определения номера квадранта, первьй вход которого соединен с второй тактовой шиной, отличающееся тем, что, с целью повьше- ния точности, в него введены последовательно соединенные первый элемен ИЛИ, у которого первый и второй, вход подктпочены соответственно к первому и второму выходам квадратурного преобразователя, первый элемент И, второй вход которого подсоединен к третьей тактовой шине, первый триггер, второй вход которого соединен с четвертой тактовой шиной, второй злемерЕт И, второй вход которого под- кхпочен к пятой тактовой шине, счет- чик, второй вход которого подсоедине к шестой тактовой шине, и второй элемент ИЛИ, у которого остальные входы подключены к остальным соот- ветствуюищм вьпсодам счетчика, и выхо соединен с третьим входом второго элемента И, последовательно соединенные второй триггер, у которого первьй вход подключен к первому выходу квадратурного преобразователя, второй вход подсоединен с седьмой тактовой шине, третий элемент ИЛИ, второй вход которого соединен с вторым выходом квадратурного преобразователя, третий элемент И, второй вход которого подключен к первому выходу блока определения номера квадранта, четвертый элемент ИЛИ, полусумматор, четвертый элемент И, второй вход которого подсоединен к выходу четвертого элемента ИЛИ, первый сумматор, второй вход которого соединен с выходом полусумматора.

11

первыл регистр, у которого второй вход подключен к седьмой тактовой шине, третий вход соединен с выходом второго элемента И, и умножитель на два, выход которого подсоединен к третьему входу первого сумматора, последовательно соединенные элемент НЕ, вход которого соединен с первым выходом блока определения номера квадранта, и пятый элемент И, выход которого подключен к второму входу четвертого элемента ИЛИ, последовательно соединенные шестой элемент И, у которого первый вход подсоединен к выходу элемента НЕ, а второй вход соединен с выходом третьего элемента ИЛИ, и пятый элемент ИЛИ, выход которого подключен к втор-ому входу полу- умматора, последовательно соединенные третий триггер, у которого первый вход подключен к второму выходу квадратурного преобразователя второй вход подсоединен к седьмой тактовой шине, шестой элемент ИЛИ, у которого второй вход соединен с первым выходом квадратурного преобразователя, а выход подключен к второму входу пятого элемента И, и седьСоставитель В, Шубин Редактор Р. Цицика Техред Л.Олейник Корректор Л. Патай

Заказ 2125/42 Тираж 728Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытшт 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

26332 12

мой элемент И, у которого второй вход подсоединен к первому выходу блока определения номера квадранта, а выход соединен с вторым входом пя- 5 того элемента ИЛИ, и последовательно соединенные второй регистр, у которого первый вход подключен к выходу второго элемента И, второй вход подсоединен к второму выходу первого 10 сумматора,а третий вход соединен с седьмой тактовой шиной, второй сумматор, у которого второй и третий входы подключены соответственно к первому и второму выходам блока определения

номера квадранта, а четвертый вход подсоединен к пшне логической единицы, и третий регистр, у которого второй и третий входы соединены соответственно с вторым и третьим выхог

дами второго сумматора, четвертый вход подключен к выходу первого регистра, а пятый вход соединен с восьмой тактовой шиной, и выход подсоединен к .выходной шине, причем второй

и третий входы блока определения номера квадранта соединены соответст- венно с первым и вторым выходами квадратурного преобразователя.

| название | год | авторы | номер документа |

|---|---|---|---|

| Функциональный преобразователь угла поворота вала в код | 1984 |

|

SU1218465A1 |

| Устройство для измерения мгновенных значений напряжения | 1987 |

|

SU1499250A1 |

| ФАЗОМЕТР С ГЕТЕРОДИННЫМ ПРЕОБРАЗОВАНИЕМ ЧАСТОТЫ | 2013 |

|

RU2551837C2 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Устройство для моделирования ветви графа | 1986 |

|

SU1348847A1 |

| УСТРОЙСТВО ДЛЯ ДЕТЕКТИРОВАНИЯ ГРУПП БИТ В БИНАРНОЙ ПОСЛЕДОВАТЕЛЬНОСТИ | 2020 |

|

RU2728957C1 |

| ИЗМЕРИТЕЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ ГАРМОНИЧЕСКИХ СОСТАВЛЯЮЩИХ ТОКА И НАПРЯЖЕНИЯ | 1994 |

|

RU2093841C1 |

| КАРДИОМОНИТОР КВАНТИЛЬНЫЙ | 1994 |

|

RU2107455C1 |

| СИСТЕМА АВТОМАТИЧЕСКОГО УПРАВЛЕНИЯ ДРОНОМ СОПРОВОЖДЕНИЯ ВОДОЛАЗА | 2017 |

|

RU2672505C1 |

| Аналого-цифровой преобразователь | 1986 |

|

SU1325696A1 |

Изобретение относится к измерительной технике и может быть использовано для измерения мгновенных значений фазы сложного сигнала. Цель изобретения - повьшение точности измерения. Это достигается путем получения двоичных кодов квадрати- рующих составляющих,, определения номера соответствующего квадранта и получения двоичного кода фазы в результате поразрядного сравнения двоичных кодов квадратурных составляющих в соответствующих квадрантах. Устройство содержит квадратурный преобразователь 1, блок 2 определения номера квадранта, логические элементы (ЛЭ) ИЛИ 3, 8, 10, 12,.21 и 23, ЛЭ И 4, 6, 11, 14, 19, 20, 24 и 26, триггеры 5, 9 и 22, счетчик 7, полусумматор 13, сумматоры 15 и 26, регистры 16, 25 и 27, умножитель 17 на два, ЛЭ НЕ 18. По срав 1ению с прототипом точность измерения мгновенных значений фазы сложного сигнала в данном устройстве повьшена в 15 раз. 1 ил.

| Авторское свидетельство СССР, № 661398, кл | |||

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Фазоизмерительное устройство | 1976 |

|

SU608107A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-04-23—Публикация

1984-07-31—Подача