Изобретение относится к измерительной технике и может быть использовано при измерении мгновенных значений переменного напряжения.

Цель изобретения - повышение точности измерения мгновенных значений напряжения переменного злектричес- кого сигнала.

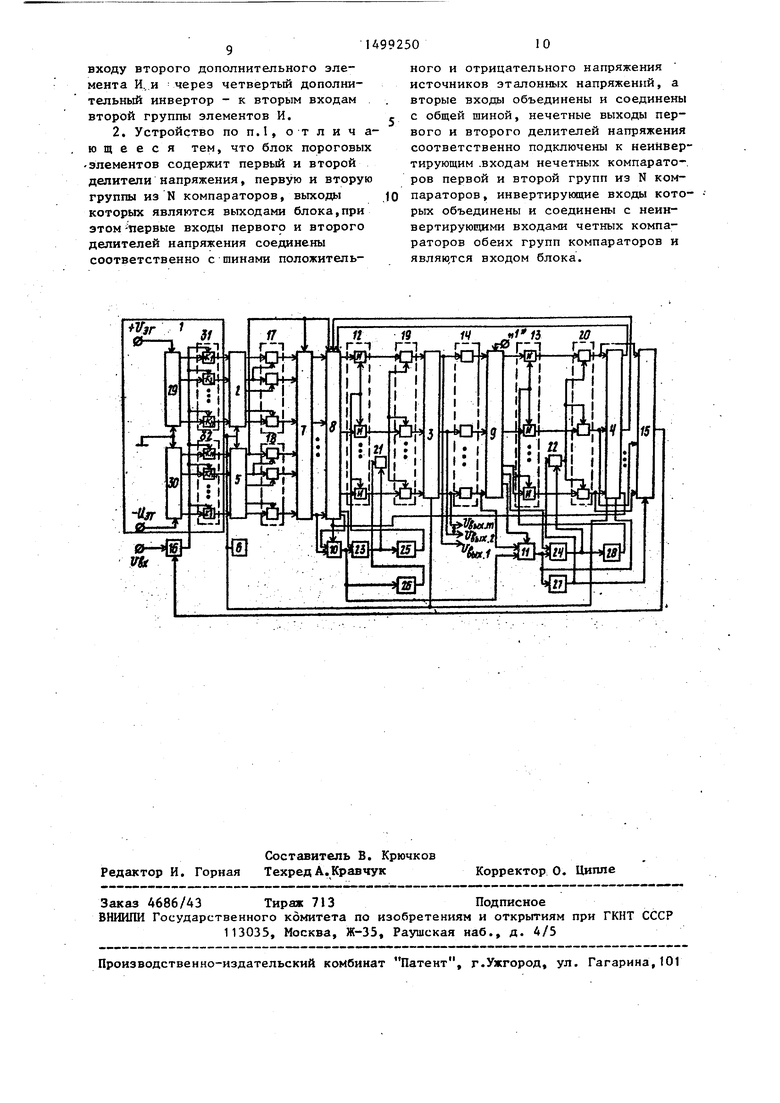

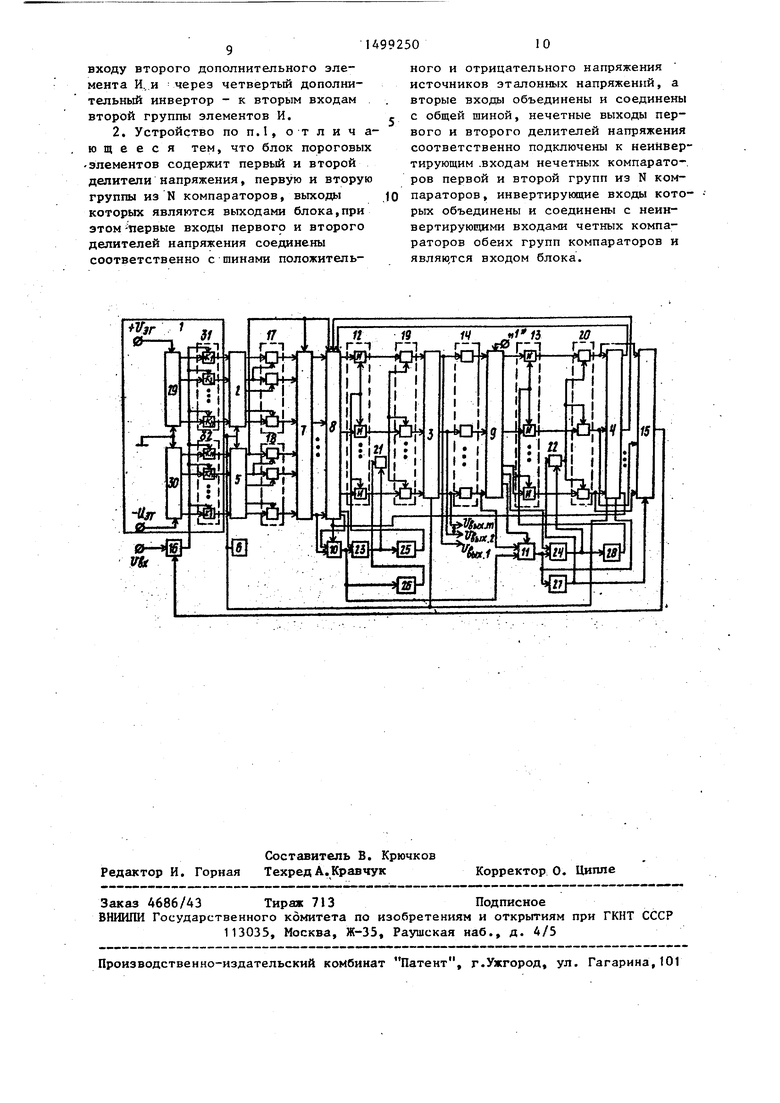

На чертеже представлена функциональная схема устройства.для измерения мгновенных значений напряжения

Устройство содержит блок 1 пороговых элементов, регистры 2-5, генератор 6 импульсов, декодер 7, сумматоры 8-11, группы 12 и 13 из М элементов И, группу 14 из М инверторов, цифреаналоговый преобразователь (ЦАП) I5, вычитатВль 16, группы 17

и 18 из г элементов ИСКЛЮЧАЮЩЕЕ ШШ , группы 19 и 20 из М элементов ИЛИ, элементы И 21 и 22, элементы ИСКЛЮЧА- ЮВ1ЕЕ или 23 и 24, инверторы 25-28, а блок 1 пороговых элементов содержит первый 29 и второй 30 делители напряжения, группы 31 и 32 из N компараторов. При этом первые входьт первого 29 и второго 30 делителей напряжения соединены соответственно с шинами положительного и отрицательного напряжения источников эталонных напряжений, а вторые входы - с общей шиной. Выход генератора импульсов соединен с управлягаци- ми входами регистров 2-5. Входная шина подключена к первому входу вы-i читателя 16, второй вход которого

4 СО CD Ю СП

314

подключен к выходу ПАП 15. Нечетные выходы первого 29 и второго 30 делителей напряжения соответственно подключены к неинвертирующим входам нечетных компараторов первой. 31 и второй 32 групп компараторов, инвертирующие входы которых объединены и соединены с неинвертирующими входами четных компараторов обеих групп 31 и 32.

Выходы компараторов первой 31 и второй 32 групп через первый 2 и чевертый 5 регистры соединены соот- ветственно с первыми входами первой 17 и второй 18 групп из N элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, вторые входы кото- рьпс соединены с нечетными выходами первого 2 и четвертого 5 регистров.

Выходы первой 17 и второй 18 групп из N элементов ИСКЛЮЧАКЧТСЕ ИЛИ через детектор 7 подключены к первым входам первого .сумматора 8,

выходы которого подключены к первым

входам первой группы 12 из М элементов И, вторые входы которых объединены и подключены к выходу инвертора 25.. Вьпсоды первой группы 12 из М зле ментов И соединега 1 с первыми входа- ми первой группы 19 из М элементов ШШ, вторые входы которых объединены и подключены к выходу элемента И 21, а выходы - через второй регистр 3 к выходным клеммам устройст- ва, через группу 14 инверторов к первым входам второго сумматора 9, вторые входы которого объединены и соединены с шиной логической единищы, а выходы подключены к первым входам второй группы 13 элементов И, вторые входы которых объединены и соединены с выходом инвертора 28. Выходы второй группы 13 элементов И подключены к первым входам второй группы 20 элементов ИЛИ, вторые входы которых объединены и соединены с выходом элемента И 22, Выходь второй группы 20 элементов ИЛИ соединены с информационными входами ЦАП 15 и третьего регистра 4, выходы которого подключены к вторым входам первого сумматора 8, управляющий вход которого соединен с управляющим входом декоде

ра 7 и с первым выходом четвертого регистра 5.

N-й выход декодера 7 соединен с первым входом третьего сумматора 10, второй и третий входы которого

s 0

5

0 5 0 5 о

5

подключены соответственно к N-му выходу и выходу Переполнение первого сумматора 8. Выход третьего сумматора 10 соединен с вторыми входами . элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 23, четвертого сумматора 11, а также через инвертор 26 - с первым входом элемента И 21, выход которого подключен к вторым входам первой группы 19 элементов ШШ. N-й выход второго регистра 4 через N-й инвертор группы 14 инверторов подключен к второму входу четвертого сумматора I1, третий вход которого подключен к выходу Перенос второго сумматора 9, N-й выход которого подключен к первому входу элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 24, второй вход которого соединен с выхо- длм четвертого сумматора 11 и с вторым управляющим входом третьего регистра 4 и через инвертор 27 с первым входом элемента И 22 и с управляющим входом ЦАП 15. Выход элемента ИСКПЮЧАЮРЩЕ ИЛИ 24 подключен к второму входу элемента И 22 и через инвертор 28 к вторым входам второй группы 13 элементов И.

Устройство для измерения мгновенных значений напряжения работает сле- дующим образом.

В вычитателе 16 из входного сигнала, поступающего на его первый вход с входной шины, вычитается ступенчатый компенсирующий сигнал, подаваемый на его второй вход с выхода ЦАП 15, так, что образуется на его выходе разностный сигнал, который поступает на объединенные входы групп 31 и 32 компараторов. На входы компараторов групп 31 и 32 подаются опорные напряжения от двух стабилизированных источников питания -HJgr и -Пэт через первый 29 и второй 30 дет лители напряжения, которые определяют порог срабатывания каждого компаратора первой и второй групп 31 и 32, а точнее определяют комбинацию на выходах соответствующих компараторов в зависимости от величины и знака разностного сигнала U вьгчитателя 16.

Опорные напряжения и выходной разностный сигнал UU на входы компараторов групп 31 и 32 подаются следующим образом: на нечетные компараторы опорные напряжения подаются на их неинвертирующие входы, и выходной разностный сигнал поступает

на их. инвертирующие входы, а на четные компараторы - наоборот.

В зависимости от абсолютной величины и знака выходного разностного сигнала uU первая 31 и вторая 32 ,группы компараторов формируют двоич- .ный код, который по параллельным каналам в виде цифрового кода поступает на входы регистров 2 и 5.

Первый 2 и четвертый 5 регистры осу11 ествляют привязку цифровой информации к тактовой частоте при помощи тактового сигнала, поступающего на их первые входы с выхода генератора 6 импульсов, и в таком виде подается на соответствующие входы первой 17 и второй 18 групп элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, с выходов которых двоичный код поступает на соответствующие входы декодера 7, который преобразует двоичный код в до- полнительньй код.

Далее эти двоичные сигналы, представляющие двоичный разностный сигнал ДА в параллельном коде поступат ют на первый сумматор 8, в котором происходит суммирование двоичного разностного сигнала ЛА с двоичным сигналом обратной связи Аре задержанным на один такт третьим регистром 4. В результате этого на выходе первого сумматора 8 вырабатывается цифровой эквивалент мгновенных значений напряжения

6)(

А

ос

ЛА

0

5

0

5

0

сумматор 11, элемент ИСКЛЮЧАЮЩЕЕ ИШ 24 и инверторы 27 и 28 предназначены для защиты от переполнения второго суммарного сигнала с выхода второго сумматора 9 на соответствующие входы регистра 4.

Если в первом сумматоре 8 нет переполнения, то на выходе элемента ИСКЛЮЧАЙИШЕ ИЛИ будет логический О, который инвертируется инвертором 25 в логическую 1, открывающую первую группу 12 элементов И.

Первый суммарный сигнал с выходов элементов И группы 12 через первую группу 19 элементов ИЛИ поступает на соответствующие входы второго регистра 3, в котором производится запись мгновенного значения измеряемого напряжения по сигналу с выхода генератора 6 импульсов, представляющего заполненное на такт мгновенное значение измеряемого напряжения, которое поступает на выходные клеммы устройства.

Этот же сигнал после инвертирования группой 14 инверторов поступа-ет на первые входы сумматора 9, где суммируется с логической единицей, в результате чего на -выходе сумматора 9 формироуется второй суммарный сигнал

В

2А,

- А,

Ы ex;., г

где В, - второй суммарный сигнап; Аьц - цифровой эквивалент мгновенных значений напряжения.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ РАДИОТЕЛЕМЕТРИЧЕСКИХ СИГНАЛОВ | 1994 |

|

RU2126139C1 |

| Двухтактный аналого-цифровой преобразователь | 1985 |

|

SU1336236A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1336237A1 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| Многоканальный приемник с кодовым разделением каналов для приема сигналов с квадратурной m-ичной амплитудно-инверсной модуляцией | 2017 |

|

RU2669371C1 |

| Устройство для регистрации информации | 1989 |

|

SU1698895A1 |

| Устройство для определения действующего значения сигнала | 1983 |

|

SU1141421A1 |

| Аналого-цифровой преобразователь | 1984 |

|

SU1368990A1 |

| Аналого-цифровой преобразователь | 1989 |

|

SU1640823A1 |

| Цифроаналоговый преобразователь с автоматической коррекцией нелинейности | 1985 |

|

SU1287290A1 |

Изобретение относится к измерительной технике и может быть использовано при измерении мгновенных значений напряжения. Цель изобретения - повышение точности. Устройство для измерения мгновенных значений напряжения содержит блок пороговых элементов, четыре регистра, генератор импульсов, декодер, четыре сумматора, две группы элементов И группу инверторов, цифроаналоговый преобразователь, вычитатель, две группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, две группы элементов ИЛИ, два элемента И, два элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, четыре инвертора. Блок пороговых элементов содержит два делителя напряжения, и две группы компараторов. Повышение точности достигается за счет вычисления последующего значения приращения входного сигнала. 1 з.п. ф-лы, 1 ил.

где Ag - цифровой эквивалент мгновенных значений напряжения Аре - двоичный сигйал обратной

связи; АА - двоичный разностный сигнал

Полученный таким образом цифровой эквивалент мгновенных значений напряжения поступает на соответствующие входы первой группы 12 из М элементов и.

Первая 12 и вторая 13 группы элементов И, группа 19 элементов ИЛИ, третий сумматор 10, элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 23, инверторы 25 и 26 предназначены для защиты от пе-. реполнения первого суммарного сигнала с выхода первого сумматора В на соответствующие входы второго регистра 3.

Также элементы И 21 и 22, вторая группа 20 элементов ИЛИ, четвертый

Если во втором сумматоре 9 нет ;

40 переполнения, то на выходе элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 24 будет логический О, который в инверторе 28 инвертируется в логическую 1, открывающую все элементы И группы 13. Вто45 рой суммарный сигнал с выходов группы 13 открытых элементов И череэ группу 20 элементов ИЛИ поступает на соответствующие входы третьего регистра 4, запоминающего второй сум50 марный сигнал с приходом очередного импульса на его вход с выхода генератора 6 импульсов.

Задержанный на такт второй суммарный сигнал представляет собой сиг55 нал обратной связи на соответствующих выходах третьего регистра 4, так что

лес

Bi.,

71499250

Второй суммарный сигнал с выходов второй группы 20 элементов ИЛИ поступает также на соответствующие входы цифроаналогового преобразователя 15 для преобразования в ступенчатьш компенсирующий сигнал, -которьй в вы- читателе 16 уравновешивает измеряемое напряжение.

Таким образом, за счет вычисле- JQ ния последующего значения приращения выходного сигнала повышается точность измерения,

Формула

изобретения 5

второй дополнительные элементы ИСКЛЮ- 40 рез второй дополнительный инвертор

ЧАЮЩЕЕ ИЛИ, четыре дополнительных инвертора, при этом выходы блока по-г роговых элементов через первый и четвертый регистры соединены соответственно с первыми входами первой д и второй групп элементов ИСКПЮЧАЩЕЕ ИЛИ, вторые входы которых соединены с четнЬтми выходами первого и четвер - того регистров, управляющие входы регистров объединены, и соединены с Q вьпсодом генератора импульсов, выходы первой и второй групп элементов ИСКЛЮЧАЮЩЕЕ ИЛИ через декодер подключены к первым входам первого сумматора, выходы которого подключены к первым входам первой группы элемен- тов И, вторые входы которых объединены и подключены к выходу первого дополнительного инвертора, выходы

с первым входом первого дополнитель ного элемента И, выход М-го выхода второго регистра через гй инвертор группы инверторов подключен к второ му входу четвертого сумматора, тре тий вход которого подключен к выходу Перенос второго сумматора, N-й выход которого подключен к первому входу второго дополнительного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с входом четверто го сумматора и с вторым управляющим входом третьего регистрами через тр тий дополнительный инвертор - с пер вым входом второго дополнительного. элемента И и с управляющим входом цифроаналогового преобразователя, в ход второго дополнительного элемент ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к второму

8

первой группы элементов И соединены с первыми входами первой группы элементов ИЛИ, вторые входы которых объединены и-подключены к выходу . первого дополнительного элемента И, а выходы через второй регистр - к выходным клеммам устройства и через группу из К инверторов - к первым входам второго сумматора, вторые входы которого объединены и соединены с. шиной логической единицы, а выходы

подключены к первым входам второй группы элементов И, вторые входы которых объединены и соединены с . выходом четвертого дополнительного инвертора, выходы второй группы элементов И подключены к первым входам второй группы элементов ИЛИ, вторые входы которых объединены и соединены с выходом второго дополнительного элемента И, выходы второй группы элементов ИЛИ соединены с информационными входами цифроаналогового преобразователя и третьего регистра, выходы которого подключены к вторым входам первого сумматора-, управляю-и щий вход которого соединен с управляющим входом декодера и с первым выходом четвертого регистра, N-й выход декодера соединен с первым входом третьего сумматора, второй и третий входы которого подключены соответственно к N-му выходу и выходу ПЕРЕПОЛНЕНИЕ первого сумматора, выход третьего сумматора соединен с вторыми входами первого дополнительного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и четвертого сумматора, а также чес первым входом первого дополнительного элемента И, выход М-го выхода второго регистра через гй инвертор группы инверторов подключен к второму входу четвертого сумматора, третий вход которого подключен к выходу Перенос второго сумматора, N-й выход которого подключен к первому входу второго дополнительного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с входом четвертого сумматора и с вторым управляющим входом третьего регистрами через третий дополнительный инвертор - с пер- вым входом второго дополнительного. элемента И и с управляющим входом цифроаналогового преобразователя, выход второго дополнительного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ подключен к второму

входу второго дополнительного элемента И., и через четвертый дополнительный инвертор - к вторым входам второй группы элементов И.

ного и отрицательного напряжения источников эталонных напряжений, а вторые входы объединены и соединены с общей шиной, нечетные выходы первого и второго делителей напряжения соответственно подключены к неийвер- тирующим .входам нечетных компарато-. ров первой и второй групп из N компараторов , инвертирующие входы которых объединены и соединены с неин- вертируюпщми входами четных компараторов обеих групп компараторов и являю,тся входом блока.

| Батушев В.А | |||

| и др | |||

| Микросхемы и их применение | |||

| Гребенчатая передача | 1916 |

|

SU1983A1 |

| Пылеочистительное устройство к трепальным машинам | 1923 |

|

SU196A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Шляндин В.М | |||

| Цифровые электроиз - мерительные приборы | |||

| - М.: Энергия, 197.2, с | |||

| РЕЛЬСОВАЯ ПЕДАЛЬ | 1920 |

|

SU290A1 |

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

Авторы

Даты

1989-08-07—Публикация

1987-04-03—Подача