11

Изобретение относится к импульсной технике и может быть использовано в различных пересчетньпс схемах. Цель изобретения - повышение быстродействия Т-триггера.

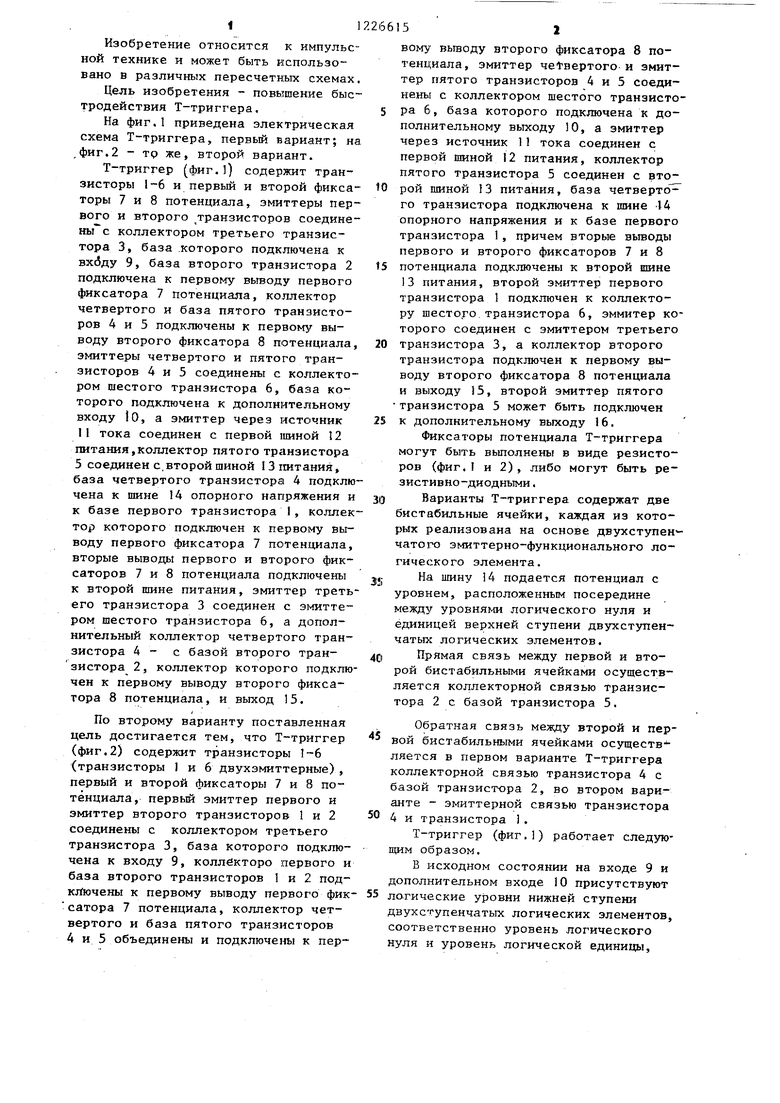

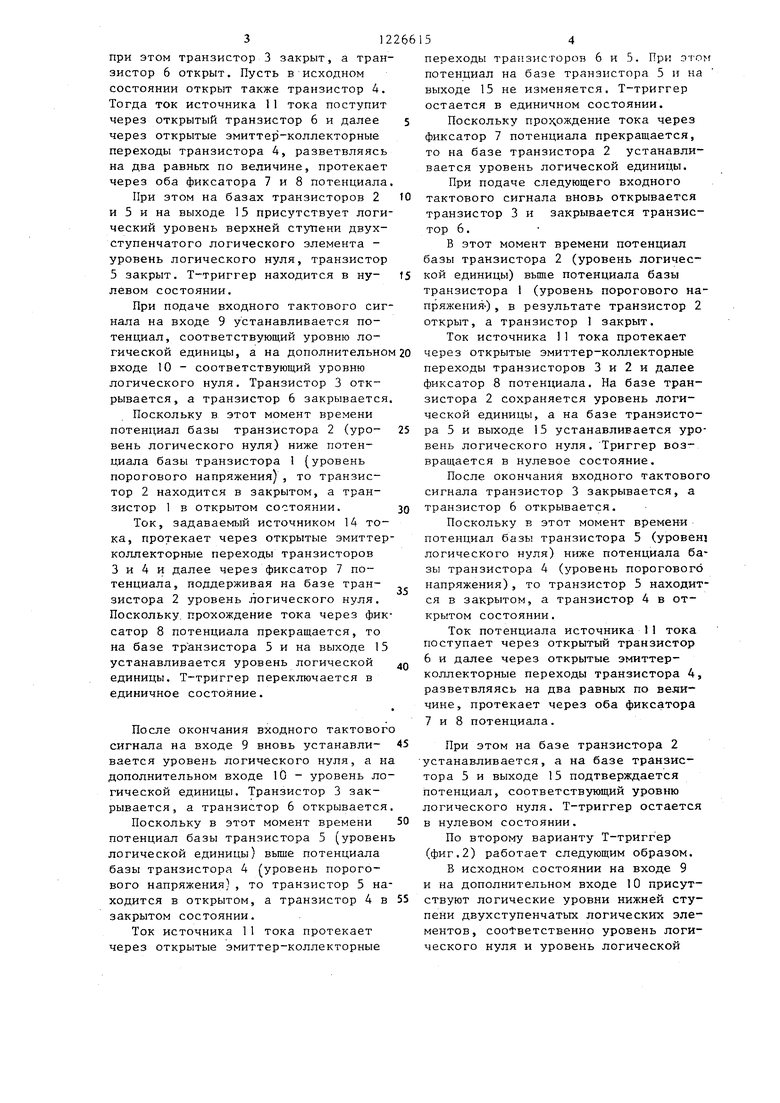

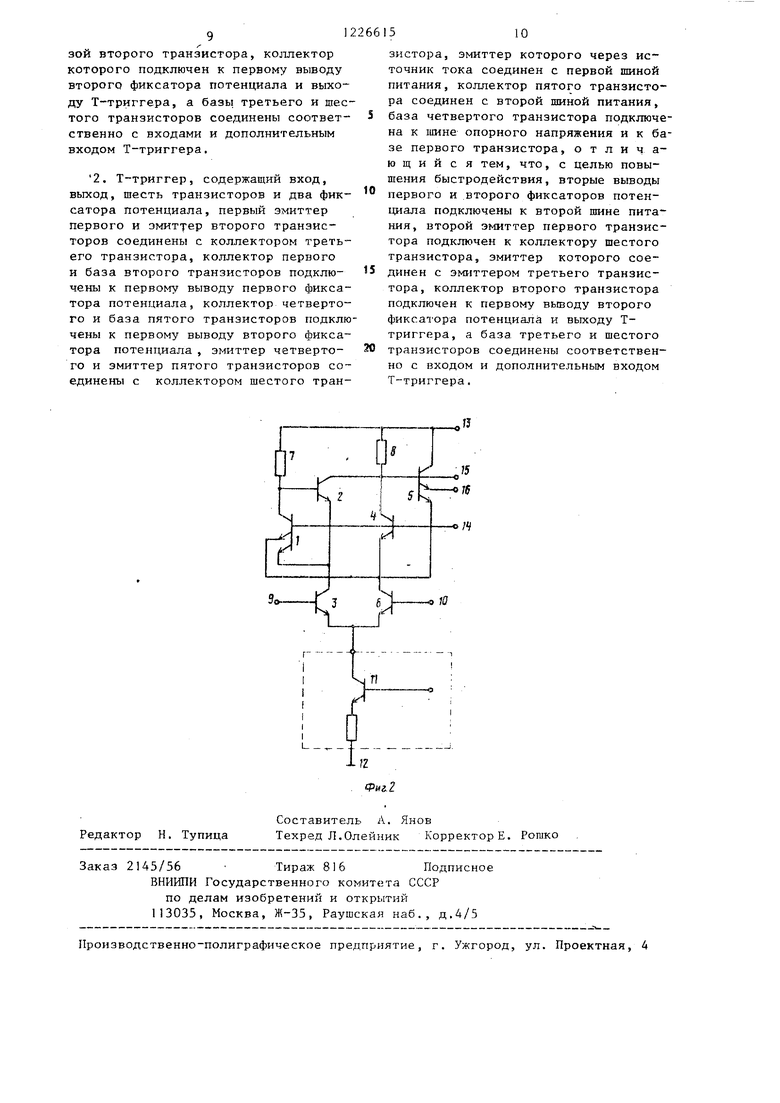

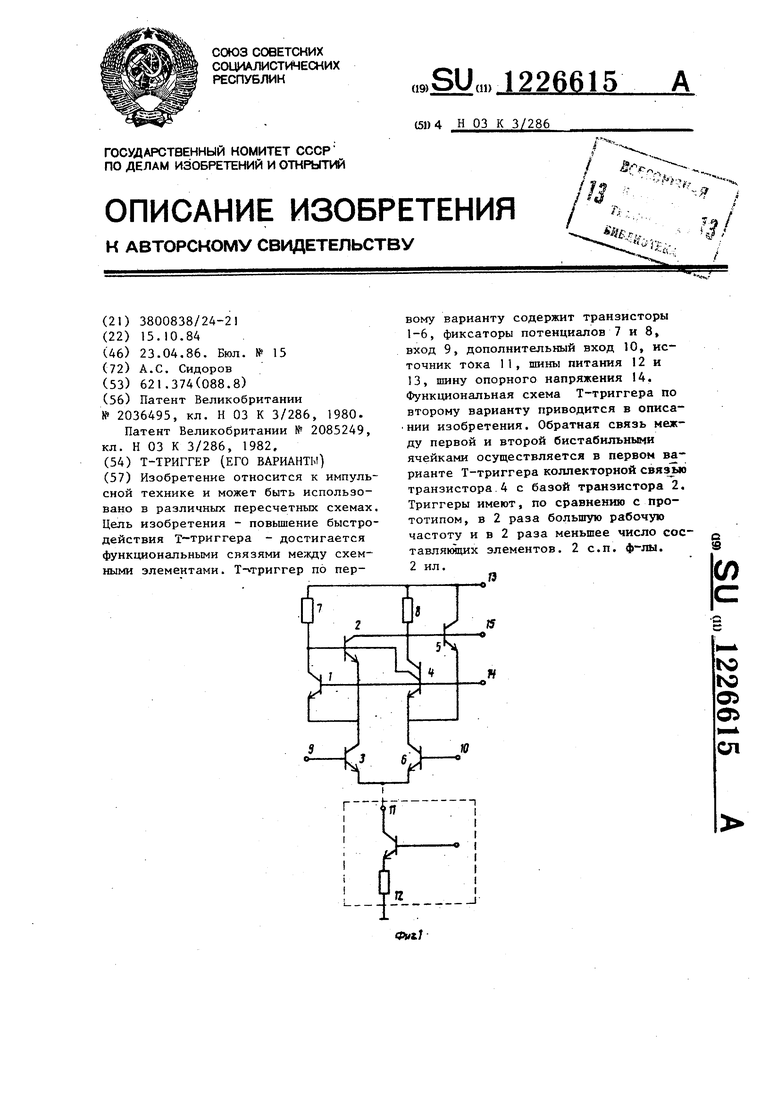

На фиг,1 приведена электрическая схема Т-триггера, первый вариант; на фиг.2 - тр же, второй вариант.

Т-триггер (фиг.)) содержит транзисторы 1-6 и первый и второй фиксаторы 7 и 8 потенциала, эмиттеры первого и второго транзисторов соединены с коллектором третьего транзистора 3, база которого подключена к вхбду 9, база второго транзистора 2 подключена к первому выводу первого фиксатора 7 потенциала, коллектор четвертого и база пятого транзисторов 4 и 5 подключены к первому выводу второго фиксатора 8 потенциала, эмиттеры четвертого и пятого транзисторов 4 и 5 соединены с коллектором шестого транзистора 6, база которого подключена к дополнительному входу 10, а эмиттер через источник 11 тока соединен с первой пшной I2 питания,коллектор пятого транзистора 5 соединен с.второй шиной 13 питания, база четвертого транзистора 4 подключена к шине 14 опорного напряжения и к базе первого транзистора I, коллектор которого подключен к первому выводу первого фиксатора 7 потенциала, вторые выводы первого и второго фиксаторов 7 и 8 потенциала подключены к второй шине питания, эмиттер третьего транзистора 3 соединен с Э1 датте- ром шестого транзистора 6, а дополнительный коллектор четвертого транзистора 4 - с базой второго тран- зистора 2, коллектор которого подключен к первому выводу второго фиксатора 8 потенциала, и выход 15.

По второму варианту поставленная цель достигается тем, что Т-триггер (фиг.2) содержит транзисторы 1-6 (транзисторы 1 и 6 двухэмиттерные), первый и второй фиксаторы 7 и 8 потенциала, первьш эмиттер первого и эмиттер второго транзисторов 1 и 2 соединены с коллектором третьего транзистора 3, база которого подключена к входу 9, коллбкторо первого и база второго транзисторов 1 и 2 подключены к первому выводу первого фик сатора 7 потенциала, коллектор четвертого и база пятого транзисторов 4 и 5 объединены и подключе1Ш к пер266152

вому выводу второго фиксатора 8 потенциала, эмиттер четвертого-и эмит тер пятого транзисторов 4 и 5 соединены с коллектором шестого транзисто5 ра 6, база которого подключена к дополнительному выходу 10, а эмиттер через источник 11 тока соединен с первой шиной 12 питания, коллектор пятого транзистора 5 соединен с вто10 рой шиной 13 питания, база четвертого транзистора подключена к шине 14 опорного напряжения и к базе первого транзистора 1, причем вторые вьгеоды первого и второго фиксаторов 7 и 8

15 потенциала подключены к второй шине 13 питания, второй эмиттер первого транзистора 1 подключен к коллектору шестого транзистора 6, эммитер которого соединен с эмиттером третьего

20 транзистора 3, а коллектор второго транзистора подключен к первому выводу второго фиксатора 8 потенциала и выходу 15, второй эмиттер пятого транзистора 5 может быть подключен

25 к дополнительному выходу 16.

Фиксаторы потенциала Т-триггера могут быть вьшолнены в виде резисторов (фиг.I и 2), либо могут быть ре- зистивно-диодными.

30 Варианты Т-триггера содержат две бистабильные ячейки, каждая из которых реализована на основе двухступен чатого эмиттерно-функционального логического элемента.

j,j На шину 14 подается потенциал с уровнем, расположенным посередине между уровнями логического нуля и единицей верхней ступени двухступенчатых логических элементов.

4(1) Прямая связь между первой и второй бистабильными ячейками осушеств- ляется коллекторной связью транзистора 2 с базой транзистора 5.

Обратная связь между второй и первой бистабильными ячейками осушеств- ляется в первом варианте Т-триггера коллекторной связью транзистора 4 с базой транзистора 2, во втором варианте - эмиттерной связью транзистора 4 и транзистора .

Т-триггер (фиг,1) работает следующим образом.

В исходном состоянии на входе 9 и дополнительном входе 10 присутствуют логические уровни нижней ступени

двухступенчатых логических элементов, соответственно уровень логического нуля и уровень логической единицы.

312

при этом транзистор 3 закрыт, а транзистор 6 открыт. Пусть в исходном состоянии открыт также транзистор 4. Тогда ток источника 11 тока поступит через открытый транзистор 6 и далее через открытые эмиттер-коллекторные переходы транзистора 4, разветвляясь на два равных по величине, протекает через оба фиксатора 7 и 8 потенциала.

При этом на базах транзисторов 2 и 5 и на выходе 15 присутствует логический уровень верхней ступени двухступенчатого логического элемента - уровень логического нуля, транзистор 5 закрыт. Т-триггер находится в ну- левом состоянии.

При подаче входного тактового сигнала на входе 9 устанавливается потенциал, соответствующий уровню логической единицы, а на дополнительном входе 10 - соответствующий уровню логического нуля. Транзистор 3 открывается, а транзистор 6 закрывается.

Поскольку в этот момент времени потенциал базы транзистора 2 (уро- вень логического нуля) ниже потенциала базы транзистора 1 {уровень порогового напряжения), то транзистор 2 находится в закрытом, а транзистор 1 в открытом состоянии.

Ток, задаваемый источником 14 тока, протекает через открытые эмиттер- коллекторные переходы транзисторов 3 и 4 и далее через фиксатор 7 потенциала, поддерживая на базе транзистора 2 уровень логического нуля. Поскольку, прохождение тока через фиксатор 8 потенциала прекращается, то на базе транзистора 5 и на выходе 15 устанавливается уровень логической единицы. Т-триггер переключается в единичное состояние.

После окончания входного тактового сигнала на входе 9 вновь устанавли- вается уровень логического нуля, а на дополнительном входе 10 - уровень логической единицы. Транзистор 3 закрывается, а транзистор 6 открывается.

Поскольку в этот момент времени потенциал базы транзистора 5 (уровень логической единицы) выше потенциала базы транзистора 4 (уровень порогового напряжения), то транзистор 5 находится в открытом, а транзистор 4 в закрытом состоянии.

Ток источника 11 тока протекает через открытые эмиттер-коллекторные

$

10 tS

20

25 0

о

5

0 5

5

54

переходы транзисторов 6 и 5. При этом потенциал на базе транзистора 5 и на выходе 15 не изменяется. Т-триггер остается в единичном состоянии.

Поскольку прохождение тока через фиксатор 7 потенциала прекращается, то на базе транзистора 2 устанавливается уровень логической единицы.

При подаче следующего входного тактового сигнала вновь открывается транзистор 3 и закрывается транзистор 6.

В этот момент времени потенциал базы транзистора 2 (уровень логической единицы) выше потенциала базы транзистора 1 (уровень порогового на- пряжения ) , в результате транзистор 2 открыт, а транзистор 1 закрыт.

Ток источника I1 тока протекает через открытые эмиттер-коллекторные переходы транзисторов 3 и 2 и далее фиксатор 8 потенциала. На базе транзистора 2 сохраняется уровень логической единицы, а на базе транзистора 5 и выходе 15 устанавливается уровень логического нуля. Триггер возвращается в нулевое состояние.

После окончания входного тактового сигнала транзистор 3 закрывается, а транзистор 6 открывается.

Поскольку в этот момент времени потенциал базы транзистора 5 (уровен логического нуля) ниже потенциала базы транзистора 4 (уровень порогового напряжения), то транзистор 5 находится в закрытом, а транзистор 4 в открытом состоянии.

Ток потенциала источника 11 тока поступает через открытый транзистор

6и далее через открытые эмиттер- коллекторные переходы транзистора 4, разветвляясь на два равных по величине, протекает через оба фиксатора

7и 8 потенциала.

При этом на базе транзистора 2 устанавливается, а на базе транзистора 5 и выходе 15 подтверждается потенциал, соответствующий уровню логического нуля. Т-триггер остается в нулевом состоянии.

По второму варианту Т-триггер (фиг.2) работает следующим образом.

В исходном состоянии на входе 9 и на дополнительном входе 10 присутствуют логические уровни нижней ступени двухступенчатых логических элементов, соответственно уровень логического нуля и уровень логической

единицы, при этом транзистор 3 закрыт , а транзистор 6 открыт.

Пусть в исходном состоянии открыт также и транзистор 4 и первый эмиттер-коллекторный переход транзистора 1. Тогда ток источника 11 тока поступает через открытый транзистор 6 и далее, разветвляясь на два равных по величине, протекает через транзистор 4 и фиксатор 8 потенциала, а также через первый эмиттерно-коллек- торный переход , транзистора 1 и фик сатор 7 потенциала.

При этом на базах транзистора 2 и 5 и на выходе 15 присутствует ло- гический уровень верхней ступени двухступенчатого логического элемента - уровень логического нуля, транзистор 5 закрыт. Т-триггер находится в нулевом состоянии.

При подаче входного тактового сигнала на входе 9 устанавливается потенциал, соответствующий уровню логической единицы, а на дополнительном входе 10 - потенциал, соответст- вующий уровню логического нуля.

Транзистор 3 открывается, а транзистор 6 закрывается.

Поскольку в этот момент времени потенциал базы транзистора 2 (уро- вень логического нуля) ниже потенци- asia базы транзистора 1 (уровень порогового напряжения), то транзистор 2 находится в закрытом, а транзистор I в открытом состоянии.

Ток источника 11 тока протекает через открытый транзистор 3 и открытый второй эмиттерно-коллекторный переход транзистора 1 и далее через фиксатор 7 потенциала, поддерживая на базе транзистора 2 уровень логического нуля. Поскольку прохождение тока через фиксатор 8 потенциала прекращается, то на базе транзистора 5 и выходе 15 устанавливается уро- вень логической единицы. Т-триггер переключается в единичное состояние.

После окончания входного тактовог с игнала на входе 9 вновь устанавливается уровень логического нуля, а на дополнительном входе 10 - уровень ло гаческой единицы. Транзистор 3 закрыт, а транзистор 6 открывается

Поскольку в этот момент времени потенциал базы транзистора 5 (уровен логической единицы) выше потенциала базы транзисторов 1 и 4 (уровень по- DoroBoro напряжения), то транзистор

5 находится в открытом, а транзистор

1и 4 в закрытом состоянии.

Ток источника тока протекает через открытые эмиттер-коллекторные переходы транзисторов 6 и 5. При это потенциал на базе транзистора 5 и на выходе 15 не изменится. Т-триггер остаетс я в единичном состоянии.

Поскольку прохождение тока через фиксатор 7 потенциала прекращается, то на базе транзистора 2 устанавливается уровень логической единицы.

При подаче следующего входного тактового сигнала вновь открывается транзистор 3 и закрывается транзистор 6.

В этот момент времени потенциал базы транзистора 2 (уровень логической единицы) выше потенциала базы транзистора 1 (уровень порогового напряжения), в результате транзистор

2открыт, а транзистор 1 закрыт.

Ток источника I1 тока протекает через эмиттер-коллекторные переходы транзисторов 3 и 2 и далее через фиксатор 8 потенциала. На базе транзистора 2 сохраняется уровень логической единицы, а на базе транзистора 5 и выходе 15 устанавливается уровень логического нуля. Т-триггер возвращается в нулевое состояние.

После окончания входного тактовог сигнала транзистор 3 закрывается, а транзистор 6 открывается.

Поскольку в этот момент времени потенциал базы транзистора 5 (уровен логического нуля) ниже потенциала базы транзистора 4 (уровень порогового напряжения), то транзистор 5 находится в закрытом, а транзистор 4 в открытом состоянии.

Ток источника 11 тока поступает через открытый транзистор 6 и далее, разветвляясь на два равных по величине, протекает через транзистор 4 и фиксатор 8 потенциала, а также через первый эмиттер-коллекторный переход транзистора 1 и фиксатор 7 потенциала .

При этом на базе транзистора 2 устанавливается, а на базе транзистора 5 и на выходе 15 подтверждается потенциал, соответствующий уровню логического нуля. Т-триггер остается в нулевом состоянии. Функциональное быстродействие Т-триггера определяет ся временем переключения двух биста- бильных ячеек.

712

Таким образом, максимальная рабочая частота триггера кс /2 Т(,р , где Тер - среднее время переключения одной бистабильной ячейки. При этом каждый вариант Т-триггера реализован на десяти элементах.

Исходя из особенности функционирования Т-триггера, заключающейся в том, что в момент времени между двумя входными тактовыми импульсами и при нулевом состоянии триггера ток источника тока одновременно протекает через оба фиксатора 7 и 8 потенциала, для достижения максимальных рабочих; частот должны вьшолнять- ся определенные соотношения между временем переключения бистабильных ячеек, скважностью входных тактовых импульсов, величиной нагрузки на выходную клемму устройства.

Например, для реализации предельного быстродействия во втором варианте Т-триггера, при соответствующем конструктивном исполнении и когда выходной сигнал снимается с до- полнительного выхода 16 устройства, когда у первой бистабильной ячейки время переключения из единичного состояния в нулевое в полтора раза больше, чем у второй, а время пере- ключения из нулевого состояния в единичное у обеих бистабильных ячеек одинаково, скважность входных тактовых импульсов должна быть равна-2,5.

Такая скважность входных тактовых импульсов может быть реализована, например, на входном дифференциаль- Hotf усилителе-формирователе со смещенным отсносительно постоянной составляющей входного синусоидального сигнала порогом срабатывания.

При работе Т-триггера в широком диапазоне входных тактовых частот от импульсного сигнала типа меандр, когда используются резисторные фик- саторы потенциала, возникает модуляция амплитуды выходного сигнала бистабильных ячеек.

В тех случаях, когда этот эффект нежелателен, возможно исключение мо- дуляции выходного сигнала Т-триггера путем подключения коллектора транзистора 2 к дополнительному выводу второго фиксатора потенциала, к средней точке фиксатора 8 потенциала. Для этой цели можно использовать исключение прохождения части коллекторного тока транзистора 2 через фиксатоо

8

8 потенциала путем подключения дополнительного второго коллектора транзистора 2 к второй шине 13 питания.

В первом варианте Т-триггера возможно исключение модуляции амплитуды выходного сигнала также и на выходе первой бистабильной ячейки. Для этог коллектор транзистора 1 должен быть подключен к дополнительному вьтоду первого фиксатора 7 потенциала (к средней точке фиксатора 7 потенциала) .

Преимуществом предлагаемого триггера по сравнению с известным является его более чем в два раза больша максимальная рабочая частота. Это обусловлено в полтора раза более высоким функциональным быстродействием предлагаемого триггера, в два раза меньшим числом составляющих элементов и соответственно более простой конструкцией, что значительно снижае время переключения каждой бистабильной ячейки и повышает быстродействие Т-триггера.

Ф о рмула изобретения

I. Т-триггер, содержащий вход, выход, шесть транзисторов и два фиксатора потенциала, эммитеры первого и второго, транзисторов соединены с коллектором третьего транзистора, база второго транзистора подключена к первому выводу первого фиксатора потенциала, коллектор четвертого транзистора соединен с базой пятого транзистора и подключен к первому выводу второго фиксатора потенциала, эмиттеры четвертого и пятого транзисторов соединены с колле:стором шестого транзистора, эмиттер которого через источник тока соединен с первой шиной питания, коллектор пятого транзистора соединен с второй шиной питания, база четвертого транзистора подключена к шине опорного напряжени и к базе первого транзистора, коллектор которого подключен к первому выводу первого фиксатора потенциала, отличающийся тем, что, с целью повышения быстродействия, вторые выводы первого и второго фиксаторов потенциала подключены к второй шине питания, эмиттер третьего транзистора соединен с эмиттером шестого транзистора, дополнительный коллектор четвертого транзистора - с ба912266

, ЗОЙ второго транзистора, коллектор

которого подключен к первому выводу второго фиксатора потенциала и выходу Т-триггера, а базы третьего и шестого транзисторов соединены соответ- ственно с входами и дополнительным входом Т-триггера.

2. Т-триггер, содержащий вход, выход, шесть транзисторов и два фиксатора потенциала, первый эмиттер первого и эмиттер второго транзисторов соединены с коллектором третьего транзистора, коллектор первого и база второго транзисторов подключены к первому выводу первого фиксатора потенциала, коллектор четвертого и база пятого транзисторов подключены к первому выводу второго фиксатора потенциала , эмиттер четвертого и эмиттер пятого транзисторов соединены с коллектором шестого тран15

10

зистора, эмиттер которого через источник тока соединен с первой шиной питания, коллектор пятого транзистора соединен с второй шиной питания, база четвертого транзистора подключена к шине опорного напряжения и к базе первого транзистора, отличающийся тем, что, с целью повышения быстродействия, вторые выводы первого и второго фиксаторов потен- 1щала подключены к второй шине питания, второй эмиттер первого транзистора подключен к коллектору шестого транзистора, эмиттер которого соединен с эмиттером третьего транзистора, коллектор второго транзистора подключен к первому выводу второго фиксатора потенциала и выходу Т- триггера, а база третьего и шестого транзисторов соединены соответственно с входом и дополнительным входом Т-триггера.

Редактор Н. Тупица

Составитель Л. Янов

Техред Л.Олейник Корректор Е. Рошко

Заказ 2145/56 Тираж 816 Подписное ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д,4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

| название | год | авторы | номер документа |

|---|---|---|---|

| Д-триггер | 1980 |

|

SU868982A1 |

| D-триггер | 1985 |

|

SU1332380A1 |

| Тактируемый @ -триггер @ -типа | 1985 |

|

SU1275738A1 |

| Тактируемый @ -триггер в интегральной инжекционной логике | 1982 |

|

SU1051692A1 |

| ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ЗАПИСИ ОПЕРАТИВНОГО ЗАПОМИНАЮЩЕГО УСТРОЙСТВА | 1994 |

|

RU2097843C1 |

| Синхронный д-триггер | 1977 |

|

SU660210A1 |

| Триггер | 1983 |

|

SU1150734A1 |

| Интегральный четырехзначный D-триггер | 1986 |

|

SU1338012A1 |

| Транзисторный инвертор | 1988 |

|

SU1818673A1 |

| НЕСИММЕТРИЧНЫЙ ТРИГГЕР | 2020 |

|

RU2743452C1 |

Изобретение относится к импульсной технике и может быть использовано в различных пересчетных схемах. Цель изобретения - повышение быстродействия Т триггера - достигается функциональными связями между схемными элементами. Т- триггер по первому варианту содержит транзисторы 1-6, фиксаторы потенциалов 7 и 8, вход 9, дополнительный вход 10, источник тока 11, шины питания 12 и 13, шину опорного напряжения 14. Функциональная схема Т-триггера по второму варианту приводится в описании изобретения. Обратная связь между первой и второй бистабильныни ячейками осуществляется в первом варианте Т-триггера коллекторной связью транзистора.4 с базой транзистора 2. Триггеры имеют, по сравнению с прототипом, в 2 раза большую рабочую частоту и в 2 раза меньшее число сос- тавлякйцих элементов. 2 с.п. ф-лы. 2 ил. /3 i СЛ to ю 05 О ел

| ОПТИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2036495C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| ЦЕНТРОБЕЖНЫЙ ЭКСТРАКТОР | 1995 |

|

RU2085249C1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-04-23—Публикация

1984-10-15—Подача