го транзистора, коллектор которого соединен с базами второго и третьего транзисторов и через нервый резистор - с шиной питания, коллекторы транзисторов второго переключателя тока соединены с эмиттерами четвертого транзистора, коллектор которого соединен с базами пятого и шестого транзисторов и через второй резистор - с шиной питания, эмиттеры второго, третьего, пятого и шестого транзисторов соединены соответственно с коллекторами входного транзистора нервого переключателя тока, входного и опорного транзисторов второго переключателя тока и первой выходной клеммой, а коллекторы - с шиной питания, базы первого и четвертого транзисторов подключены ко второму источнику опорного напрял ения, а коллектор опорного транзистора первого переключателя тока - ко второй входной клемме, введены два дополнительных транзистора, базы которых подключены к третьей входной клемме, коллекторы - к коллекторам, а эмиттеры- к эмиттерам входных транзисторов первого и второго переключателей тока соответственно, кроме того, в него введен седьмой транзистор, коллектор которого соединен с шиной питания, эмиттер - со второй выходной клеммой, а база - с коллектором пятого транзистора и через резистор - с шиной питания.

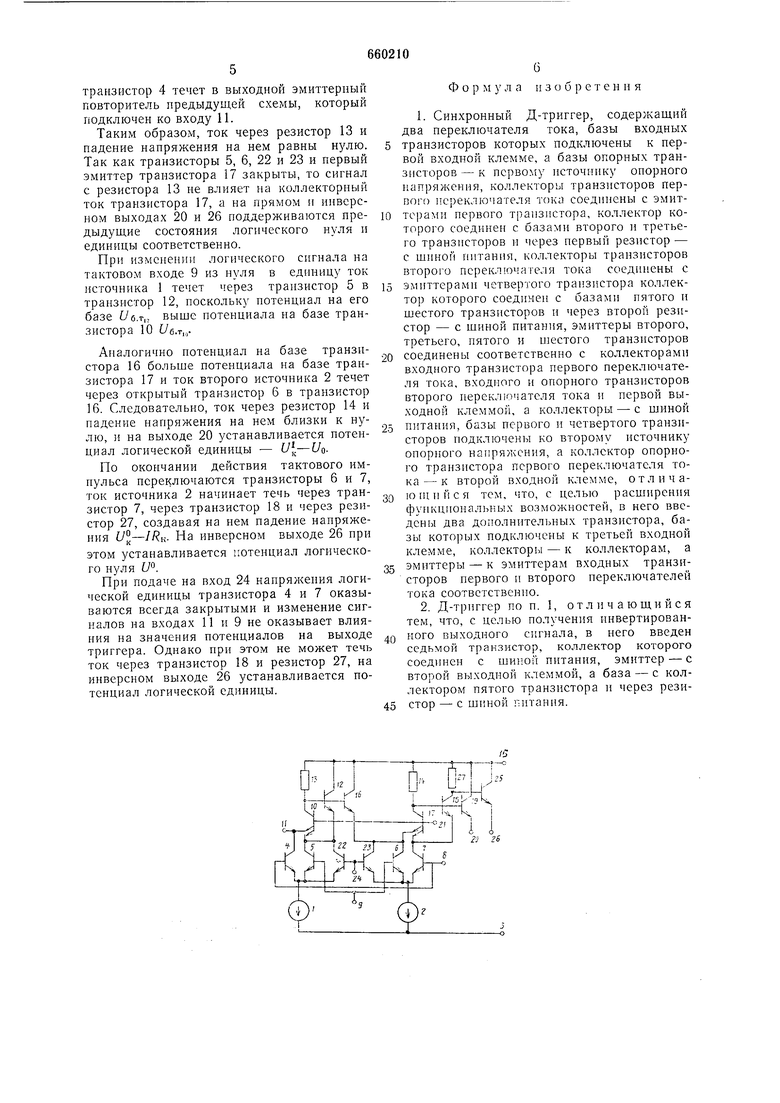

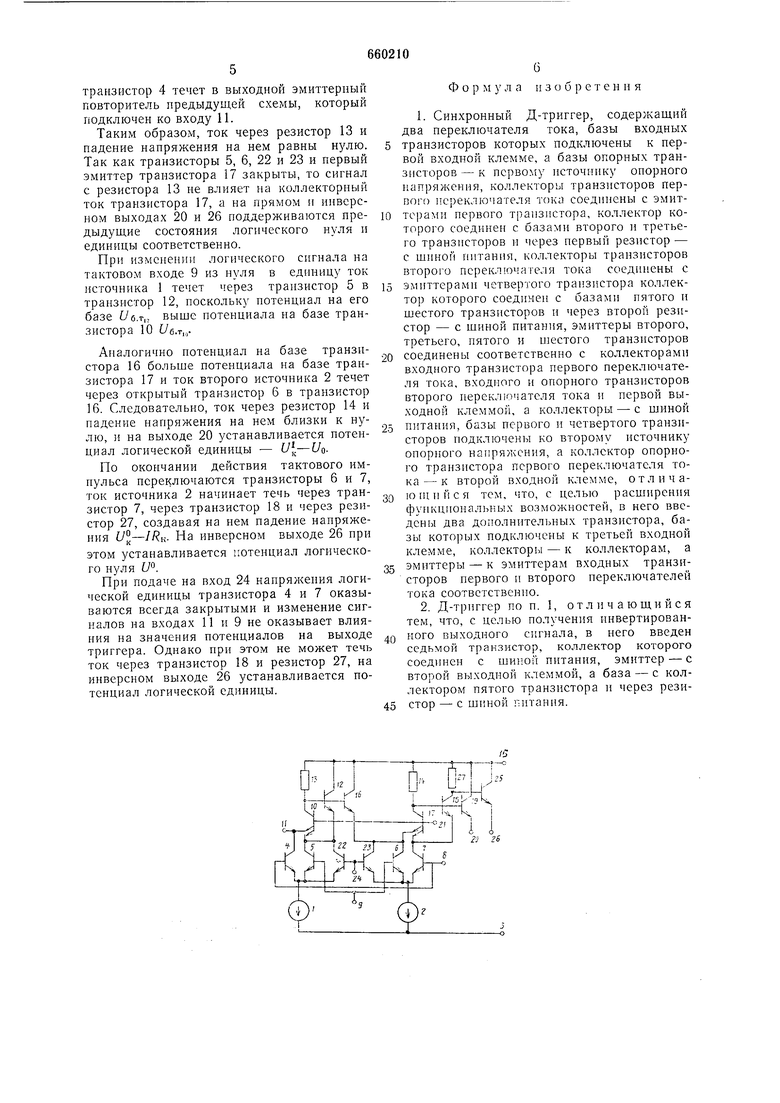

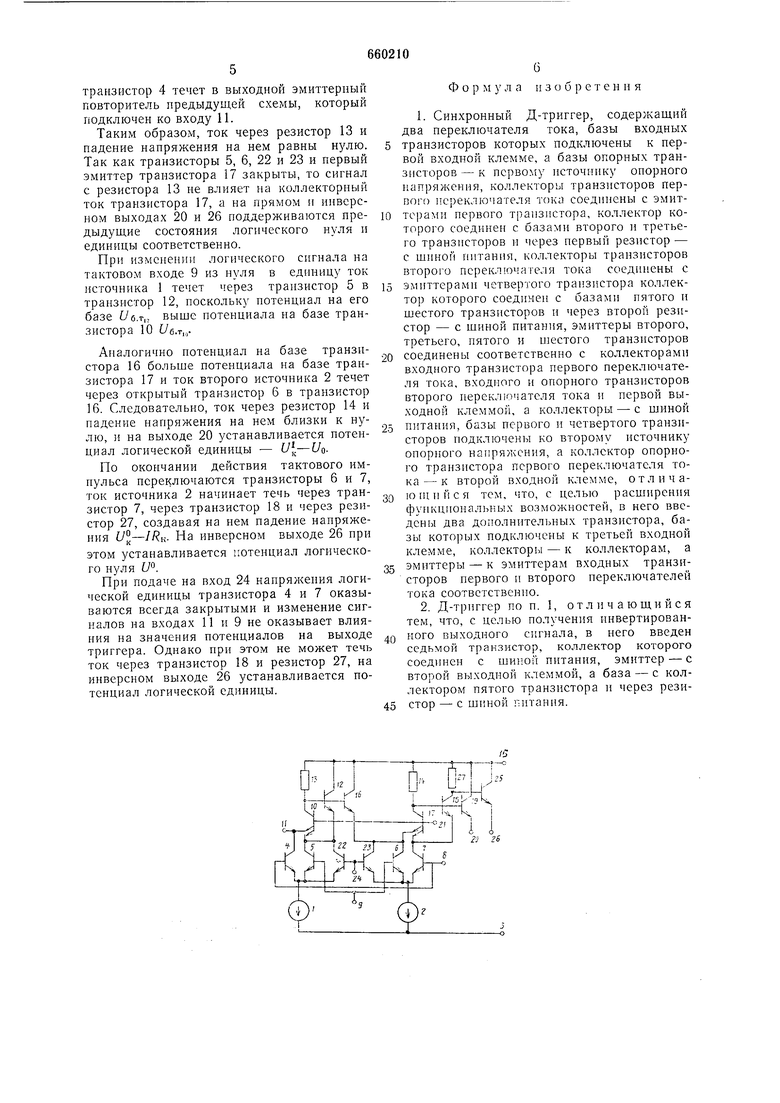

На чертеже представлена схема предлагаемого синхронного Д-триггера.

В Д-триггере источники 1, 2 тока включены между первой шиной питания 3 и эмиттерами транзисторов 4-7, базы транзисторов 4 и 7 подключены к первой клемме 8 опорного напряжения, базы транзисторов 5 и 6 подключена к первому входу 9, а коллектор транзистора 4, объединенный с первым эмиттером транзистора 10, подключен ко второму входу 11, второй эмиттер транзистора 10 соединен с коллектором транзистора 5 и эмиттером транзистора 12, резисторы 13 и 14 подключены следующим образом: резистор 13 включен между второй шиной питания 15 и объединенными коллектором транзистора 10 и базами транзисторов 12 и 16, а резистор 14 - между шиной 15, коллектором транзнстора 17 и базами транзисторов 18 и 19, эмиттер транзистора 18 подключен к первому эмиттеру транзистора 17 и коллектору транзистора 7, эмиттер транзистора 19 подключен к прямому выходу 20, а эмиттер транзистора 16 соединен со вторым эмиттером транзистора 17 и коллектором транзистора 6, причем коллекторы транзисторов 12, 16 и 19 подключены к шине питания 15, а базы транзисторов 10 и 7 - ко второй клемме опорного напряжения 21, коллектор транзистора 22 соединен с коллектором транзистора 5, коллектор транзистора 23- с коллектором транзистора 6, эмиттер транзистора 22 соединен с эмиттером транзистора 5 и эмиттер транзистора 23 - с эмиттером транзистора 6, базы транзисторов 22 и 23 подключены к третьему входу 24, эмиттер, коллектор и база транзистора 25 5 подключены соответственно к инверсному выходу 26, шине 15 и коллектору транзистора 18, причем между последними включен резистор 27. Устройство работает следующим обра0 зом.

Пусть в начальном состоянии на тактов 51Й вход 9 и логические входы 11 и 24 подан потенциал логического нуля Lf, меньП1ПЙ, чем величина напряжения источника 8

5 опорного напрял ения

Я„п, (U° -f U}/2,

причем величина напряжения источника опорного напряжения 21 равна

0fon,. + o,

где Uo - падение напряжения на открытом эмиттерном переходе транзистора. Тогда транзисторы 5, 6, 22 и 23 закрыты, и ток первого источника тока протекает через открытый транзистор 4 и первый эмиттер транзистора 10 в первый резистор 13, создавая на нем падение напряжения

UI - - //.,

где /-величина тока источников 1 и 2; RK-сопротивление резисторов 13, 14

и 27.

Когда потенциал на тактовом входе 9 изменяется из

, в U.-U,,

то переключаются транзисторы 4 и 5 и ток источника 1 через транзистор 5 начинает течь в транзистор 10, так как напряжение на его базе больше, чем на базе транзистора 12.

В результате на резисторе 13 сохраняется потенциал У. Тогда ток второго источника 2 протекает через транзистор 6 и первый эмиттер транзистора 17 во второй резистор 14, создавая на нем падение напряжения f/. На выходе триггера 20 устанавливается потенциал логического нуля 11°. Но окончании действия тактового импульса переключаются транзисторы 6 и 7. Ток источника 2 начинает течь через транзистор 7 в транзистор 17, в резистор 14, так как напряжение на его базе больше, чем напряжение на базе транзистора 18.

На выходе 20 схемы при этом сохраняется потенциал логического нуля U. Из-за этого коллекторный ток транзистора 18 и напряжение на резисторе 27 близко к нулю б 0 и на выходе 26 устанавливается потенциал логической единицы .

Пусть теперь на вход 11 подан потенциал логический единицы. При нулевом состоянии тактового входа 9, эмиттеры транзистора 10 закрыты, и ток источника 1 через

| название | год | авторы | номер документа |

|---|---|---|---|

| Переключатель тока | 1980 |

|

SU928648A1 |

| Д-триггер | 1980 |

|

SU868982A1 |

| Пороговое устройство Ларионова | 1985 |

|

SU1401435A1 |

| Т-триггер (его варианты) | 1984 |

|

SU1226615A1 |

| Пороговый логический элемент | 1975 |

|

SU600711A1 |

| Многопороговый логический элемент четности | 1980 |

|

SU928653A1 |

| Усилитель записи - считывания | 1989 |

|

SU1674250A1 |

| Мультиплексор | 1986 |

|

SU1378048A1 |

| D-триггер | 1985 |

|

SU1332380A1 |

| Аналого-цифровой преобразователь | 1985 |

|

SU1350831A1 |

Авторы

Даты

1979-04-30—Публикация

1977-03-05—Подача