(54) О-ТРИГГЕР

| название | год | авторы | номер документа |

|---|---|---|---|

| Т-триггер (его варианты) | 1984 |

|

SU1226615A1 |

| D-триггер | 1985 |

|

SU1332380A1 |

| Синхронный д-триггер | 1977 |

|

SU660210A1 |

| Д-триггер | 1982 |

|

SU1027802A1 |

| Преобразователь уровня сигналов | 1981 |

|

SU1011025A1 |

| Фронтальный D-триггер | 1979 |

|

SU896758A1 |

| СХЕМА ЗАЩИТЫ КЛЮЧЕВОГО ТРАНЗИСТОРА | 2003 |

|

RU2245602C1 |

| СВЕРХБЫСТРОДЕЙСТВУЮЩЕЕ СВЕРХИНТЕГРИРОВАННОЕ БИМОП ОЗУ НА ЛАВИННЫХ ТРАНЗИСТОРАХ | 1999 |

|

RU2200351C2 |

| Троичный счетный триггер | 1979 |

|

SU864503A1 |

| Тактируемый д-триггер | 1979 |

|

SU794723A1 |

Изобретение относится к импульсной технике.

Известен тактируемый О-триггер, состоящий из управляющего вентиля, переключателя тока с тактовым входом, источника постоянного тока и источника опорных напряжений l.

Недостатком известного триггера является низкая надежность из-за большой сложности.

Известен также триггер, содержащий бистабильный элемент на двух транзисторах, эмиттеры которых соединены между собой, а коллекторы через резисторы соединены с источником питания, управляющий транзистор, коллектор которого соединен с коллекторром одного из транзисторов бистабильного элемента, база соединена с источнике входных импульсов, а эмиттер соединен со вторым эмиттером второго транзистора бистабильного элемента, переключатель тока на двух транзисторах, коллекторы которых соединены соответственно с эмиттерами транзисторов бистабильного элемента и управляющего транзистора, баоы подключены к генераторс1М тактовых импульсов, а эмиттеры соединены с источником постоянного токаСз.

Недостатком известного устройства является низкая помехоустойчивость из-за малой величины перепада логие ческих уровней.

Цель изобретения - увеличение помехоустойчивости триггера.

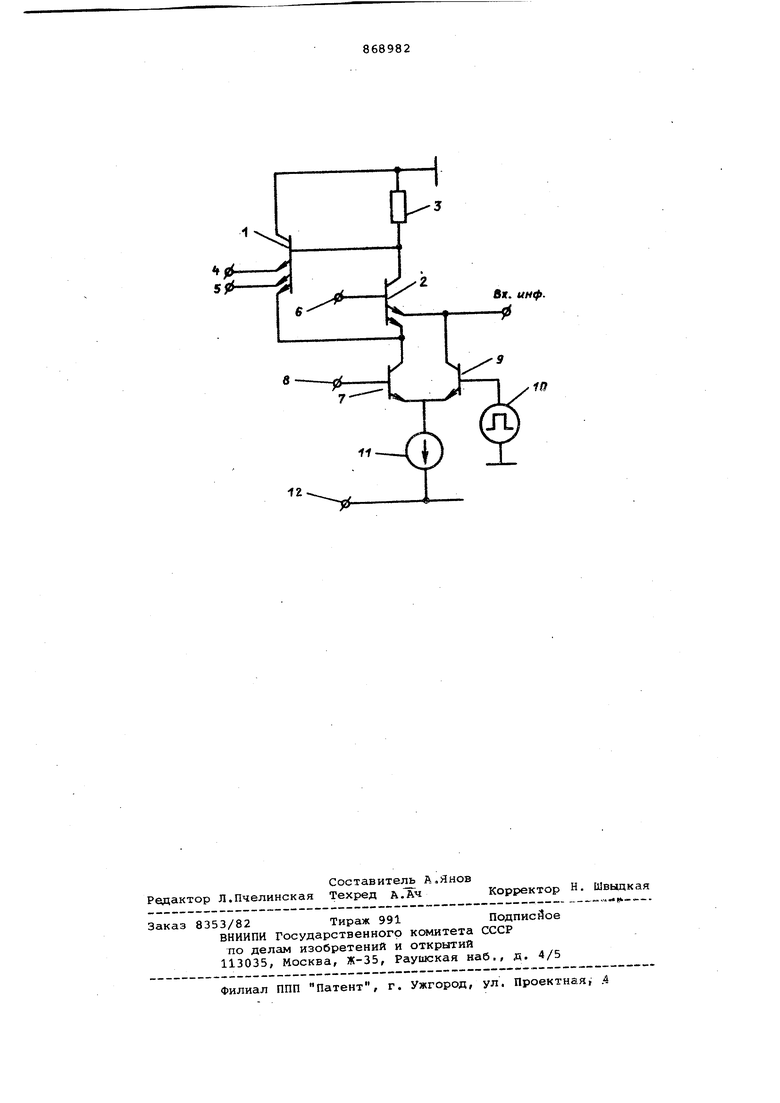

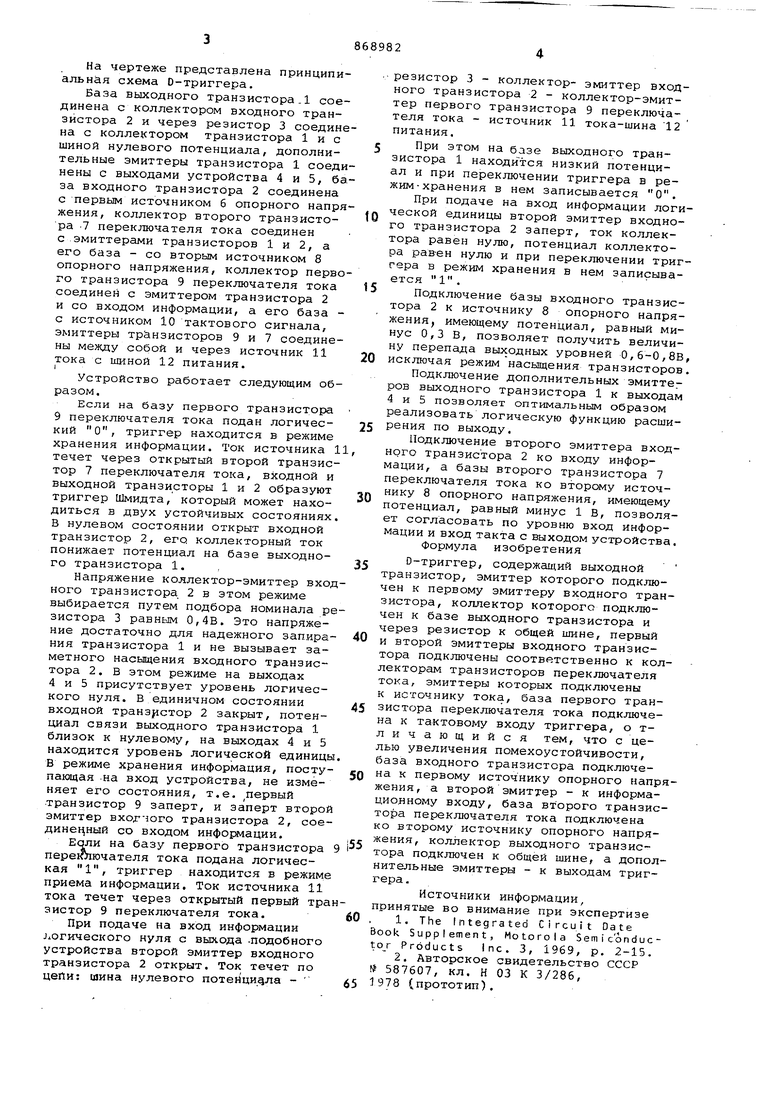

Для достижения поставленной цели в D-триггере, содержащем выходной

10 транзистор, эмиттер которого подключен к первому эмиттеру входного транзистора, коллектор которого подключен к базе выходного транзистора и через резистор к общей шине, первый

15 и второй эмиттеры входного транзистора подключены соответственно к коллекторам транзисторов переключателя тока, эмиттеры которых подключены к , источнику тока, база первого транзис20тора переключателя тока подключена к тактовому входу триггера, база входного транзистора подключена к первому источнику опорного напряжения, а второй эмиттер - к информационному

25 входу, база второго транзистора переключателя тока подключена ко второму источнику опорного напряжения, ко.плектор выходного транзистора подключен к общей шине, а дополнительные эмит30теры - к выходам триггера. На чертеже представлена принципиальная схема 0-триггера. База выходного транзистора 1 соединена с коллектором входного транзистора 2 и через резистор 3 соедине на с коллектором транзистора 1 и с шиной нулевого потенциала, дополнительные эмиттеры транзистора 1 соеди нены с выходами устройства 4 и 5, ба за входного транзистора 2 соединена с первым источником б опорного напря жения, коллектор второго транзистора -7 переключателя тока соединен с эмиттерами транзисторов 1 и 2, а его база - со вторым источником 8 опорного напряжения, коллектор перво го транзистора 9 переключателя тока соединен с эмиттером транзистора 2 и со входом информации, а его база с источником 10 тактового сигнала, эмиттеры транзисторов 9 и 7 соединены между собой и через источник 11 тока с шиной 12 питания, Устройство работает следующим образом. Если на базу первого транзистора 9 переключателя тока подан логический О, триггер находится в режиме хранения информации. Ток источника течет через открытый второй транзистор 7 переключателя тока, входной и выходной транзисторы 1 и 2 образуют триггер Шмидта, который может находиться в двух устойчивых состояниях в нулевом состоянии открыт входной транзистор 2, его коллекторный ток понижает потенциал на базе выходного транзистора 1. Напряжение коллектор-эмиттер вход ного транзистора, 2 в этом режиме выбирается путем подбора номинала р зистора 3 равным 0,4В, Это напряжение достаточно для надежного запира ния транзистора 1 и не вызывает заметного насыщения входного транзистора 2. В этом режиме на выходах 4 и 5 присутствует уровень логического нуля. В единичном состоянии входной транзистор 2 закрыт, потенциал связи выходного транзистора 1 близок к нулевому, на выходах 4 и 5 находится уровень логической единиц В режиме хранения информация, посту пающая .на вход устройства, не изменяет его состояния, т.е. первый транзистор 9 заперт, и заперт второ эмиттер вхогчого транзистора 2, сое динецный со входом информации, Еоли на базу первого транзистора перею ючателя тока подана логическая 1, триггер находится в режим приема информации. Ток источника 11 тока течет через открытый первый тр зистор 9 переключателя тока. При подаче на вход информации Jлoгичecкoгo нуля с выхода -подобного устройства второй эмиттер входного транзистора 2 открыт. Ток течет по цепи: шина нулевого потейци ла резистор 3 - коллектор- эмиттер входного транзистора 2 - коллектор-эмиттер первого транзистора 9 переключателя тока - источник 11 тока-шина 12 питания. При этом на базе выходного транзистора 1 находится низкий потенциал и при переключении триггера в режим-хранения в нем записывается О, При подаче на вход информации логической единицы второй эмиттер входного транзистора 2 заперт, ток коллектора равен нулю, потенциал коллектора рав-ен нулю и при переключении триггера в режим хранения в нем записывается 1. Подключение базы входного транзистора 2 к источнику 8 опорного напряжения, имеющему потенциал, равный минус 0,3 В, позволяет получить величину перепада выходных уровней О,6-0,8В, исключая режим насыщения транзисторов. Подключение дополнительных эмитте,ров выходного транзистора 1 к выходам 4 и 5 позволяет оптимальным образом реализовать логическую функцию расширения по выходу. Подключение второго эмиттера входного транзистора 2 ко входу информации, а базы второго транзистора 7 переключателя тока ко второму источнику 8 опорного напряжения, имеющему потенциал, равный минус 1 В, позволяет согласовать по уровню вход информации и вход такта с выходом устройства. Формула изобретения D-триггер, содержащий выходной транзистор, эмиттер которого подключен к первому эмиттеру входного транзистора, коллектор которого подключен к базе выходного транзистора и через резистор к общей шине, первый и второй эмиттеры входного транзистора подключены соответственно к коллекторам транзисторов переключателя тока, эмиттеры которых подключены к источнику тока, база первого транзистора переключателя тока подключена к тактовому входу триггера, о тличающийся тем, что с целью увеличения помехоустойчивости, база входного транзистора подключена к первому источнику опорного напряжения, а второй эмиттер - к информационному входу, база второго транзистора переключателя тока подключена ко второму источнику опорного напряжения, коллектор выходного транзистора подключен к общей шине, а дополнительные эмиттеры - к выходам триггера , Источники информации, принятые во внимание при экспертизе 1.The Integrated Circuit Date Book Supplement, Motorola Semiconducto r Products Inc. 3, 1969, p. 2-15. 2.Авторское свидетельство СССР 587607, кл. Н 03 К 3/286, 1978 (прототип).

Авторы

Даты

1981-09-30—Публикация

1980-01-04—Подача