цы (i 1,..., j 1,,..,+i m - разрядность операндов), выходы разрядов суммы четвертого сумматора модуля умножения i-й строки , j-ro столбца матрицы соединены с входами первой группы первого сумматора модуля умножения (1+1)-й строки j-ro столбца матрицы, отличающееся тем, что, с целью сокращения количества оборудования, модуль умножения содержит четыре узла анализа, два элемента НЕ, причем разряды выхода i-й тетрады регистра множителя соединены соответственно с первыми входами первого, второго, третьего и четвертого узлов анализа модулей умножения i-й строки матрицы, вход управления коррекцие устройства соединен с вторыми входами первого, второго, третьего и четвертого узлов анализа каждого модуля умножения матрицы, разряды с весом 8, 4, 2, 1 выхода j-й тетрада регистра множимого соединены соответственно с третьим четвертым, пятым и шестым входами первого узла анализа модуля умножения строки (i+j-1)-ro столбца матрицы и соответственно с шестыми входами ВТОРОГО , третьего и четвертого узлов анализа модуля умножения i-й строки (i+j)-ro столца матрицы, выход переноса первого сумматора модуля умножения j-ro столбца i-й строки соединен с восьмым входом четвертого узла анализа модуля умножения (i-1)-й строки j-ro столбца матрицы, выход переноса четвертого сумматора модуля умножения i-й строки j-ro столбца матрицы соединен с седьмым входом первого узла анализа модуля умножения (1+1)-й строки (j-l)-ro столца матрихцл, выходы третьего и пято. го элементов И модуля умножения i-й строки j-ro столбца матрицы соединены соответственно с первыми входами шестого и десятого злементов ИЛИ модуля умножения i-й строки (j+l)-ro столбца матрицы, в каждом модуле умножения третий

вход первого узла анализа соединен с вторыми входами первого, второго и третьего элементов И, третьи входы которых соединены соответственно с первыми входами второго, третьего и четвертого узлов анализа, четвертый вход первого

200282

узла анализа с третьим входом второго узла анализа, вторыми входами четвертого, пятого, . и шестого элементов И, третьи входы пятого и шестого элементов И соединены с вторым входом седьмого элемента И и с первым входом четвертого узла анализа, пятый вход первого узла анализа соединен с четвертым входом второго узла анализа, третьим входом третьего узла анализа и четвертым входом пятого элемента И, шестой вход первого узла анализа соедине:н с пятым входом второго узла анализа, четвертым входом третьего узла анализа и третьим входом четвертого узла анализа, четвертый вход которого соединен с шестым входом второго узла анализа, пятым входом третьего узла анализа, шестой вход третьего узла анализа соединен с пятым входом четвертого узла анализа, седьмые входы второго, третьего и четвертого узлов анализа соединены соответственно с вьпсодами переноса :первого, второго и третьего сумматоров, первые входы первого, вто- ,рого и третьего элементов ИЛИ соединены с соответствующими выходами пер вого узла ангшиза, четвертый выход которого соединен с вторыми входами первого и второго элементов ИЛИ, третий вход второго элемента ШЩ соединен с выходом первого элемента И и вторым входом третьего элемента ИЛИ, третий вход которого соединен с четвертым входом второго элемента РШИ и с пятым выходом первого узла анализа, шестой выход которого соединен с входом с весом 1 второй группы первого сумматора, выход переноса второго сумматора соединен с восьмым входом первого узла анализа, первые входы четвертого, пятого и второй вход шестого элементов JUM соединены соответственно с первьм, вторым и третьим выходами второго узла анализа, четвертый выход которого подключен к второму входу пятого злемента ИЛИ и второму входу четвертого элемента ИЛИ, третий вход которого соединен с выходом второго элемента И и третьим входом пятого элемента ШШ, четвертый вход которого подключен к третьему входу шестого элемента ИЛИ и пятому выходу второго узла анализа, выход которого подключен к входу с весом 1 второй группы второ сумматора, выход переноса третьего сумматора соединен с восьмым входом второго узла анализа, первые входы седьмого, восьмого и девятого элементов ИЛИ подключены соответственно к первому, второму и третьему, выходам третьего узла анализа, четвертьй выход которого соединен с вторыми входами седьмого и восьмого элементов ИЛИ, третьи входы которых подключены к выходу шестого- элемента И, четверт вход которого подключен к выходу первого элемента НЕ, вход которого подключен к третьему входу седьмого элемента И и пятому входу перво узла анализа, нетвертый вход которого соединен через второй элемент НЕ с четвертым входом седьмого элемента И, выход которого подключен к четвертому входу восьмого элемента ИЖ и второму входу девятого элемента ИЛИ, третий вход которого соединен с пятым выходом третьего узла анализа и пятым входом восьмого элемента ИЛИ, шестой вход которого подключен к выходу третьего элемента И, выход переноса четвертого сумматора соединен с восьмым входом третьего узла анализа, шестой выход которого соединен с вторым входом десятого элемента ИЛИ, первый, второй и третий выходы четвертого узла анализа сое динены соответственно с первыми входами одиннадцатого, двенадцатог и тринадцатого элементов ИЛИ, первый вход третьего узла анализа соединен с третьим входом четверто го элемента И, выход которого соед нен с вторым входом тринадцатого элемента ШИ и вторым входом две82надцатого элемента ИЛИ, третий вход которого соединен с вторым входом одиннадцатого элемента ИЛИ и четвертым выходом четвертого узла анализа, пятый выход которого -подключен к четвертому входу двенадцатого элемента ИЛИ и третьему входу тринадцатого элемента ИЛИ, шестой выход четвертого узла анализа соединен с входом с весом 1 второй группы четвертого сумматора, четвертый вход седьмого элемента ИЛИ соединен с выходом пятого элемента И. 2. Устройство по п. 1, о т л ичающееся тем, что узел анализа содержит шесть элементов И, I элемент сложения по модулю два и триггер, причем первый вход узла аналиэа соединен с первыми входами первого, второго, третьего и четвертого элементов И, вторые входы которых подключены соответственно к третьему, четвертому, пятому и шестому входам узла аналиэа, второй вход которого подключен к входу приема триггера, первому входу пятого элемента И и первому входу шестого элемента И, второй вход которого соединен с выходом элемента сложения по модулю два, первый вход которого подключен к седьмому входу узла анализа и второму входу пятого элемента И, третий вход которого соединен.с вторым входом элемента сложения по модулю два и выходом триггера, информационный вход которого подключен к восьмому входу узла аналиэа, первый, второй, -третий, четверт1й, пятый и шестой выходы узла анализа соединены соответственно с выходами первого, второго, третьего, пятого, шестого и четвертого элементов И.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для умножения | 1988 |

|

SU1578711A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Операционный модуль | 1984 |

|

SU1406592A1 |

| Матричное устройство для умножения | 1985 |

|

SU1267408A1 |

| СПОСОБ И УСТРОЙСТВО УМНОЖЕНИЯ ДВОИЧНО-ДЕСЯТИЧНЫХ КОДОВ | 2008 |

|

RU2386998C1 |

| Устройство для умножения двоично-десятичных цифр | 1983 |

|

SU1198513A1 |

| Последовательный двоично-десятичный сумматор-вычитатель | 1978 |

|

SU734685A1 |

| Устройство для умножения | 1985 |

|

SU1262481A1 |

| УСТРОЙСТВО для УМНОЖЕНИЯ ДЕСЯТИЧНЫХ ЧИСЕЛ | 1973 |

|

SU390525A1 |

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

1. МАТРИЧНОЕ УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ДВОИЧНЫХ И ДЕСЯТИЧНЫХ ЧИСЕЛ, содержащее регистр множимого, регистр множителя, регистр результата, коммутатор, узел формирования десятичного результата и матри- . цу модулей умножения, каждый модуль умножения содержит четыре сумматора, тринадцать элементов ИЛИ, семь элементов И, причем выходы разрядов суммы первого сумматора соединены с входами первой группы второго сумматора, выходы разрядов .суммы которого соединены с входами первой группы третьего сумматора, выходы разрядов суммы которого соединены с входами первой группы четвертого сумматора, выходы первого, второго и третьего элементов ИЛИ соединены соответственно с входами с весом 8, 4, 2, 1 второй группы первого сумматора, выходы четвертого, пятого и шестого элементов ИЛИ соединены соответственно с входами с весом 8, 4, 2 второй группы второго сумматора, выходы седьмого, восьмого, девятого и десятого элементов ИЛИ соединены с входами второй группы третьего сумматора, выходы одиннадцатого, двенадцатого и тринадцатого элементов ИЛИ соединены соответственно с входами с весом 8, 4, 2 второй группы четвертого сумматора, вход управления приемом операндов устройства соединен с тактовыми входами регистров множимого и множителя, выходы разрядов суммы четвертых сумматоров модулей умножения последней строки матрицы соединены с первой группой информационных входов коммутатора и с первой группой входов узла формирования десяа S тичного результата, выход которого соединен с второй группой информа(Л ционных входов коммутатора, выход которого соединен с информационным входом регистра результата, выход которого-соединен с второй группой входов узла формирования десятичного результата, вход управления NP приемом результата устройства соедиО нен с входом сброса регистра мноо жителя и управляющим входом регистра 00 результата, вход управления коррекцией устройства соединен с управляю щим входом коммутатора, вход задания режима устройства соединен с первыми входами первого, второго, третьего, четвертого, пятого, шестого, седьмого элементов И каждого модуля умножения матрицы, выходы переноса первого, второго, третьего и четвертого сумматоров модуля умножения j-ro столбца i-й строки матрицы соединены соответственно с входами переносов соответствующих сумматоров модулей умножения (j+1)-ro столбца i-й строки матрк

Изобретение относится к вычислительной технике, предназначено для умножения двоичных и десятичных чисел, представленных кодом 8-4-2-1 и может быть использовано в быстродействующих вычислителях.

Цель изобретения - сокращение количества оборудования.

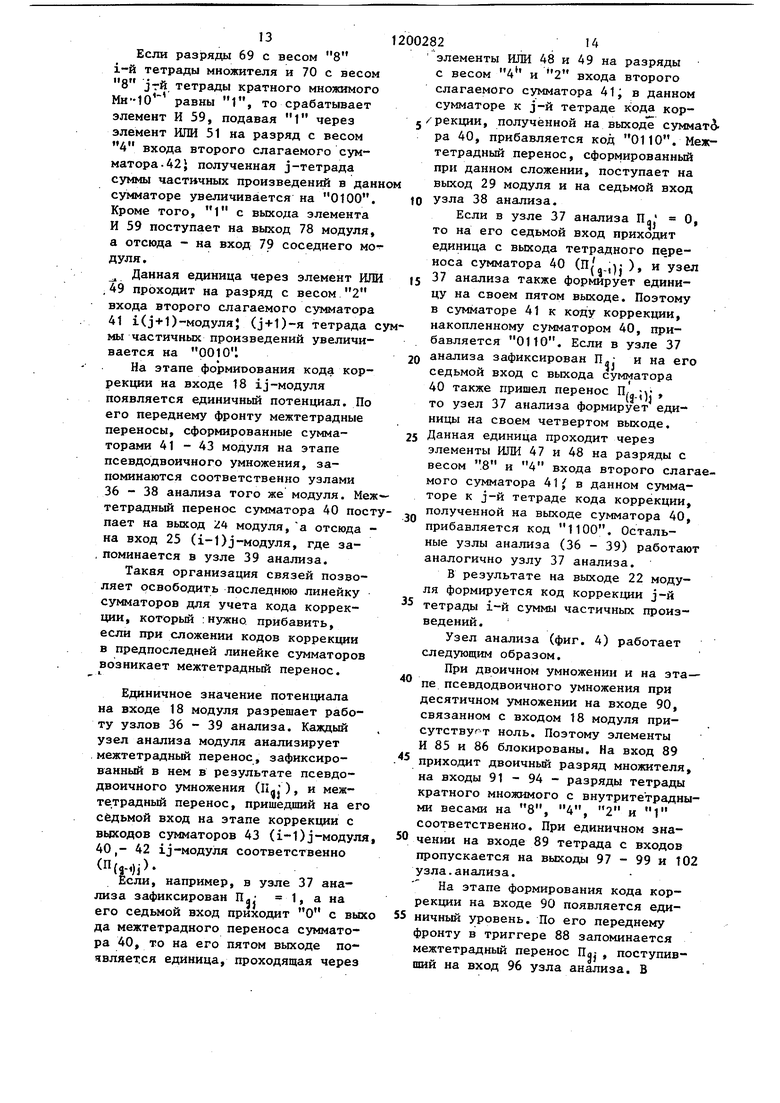

Йа фиг. 1 приведена структурная схема матричного устройства для умножения двоичных и десятичных чисел; на фиг. 2 - схема матрицы. 5 умножения} на фиг. 3 - схема модуля умножения тетрад, на фиг. 4 схема анализа, на фиг. 5 - временная диаграмма формирования управ;пяющих сигналов.

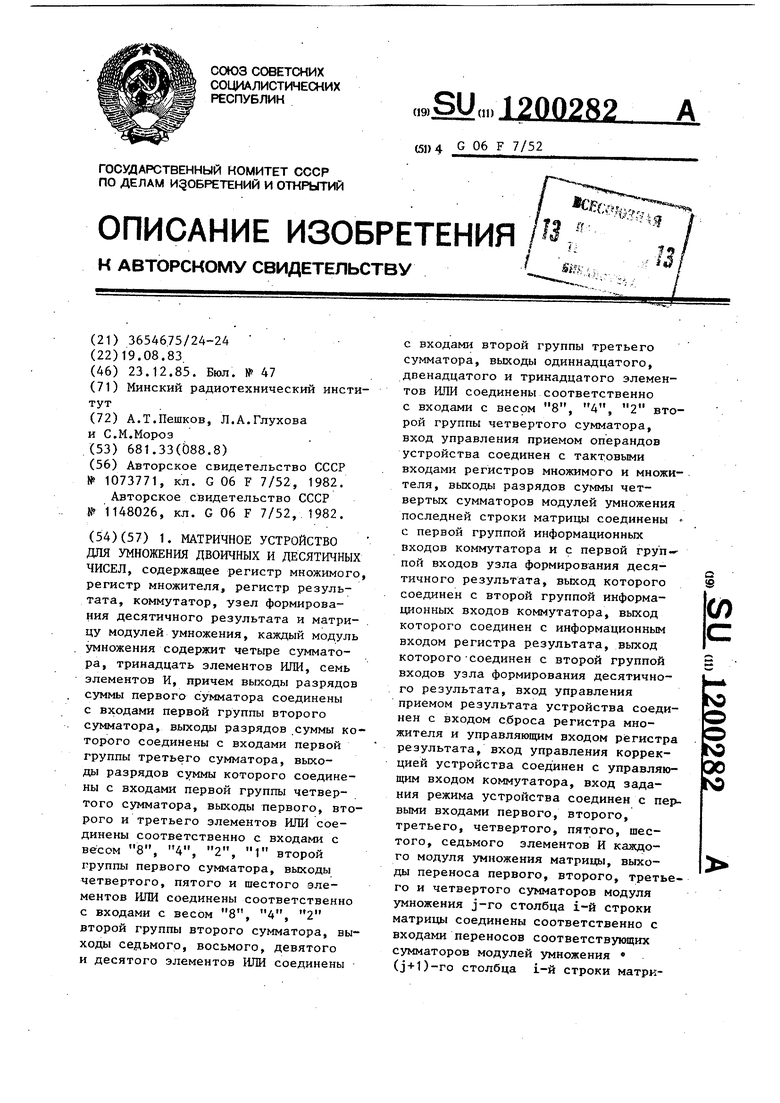

Матричное устройство для умножения двоичных и десятичных чисел (фиг. 1) содержит матрицу 1 умножения, регистр 2 множимого, регистр 3 множителя, регистр 4 результата, коммутатор 5, разрядностью п разрядов, узел 6 формирования десятичного результата, вход 7 сброса регистра множителя, вход 8 управления приемом операндов, первый 9 и второй 10 информационные входы матрицы умножения, вход 11 управления приемом резул1ьтата, вход

12управления коррекцией, первый

13и второй 14 управляющие входы матрицы умножения, вход 15 задания режима.

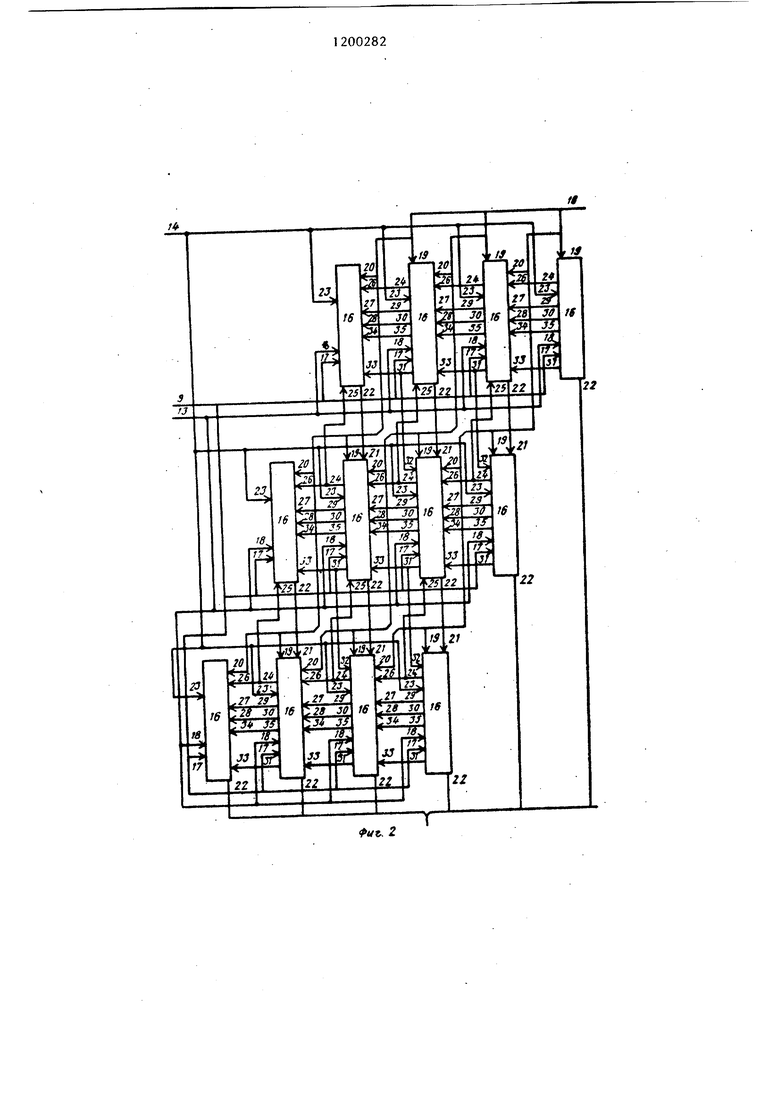

Матрица 1 умножения (фиг. 2) содержит модули 16 умножения, входы 17 - 21, выход 22, вход 23, выход 24, входы 25 - 28, выходы 29 - 31, входы 32 - 34, выход 35 модуля 16 умножения тетрад.

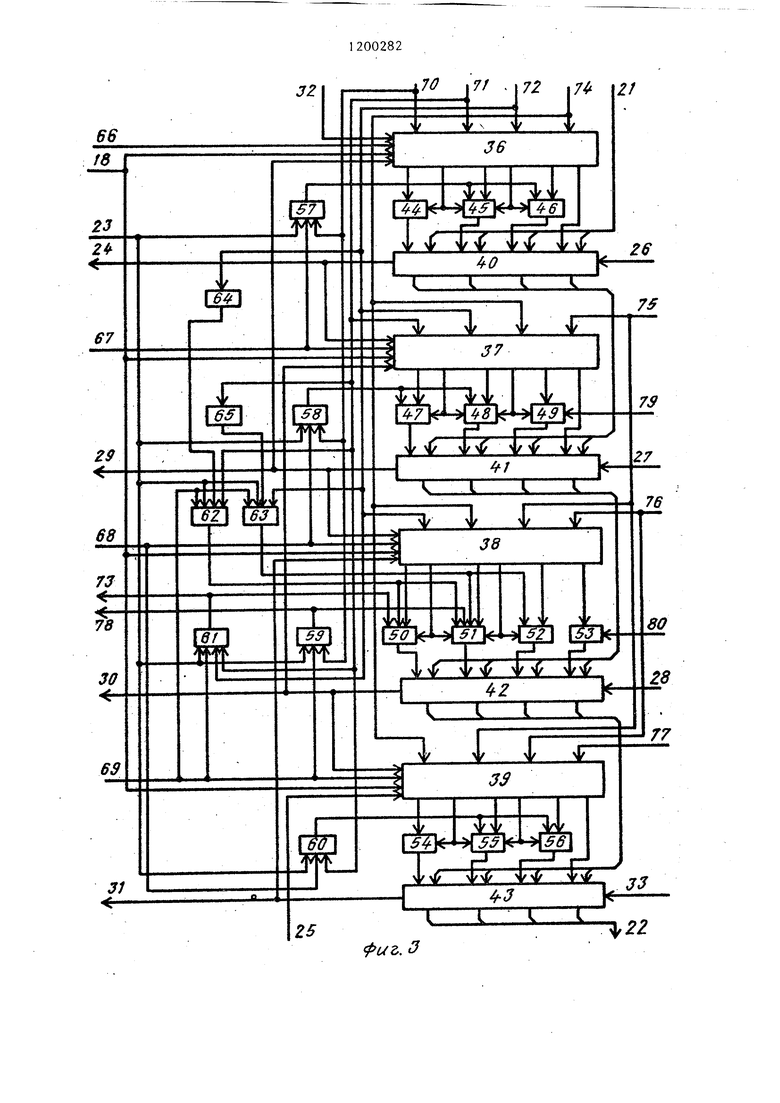

Модуль 16 умножения тетрад (фиг. содержит узлы 36 - 39 анализа, сумматоры 40 - 43, элементы ИЛИ 44 56, злементы И 57 - 63, элементы НЕ 64 и 65, разряды 66 - 69 входа 17, разряды 70 - 72 входа 19, разряд 73 выхода 35, разряд 74 входа 19, разряды 75 - 77 входа 20, разряд 78 выхода 35, разряды 79 - 80 входа 34.

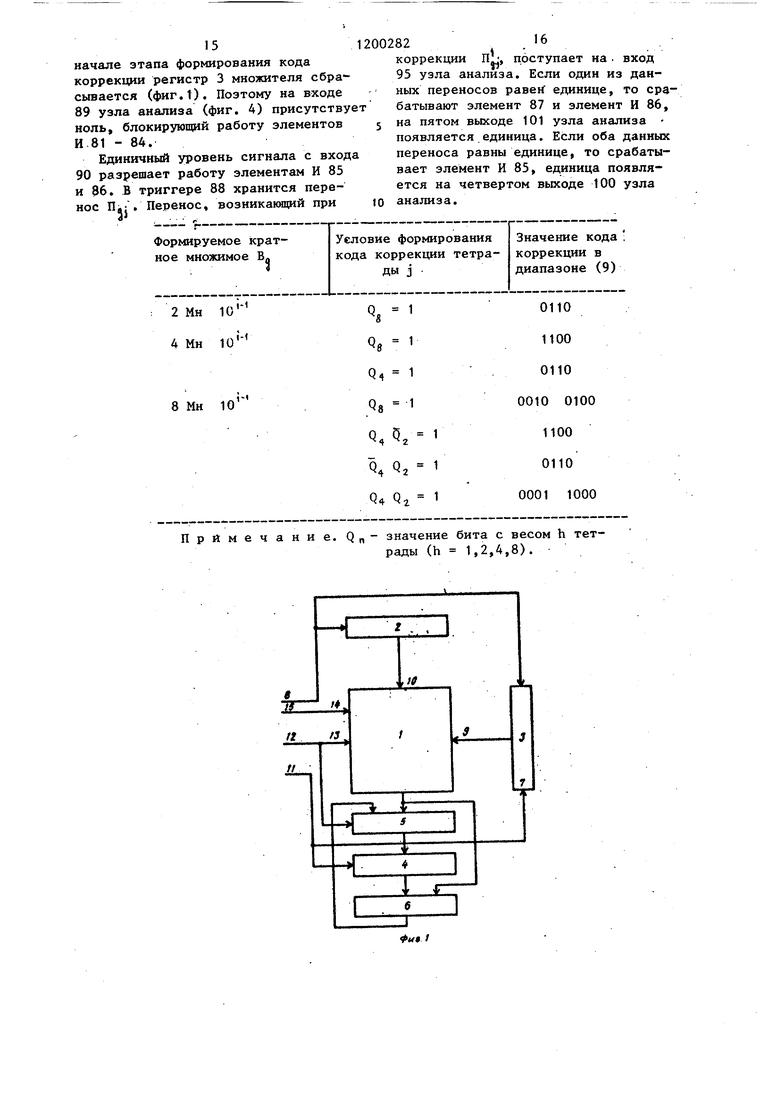

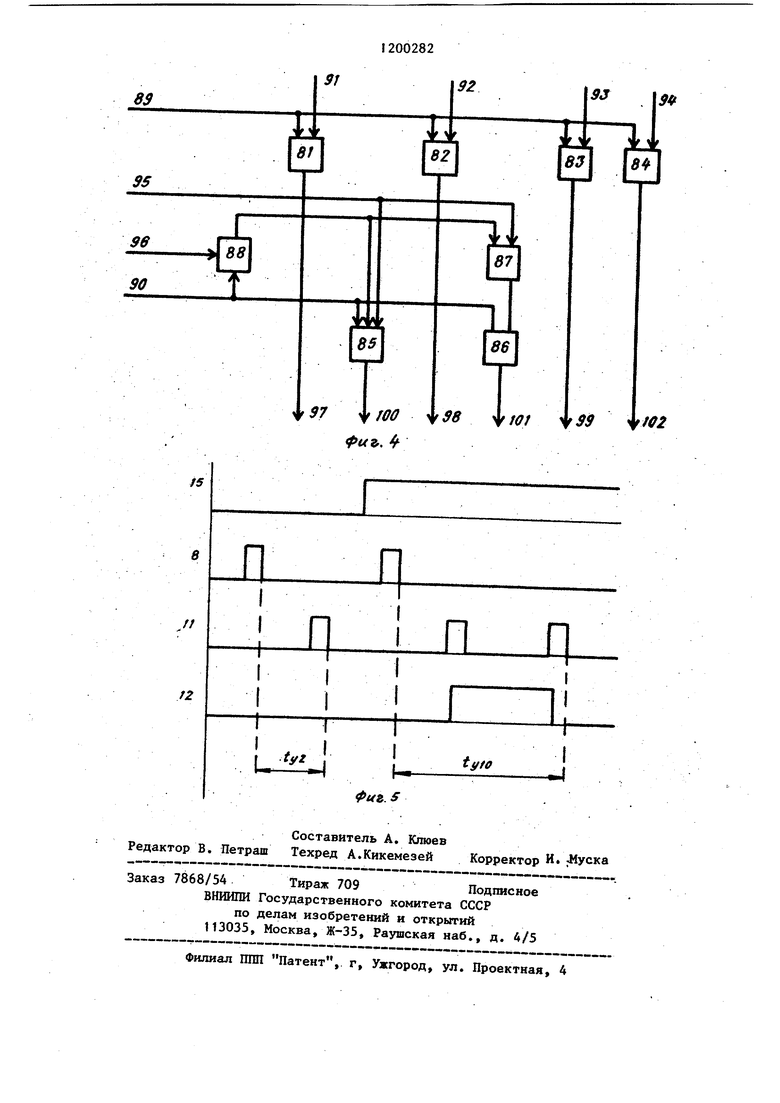

Узел анализа (Фиг. 4) содержит элементы И 81 - 86, элементы 87 сложения по модулю два, триггер 88, входы 89 - 96, выходы 97 - 102.

Матричное устройство для умножения двоичных и десятичных чисел использует следующий алгоритм формирования десятичного произведения: сформировать необходимые десятичные кратные десятичного множимого Вд в коде 8-4-2-1, сформировать псевдодвоичные произведения },д путем двоичного перемножения десятичных сомножителей;

сформировать код коррекции путем двоичного суммирования в некоторых тетрадах кодов коррекции 6 столько раз, сколько переносов возникло из данных тетрад в процессе получения wjp и ;

сформировать псевдодесятичную (с цифрами 0-15) сумму и путем двоичного суммирования их соответствующих тетрад с последующим прибавлением к ним кодов 6 столько раз, сколько переносов возникло из данных тетрад при двоичном сложении и прибавлении кодов 6, сформировать двоично-десятичное произведение путем коррек

ции полученной суммы за счет прибавления 6 к тетрадам, в которых возникли запрещенные для кода 8-4-2-1 комбинации (10 - 15), с распространением межтетрадных переносов.

Назовем первый этап этапом формирования псевдодвоичного произведения, второй - этапом формирования кода коррекции, третий - этапом формирования десятичного результата.

Bi ходе получения псевдодвоичного произведения десятичных сомножителей, представленных кодом 8-4-2-1, необходимо использовать кратные множимого, также представленные кодом 8-4-2-1. Данные кратные могут быть сформированы из множимо- . го М(| непосредственно в ходе двоичного перемножения десятичных сомножителей.

Кратные множимые получаются сдвигом множимого в сторону старших разрядов на соответствующее количество битов и последующей коррекцией, если при сдвиге в соседнюю старшую тетраду было выдвинуто ненулевое знаг чение.

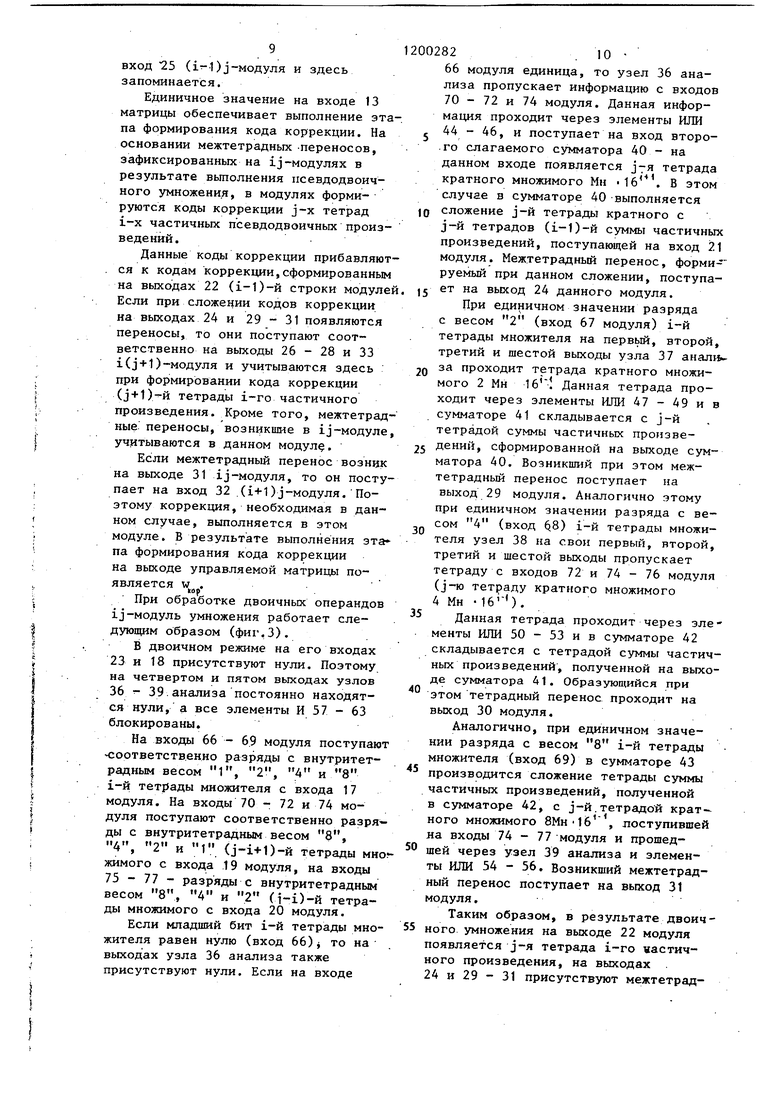

Условия формирования кодов коррекции тетрады крайних множимых, полученных при сдвиге кратного М 10 на один, два и три ряда, приведены

в таблице.

При умножении двоичных операндов матричное устройство для умножения двоичных и десятичных чисел

работает следующим образом.

По сигналу на входе 8 управления приемом операндов в регистры 2 и 3 принимаются сомножители. На входе 15 режима сигнал отсутствует. Матрица 1 множения перемножает коды множимого и множителя, поступающих соответственно на ее входы 10 и 9. В результате на выходе матрицы 1 появляется двоичное произведение.

В двоичном режиме на входе 12 управления коррекцией сигнал отсутствует. Поэтому коммутатор 5 пропускает информацию со своего

первого разрядного входа. Таким

образом, на входе регистра 4 появляется двоичное произведение с вьосода матрицы 1. По сигналу входа 11 управления приемом результата производится прием двоичного произведения в регистр 4. На этом умножение двоичных операндов оканчивается. Умножение десятичных операндов состоит из нескольких этапов; псев двоичного умноженияi формирования кода коррекции} формирования десятичного произведения, представленного кодом 8-4-2-1. По сигналу с входа 8 управления приемом операндов в регистры 2 и 3 принимаются сомножители в коде 8-4-2-1. В матрице 1 выполняется псевдодвоичное умножение десятичных кодов множимого и множите ля. При этом кратные множимые Вп, используемые матрицей 1 в ходе умножения, формируются непосред ственно в матрице 1 сдвигом множимого на число разрядов, соответствующее весу разрядов множител для умножения на которой Вл образу ются с последующей коррекцией на основании приведенной таблицы. Выполнение данного этапа отличается от истинного десятичного (в коде 8-4-2-1) умножения тем, что после прибавления в некоторой линейке сумматоров модулей 16 матрицы 1 умножения q частного про изведения коррекция не производится, В связи с этим при выполнении всевдодвоичного умножения накапливается погрешность, величина которой равна коду коррекции. Для того, чтобы сформировать код коррекции псевдодвоичного произведени необходимо заполнить межтетрадные переносы, полученные в ij-модулях матрицы на этапе псевдодвоичного умножения. Запоминание межтетрадны переносов может быть выполнено одн временно с приемом результата псев додвоичного умножения в регистр 4 результата. На этапе псевдодвоичного умножения на входе 12 блока управления коррекцией сигнал отсутствует. Поэ му коммутатор 5 пропускает информа цию с выхода матрицы 1. Через время, достаточное для вы полнения двоичного умножения в матрице 1, на входе 11 формируется сигнал, обеспечивающий прием резул тата псевдодвоичного умножения дес 826 тичных сомножителей в регистр 4 и сброс регистра 3 в ноль по входу 7. Одновременно с этим появляется потенциальный сигнал на входе 12. Данный сигнал поступает на управляющий вход 13 матрицы 1. По его переднему фронту межтетрадные переносы, формируемые при псёвдодвоичном умножении в каждой линейке сумматора модулей 16 матрицы, запоминаются в предьщущей линейке. Каждая строка модулей 16 умножения управляется соответствующей тетрадой множителя. В состав каждого модуля 16 входят четьфе линейки сумматоров, осуществляющих прибавление к ранее накопленной сумме частичных произведений необходимого кратного, если соответствующий бит тетрады множителя равен единице. Количество линеек сумматоров соответствует разрядности множителя. Отметим, что в первой линейке сум маторов переносы возникнуть не могут так, как в нейвозможно только сложение множимого с нулем. Поэтому переносы, возникающие во второй линейке сумматоров матрицы, могут запоминаться в первой линейке, возникающие в третьей линейке - во второй линейке сумматоров матрицы и т.д. При этом последняя линейка 1освобождается для учета кода коррекции (0110), который нужно прибавить в последней линейке сумматоров, если в предпоследней при накапливании кодов коррекции возник межтетрадньв перенос. Кроме того, единичное значение сигнала с входа 12 обеспечивает переключение коммутатора 5 в режим пропуска информации с выхода узла 6. На этом этап псевдодвоичного умножения десятичных операндов окан чивается. Результатом этапа являет ся псевдодвоичное произведение в регистре 4 и межтетрадные переносы, зафиксированные в каждом модуле умножения матрицы 1. На следующем этапе на основании зафиксированных межтетрадных переносов в матрице 1 формируется код коррекции результата псевдодвоичного умножения. Поскольку на данном этапе регистр 3 установлен в ноль, то значения соответствующих кратных множимых на ход коррекции влияния не оказывают. Данный этап выполняется под управлением потенциального сигнала с входа 12. Появление данного сигнала разрешает формирование кода коррекции в модулях матрицы 1. Если на этапе псевдс АВОИЧНОГО умножения в gj-линейке был запомнен межтетрадный перенос (П.:), то на этапе коррекции в данной линейке прибавится код коррекции ОНО к коду коррекции, накопленному в (g-1)j-линейке. Если при ко рекции в gj-линейке возникнет межтетрадный перенос ( ) то в (8+1)линейке к накопленной коррекции прибавится код 6 (если 3fOi ( ( Таким образом, к концу этапа корре цйи на выходе матрицы 1 сформируется значение кода коррекции резул тата псевдодвоичного умножения. На следующем этапе - этапе форм рования десятичного результата в узле 6 на основании полученного псевдодвоичного произведения и накопленного кода коррекции формируе ся десятичное произведение в коде .8-4-2-1 х,д. Узел 6 формирования десятичного результата реализован аналогично известному устройству, В данном узле выполняется двоичное сложение псевдодвоичного произведения и накопленного кода коррекции. Далее полученная двоичная сумма корректи руется согласно следующему алгорит проанализировать межтетрадные переносы, возникшие при двоичном суммировании. Если в.некоторой тет раде перенос равен единице, то к содержимому данной тетрады необходимо прибавить код коррекции 0110 проанилизировать межтетрадные переносы, возникшие при первом двоичном прибавлении кода ОНО. Если в некоторой тетраде перенос равен единице, То к содержимому данной тетрады необходимо прибавит код коррекции 0110. Если после выполнения второго этапа в некоторой тетраде имеет ме то запрещенная комбинация (1010 1111), то к содержимому данной тет рады необходимо прибавить код корр ции 0110. Поскольку на данном этапе коммутатор 5 установлен в режим пропу кания информации с выхода узла б (на входе 12 присутствует единич28ное значение сигнала), то десятичное произведение через коммутатор 5 поступает на разрядный вход регистра 4 результата, где запоминается г по сигналу на входе 11 управл ёния приемом результата. Матрица умножения (фиг. 2) работает следующим образом. При обработке двоичных операндов на входах 13 и 14 матрицы присутствует ноль. В ij-модуле формируется j-я тетрада i-й суммы частичных произведений (на выходе 22) и четыре разряда межтетрадных переносов (на выходах 24 и 29 - 31), образовав шихся на выходах переноса первой-четвертой линеек сумматоров. Данные переносы поступают соответственно на четыре разряда входа тетрадного переноса 26 - 28 и 33 соседнего старшего модуля той же строки, учитываясь здесь при формировании (з+1)-й тетрады суммы чacтич ных произведений. Таким образом, на выходах 22 i-й строки модулей умножения формируется 1-я сумма частичных: произведений. На выходах 22 последней строки модулей образуется двоичное произведение. При обработке десятичных чисел, представленных кодов 8-4-2-1, на входе 14 матрицы присутствует единичный сигнал. Данный сигнал поступает на входы 23 всех модулей умножения. Это обеспечивает выполнение в ij-модулях условий коррекции используемых кратных множимых, множимого на один, два, или три биты. Поэтому в ходе формирования i-ой суммы частичных цроизведений фактически участвуют кратные множимые представлены кодом 8-4-2-1. В остальном выполнение этапа псевдодвоичного умножения не отличается от умножения двоичньк чисел. На выходах 22 последней строки модулей образуется псевдодвоичное произведение. Через время, достаточное для получения всевдодвоичного произведения на входе 13 матрицы появляется управляющий сигнал. По его переднему фронту межтетрадные переносы, сформированные на выходах 29-31 модуля, запоминаются в том же модуле. Межтетрадный перенос с выхода 24 ij-модуля поступает на

вход 25 (i-1)j-модуля и здесь запоминается.

Единичное значение на входе 13 матрицы обеспечивает выполнение этапа формирования кода коррекции. На основании межтетрадных-переносов, зафиксированных на ij-модулях в результате выполнения псевдодвоичного умножения, в модулях формируются коды коррекции j-x тетрад i-x частичных псевдодвоичных произведений.

Данные коды коррекции прибавляются к кодам коррекции,сформированным на выходах 22 (1-1)-й строки модуле Если при сложении кодов коррекции на выходах 24 и 29-31 появляются переносы, то они поступают соответственно на выходы 26 - 28 и 33 1(3+1)модуля и учитываются здесь при формировании кода коррекции (j+1)-й тетрады i-ro частичного произведения. Кроме того, межтетрадные переносы, возникшие в ij-модуле учитываются в данном модул.

Если межтетрадный перенос возник на выходе 31 ij-модуля, то он поступает на вход 32 .(i+1)j-модуля.Поэтому коррекция, необходимая в данном случае, выполняется в этом модуле. В результате выполнения эта па формирования кода коррекции на выходе управляемой матрицы появляется W .

пор

При обработке двоичных операндов ij-модуль умножения работает следующим образом (фиг.З).

В двоичном режиме на его входах 23 и 18 присутствуют нули. Поэтому на четвертом и пятом выходах узлов 36 39.анализа постоянно находятся нули, а все элементы И 57 - 63 блокированы.

На входы 66 - 69 модуля поступаю ч:оответственно разряды с внутритетрадным весом 1, 2, 4 и 8 i-й тетрады множителя с входа 17 модуля. На входы 70 - 72 и 74 модуля поступают соответственно разряды с внутритетрадным весом 8, 4, 2 и 1 0--1-И)-й тетрады мн жимого с входа 19 модуля, на входы 75 - 77 - разряды с внутритетрадным весом 8, 4 и 2 (1-)-й тетрады множимого с входа 20 модуля.

Если младший бит i-й тетрады множителя равен нулю (вход 66)j то на выходах узла 36 анализа также присутствуют нули. Если на входе

66 модуля единица, то узел 36 анализа пропускает информацию с входов 70 - 72 и 74 модуля. Данная информация проходит через элементы ИЛИ 44 - 46, и поступает на вход второ.го слагаемого сумматора 40 - на данном входе появляется j7Я тетрада кратного множимого Мн -16 . В этом случае в сумматоре 40 выполняется

сложение j-й тетрады кратного с

j-й тетрадов (i-1)-й суммы частичных произведений, поступающей на вход 21 модуля. Меж.тетрадный перенос, форми- руемый при данном сложении, поступает на выход 24 данного модуля.

При единичном значении разряда с весом 2 (вход 67 модуля) i-й тетрады множителя на первьй, второй, третий и шестой выходы узла 37 анашг за проходит тетрада кратного множи0мого 2 Мн 16. Данная тетрада проходит через элементы ИЛИ 47 - 49 и в сумматоре 41 складывается с j-й тетрадой суммы частичных произведений, сформированной на выходе сумматора 40. Возникт1й при этом межтетрадный перенос поступает на выход 29 модуля. Аналогично этому при единичном значении разряда с весом 4 (вход 68) i-й тетрады множи0теля узел 38 на свои первый, второй, третий и шестой выходы пропускает тетраду с входов 72 и 74 - 76 модуля (j-ю тетраду кратного множимого 4 Мн ).

5

Данная тетрада проходит через элементы ИЛИ 50 - 53 и в сумматоре 42 складывается с тетрадой суммы частичных произведений, полученной на выходе сумматора 41. Образующийся при

0 этом тетрадный перенос проходит на выход 30 модуля.

Аналогично, при единичном значении разряда с весом 8 i-й тетрады множителя (вход 69) в сумматоре 43

5 производится сложение тетрады суммы частичных произведений, полученной в сумматоре 42, с j-й. тетрадой кратного множимого 8Мн 16 , поступившей на входы 74 - 77 модуля и прошед0шей через узел 39 анализа и элементы ИЛИ 54 - 56. Возникший межтетрадный перенос поступает на выход 31 модуля,

Таким образом, в результате двоичного умножения на выходе 22 модуля появляется j-я тетрада i-ro частичного произведения, на выходах . 24 и 29 - 31 присутствуют межтетрадные переносы, возникшие в сумматорах 40 - 43.

При обраб,отке операндов, представленных кодом 8-4-2-1, ij-моду умножения работает следующим образом.

В десятичном режиме на входе 23 одуля присутствует единица, что разрешает работу всех элементов И 57 - 63. На этапе псевдодвоичного умножения узлы 36 - 39 анализа и сумматоры 40 - 43 работают аналогично описанному вьше для случая обработки двоичных чисел. При этом на входы узлов 36-39 анализа, а следовательно, и на входы второго слагаемого сумматоров 40 43 поступают соответственно j-e тетрады ратных множимых Мн -10 Мн10 , сдвинутого на один двоичный разряд влево, Мн 10 , сдвинутого двоичных разряда влево, Мн 10 сдвинутого на три двоичных разряда влево.

Как было показано ранее., на этап псевдодвоичнрго -умножения в операции должны участвовать множимое Мн и его кратные, представленные кодом 8-4-2-1.

Вьшолнение коррекции кратных, согласно приведеннойтаблице, осуществляется следукяцим образом.

Если разряд с весом 2 i-й тетрды множителя равен 1 (это говорит о том, что должно быть прибавлено кратное 2 Мн-10) и разряд с весом 8 j-й тетрады кратного Мн.10 также равен единице (что в коде 8-4-2-1 характерно лишь.для комбинаци 1000 и 1001), то срабатывает элемент И 57 (фиг. 3), обеспечивая подачу «единиц через элементы ИЛИ 45 и 46 на разряды с весом 4 и 2 входа второго слагаемого сумматора 40..

Если разряд с весом 4 i-й тетрады множителя равен 1 (должно быть прибавлено кратное множимое 4 Мн«10) и разряд с весо 8 j-й тетрады кратного также равен единице (данная тетрада равна 1000 или 1001), то срабатывает элемент И 58, обеспечивая подачу через элементы И 47 и 481 единиц на разряды с весом 8 и 4 входа второго слагаемого сумматора 41.

ЕСЛИ разряд 68 с весом 4 i-й тетрады множителя равен 1 и разря

71 с весом 4 j-и тетрады кратного множимого Мн 10 также равен 1 (это является условием прибавления кода 0110 к j-й тетраде 4.МН.),

с то срабатывает элемент И 60,

обеспечивая подачу через элементы ИЛИ 55 и 56 единиц. В сумматоре 43 j-я тетрада суммы частичньк произведений, сформированная в сумматоQ ре 42, увеличивается на шесть.

Если разряд 69 с весом 8 i-й тетрады множителя равен единице, разряды 72 с весом 2 и 71 с весом 4 jrn тетрады кратного множимого

5 соответственно равны 1 и О, то срабатьшает элемент И 63. обеспечивая подачу через элементы ИЛИ 51 и 52 единиц на разряды с весом 4 и 2 входа второго слагаеQ мого сумматора 42J в данном сумматоре производится сложение суммы . частичньпс произведений, полученной в сумматоре 41, с кодом 0110.

Если разряд 69 с весом. 8 i-й 5 тетрады множителя равен 1, разряды 72 с весом 2 и 71 с весом 4 соответственно равны О и 1, то срабатывает элемент И 62, подавая через элементы ИЛИ 50 и 51 0 единицы на разряд с весом 8 и 4 входа второго слагаемого сумматора 42, в данном сумматоре складывается сумма частичных произведений, полученная в сумматоре 41, с кодом C коррекции 1100.

Если разряд 69 с весом 8 i-й тетрады множителя равен 1 и разряды 72 и 71.с весом 2 и 4 j-ой тетрады 10 -кратного множимого также равны 1, то срабатьгоает

элемент И 61, обеспечивая подачу через элемент ИЛИ 50 единицы на разряд с весом 8 сумматора 42, в данном сумматоре j-я тетрада суммы час5

тичных произведении, полученная сумматором 41, увеличивается на 1000. Кроме того, 1 с выхода элемента И 61 поступает на выход 73 модуля, а отсюда на вход 80 соседнего

модуля. Данная единица через элемент ИЛИ 53 i (j+1)-мoдyля поступает на разряд с весом 1 сумматора 42 i в сумматоре 42 i(j+1)-мoдyля (j+1)-я тетрада суммы частичных

произведений увеличивается на единицу. Таким образом, формируется

м код коррекции кратного 8-Мн 10 0001 1000 (18). Если разряды 69 с весом 8 i-й тетрады множителя и 70 с весом 8 jrft тетрады кратного множимого Мн-10 равны 1, то срабатывает элемент И 59, подавая 1 через элемент ИЛИ 51 на разряд с весом 4 входа второго слагаемого сумматора -42} полученная j-тетрада суммы частичных произведений в дан сумматоре увеличивается на 0100. Кроме того, 1 с выхода элемента И 59 поступает на выход 78 модуля, а отсюда - на вход 79 соседнего мо дуля. Данная единица через элемент ИЛ ,49 проходит на разряд с весом 2 входа второго слагаемого сумматора 41 1(3+1)-модуля} (j+1)-я тетрада мы частичных произведений увеличивается на 00101 На этапе формирования кода коррекции на входе 18 ij-модуля появляется единичный потенциал. По его переднему фронту межтетрадные переносы, сформированные сумматорами 41-43 модуля на этапе псевдодвоичного умножения, запоминаются соответственно узлами 36-38 анализа того же модуля. Ме тетрадный перенос сумматора 40 пос пает на выход 24 модуля,а отсюда на вход 25 (1-1)3-модуля, где за, поминается в узле 39 анализа. Такая организация связей позволяет освободить последнюю линейку сумматоров для учета кода коррекции, который :нужно прибавить, если при сложении кодов коррекции в предпоследней линейке сумматоров возникает межтетрадньш перенос. Единичное значение потенциала на входе 18 модуля разрешает работу узлов 36 - 39 анализа. Каждый узел анализа модуля анализирует межтетрадный перенос, зафиксированный в нем в результате псевдодвоичного умножения (II- ), и межтетрадный перенос, пришедший на ег седьмой вход на этапе коррекции с выходов сумматоров 43 (i-1)j-модул 40,- 42 ij-модуля соответственно ((|-i)i Если, например, в узле 37 анализа зафиксирован П.- 1, а на его седьмой вход приходит О с вы да межтетрадного переноса сумматора 40, то на его пятом выходе появляется единица, проходящая через 214 элементы ИЛИ 48 и 49 на разряды с весом и 2 входа второго слагаемого сумматора 41j в данном сумматоре к j-й тетраде кода коррекции, полученной на выходе сумматбра 40, прибавляется код 0110. Межтетрадный перенос, сформированный при данном сложении, поступает на выход 29 модуля и на седьмой вход узла 38 анализа. Если в узле 37 анализа Пд 0, то на его седьмой вход приходит единица с выхода тетрадного переноса сумматора 40 (П/..,),- ), и узел 37 анализа также формирует единицу на своем пятом выходе. Поэтому в сумматоре 41 к коду коррекции, накопленному сумматором 40, прибавляется 0110. Если в узле 37 анализа зафиксирован П.- и на его седьмой вход с выхода сумматора 40 также пришел перенос П/- ;v , то узел 37 анализа формирует единицы на своем четвертом выходе. Данная единица проходит через элементы ИЛИ 47 и 48 на разряды с весом 8 и 4 входа второго слагаемого сумматора 41 в данном сумматоре к j-й тетраде кода коррекции, полученной на выходе сумматора 40, прибавляется код 1100. Остальные узлы анализа (36 - 39) работают аналогично узлу 37 анализа. В результате на выходе 22 модуля формируется код коррекции j-й тетрады i-й суммы частичных произведений. Узел анализа (фиг. 4) работает следующим образом. При двоичном умножении и на эта- пе псевдодвоичного умножения при десятичном умножении на входе 90, связанном с входом 18 модуля присутствугТ ноль. Поэтому элементы И 85 и 86 блокированы. На вход 89 приходит двоичный разряд множителя, на входы 91 - 94 - разряды тетрады кратного множимого с внутритетрадными весами на 8, 4, соответственно. При единичном зна- чении на входе 89 тетрада с входов пропускается на выходы 97 - 99 и 102 узла.анализа. На этапе формирования кода коррекции на входе 90 появляется единичный уровень. По его переднему ронту в триггере 88 запоминается ежтетрадный перенос , поступивий на вход 96 узла анализа, В начале этапа формирования кода коррекции регистр 3 множителя сбрасывается (фиг.1). Поэтому на входе 89узла анализа (фиг, 4) присутству ноль, блокирующий работу элементов И.81 - 84. Единичный уровень сигнала с вход 90разрешает работу элементам И 85 и 86. В триггере 88 хранится пере нос 11|,;. Перенос, возниканиций при

Формируемое кратное множимое Вд

2 Мн 10

|-(

4 Мн 10

18 Мн 10

Примечание. Qn- значение бита с весом h тет7

/,

гг /3

Условие формирования кода коррекции тетрады j

0110

1100

0110 0010 0100 1

1100

1

0110 0001 1000 1 рады (h 1,2,4,8).

vV 82 П:, поступает на . вход коррекции 95 узла анализа. Если один из данных переносов единице, то срабатывают элемент 87 и элемент И 86, на пятом выходе 101 узла анализа появляется единица. Если оба данных переноса равны единице, то срабатывает элемент И 85, единица появляется на четвертом выходе 100 узла анализа.

фыг.З

| Устройство умножения двоично-десятичных цифр | 1982 |

|

SU1073771A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Авторское свидетельство СССР № 1148026, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для видения на расстоянии | 1915 |

|

SU1982A1 |

Авторы

Даты

1985-12-23—Публикация

1983-08-19—Подача