Изобретение относится к вычислительной технике и может быть использовано для умножения двоичных и десятичных чисел, а также для преобразования чисел из двоич-ной системы счисления в десятичную и обратно, особенно эффективно его применение в качестве основы при разработке быстродействующих арифметических устройств универсальных ЭВМ, работающих как с двоичными, так и с десятичными числами.

Цель изобретения - повышение быстродействия и расширение функциональных возможностей за счет выполнения операций преобразования чисел из двоичной системы счисления в десятичную и обратно.

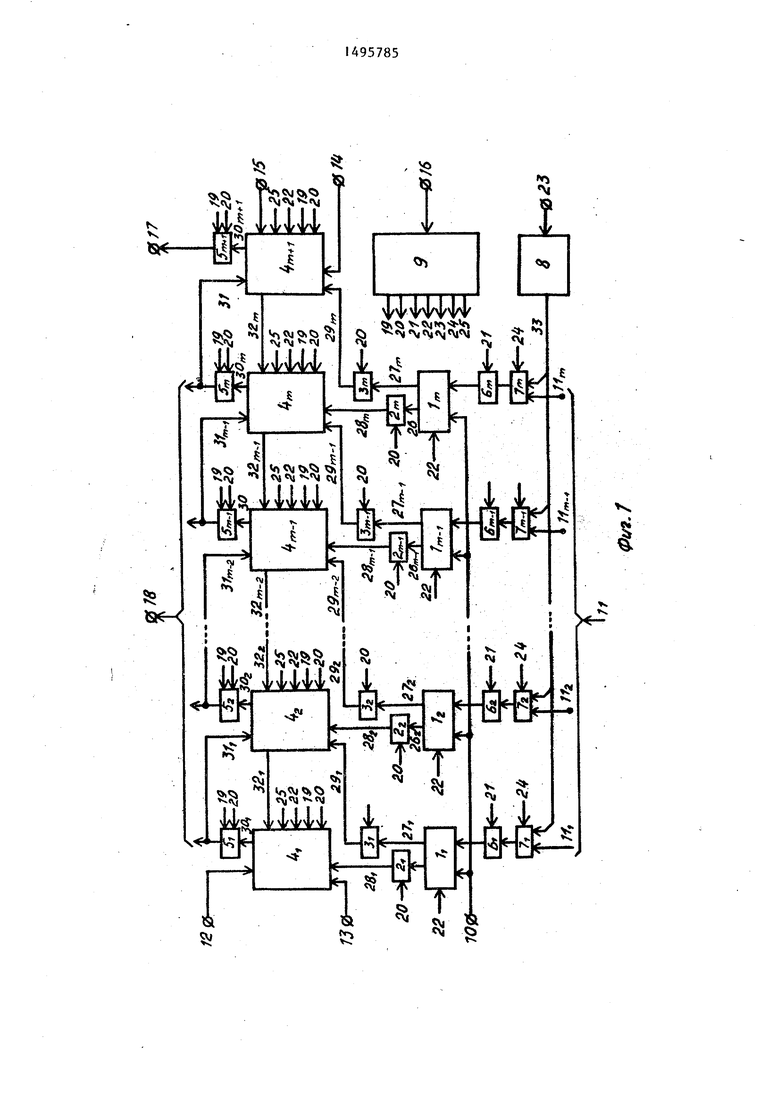

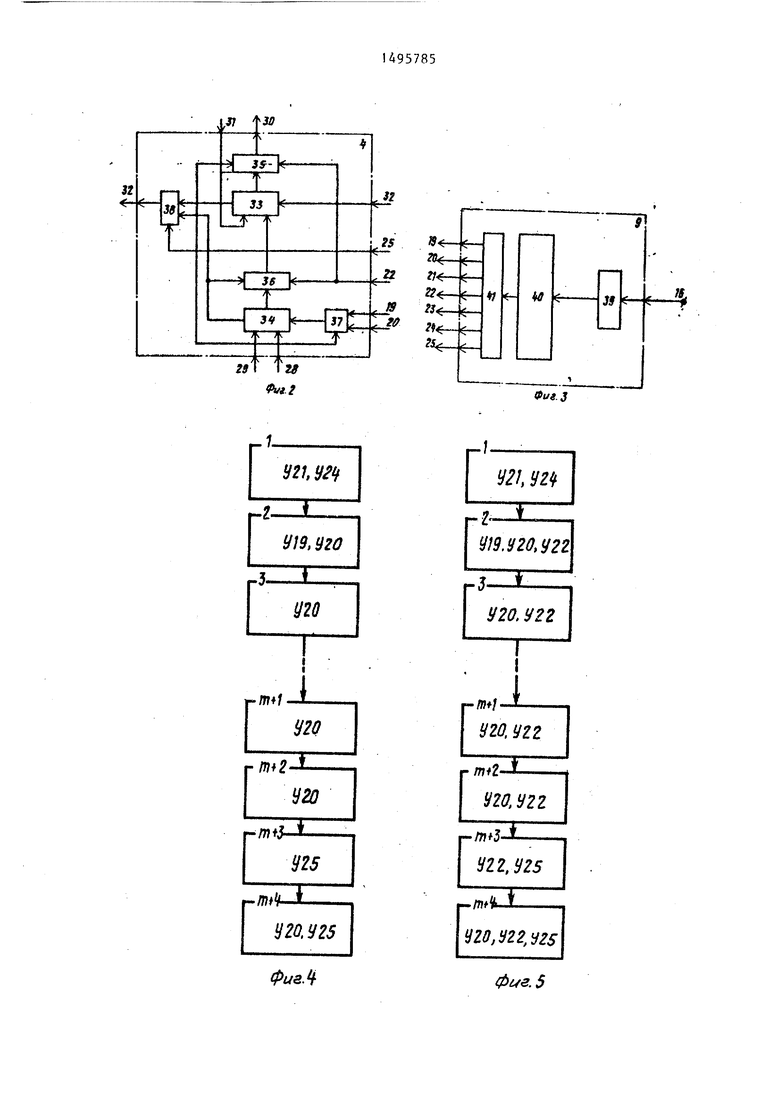

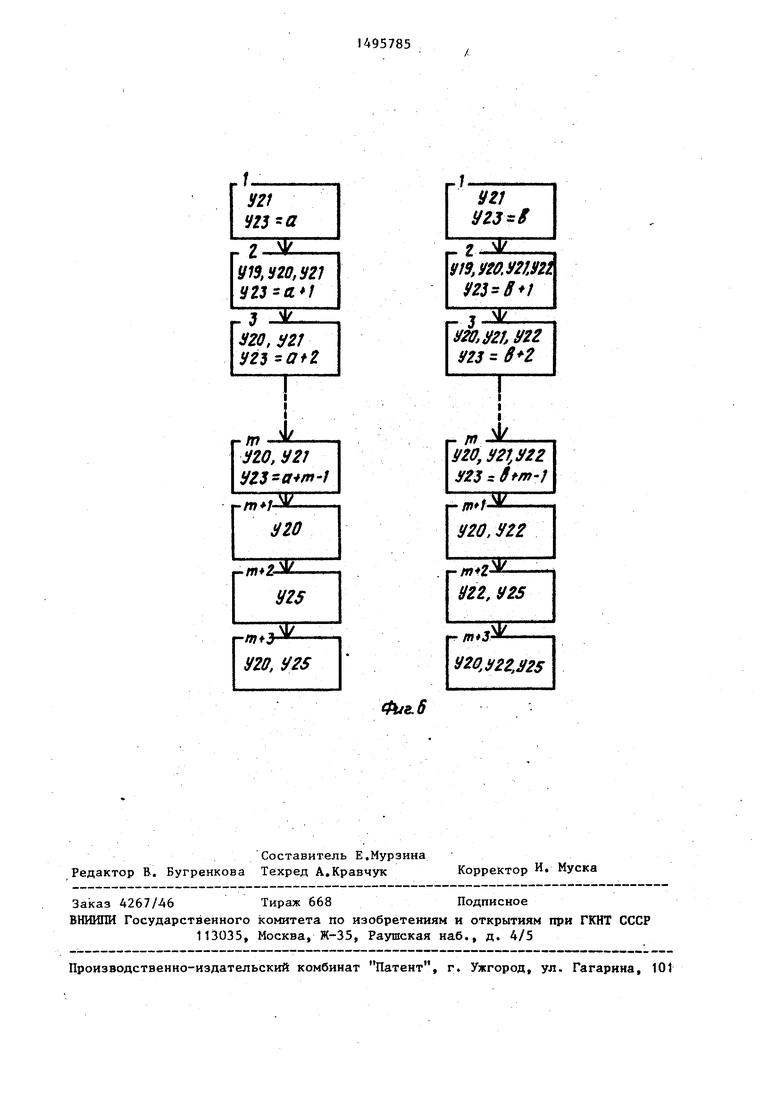

На фиг„1 показана функциональная схема устройства для умножения; на фиг. 2 - функциональная схема блока суммирования; на фиг.З - функциональная схема микропрограммного блока управления; на фиг. 4-6 - микропрограммы выполнения в устройстве соответственно операций дпоичного умножения, десятичного умножения, преобразования двоично-десятичного кода в двоичный и преобразования двоичного кода в двоично-десятичный.

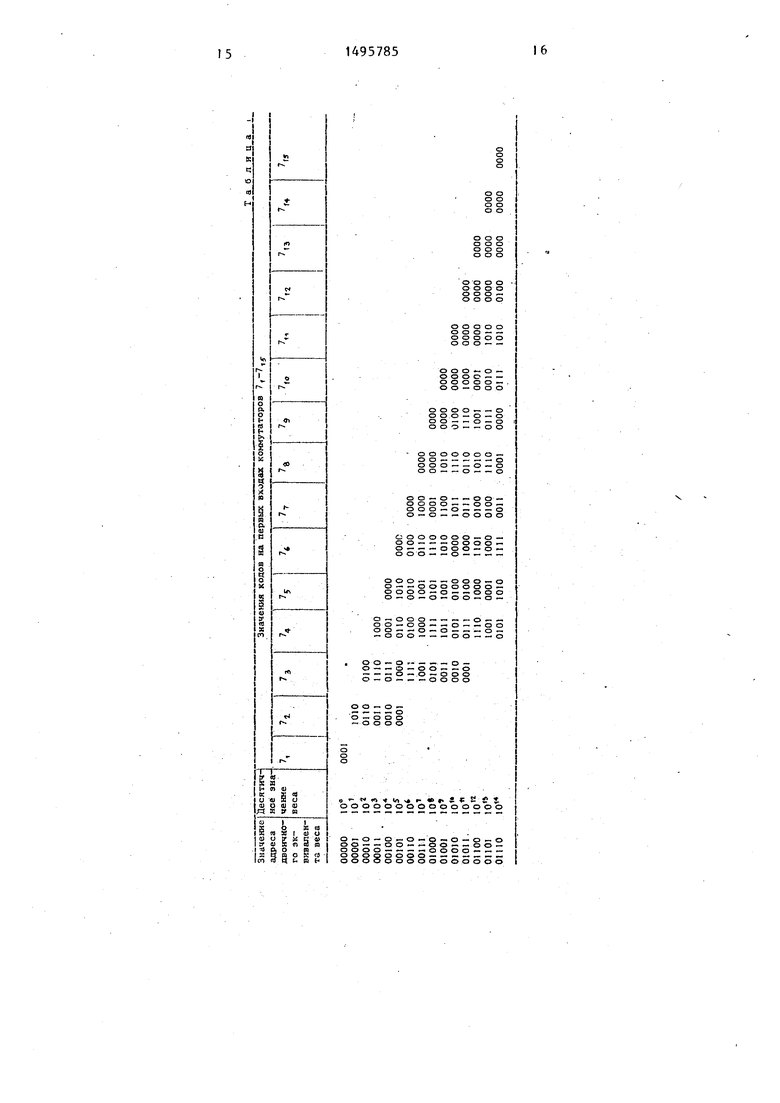

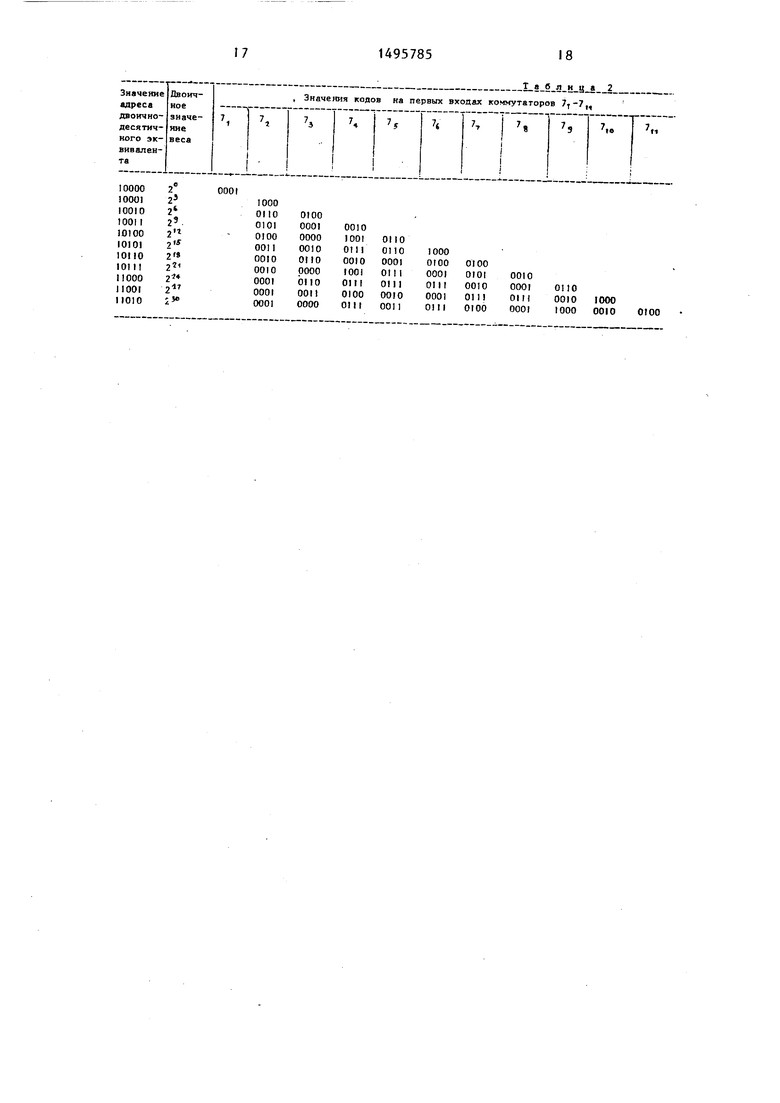

В табл. 1 и 2 приведены значения соответственно двоичных и двоично- десятичных эквивалентных весов преобразуемых групп разрядов.

Устройство для умножения содержит (фиг.1) блоки умножения, буферные регистры первой второй групп, блоки 4 -4 суммирования , регистры 5 -5 f, результата, регистры 6 ,-6fn операнда, коммутаторы 7,-7, блок 8 хранения смещенных эквивалентов, микропрограммный блок 9 управления, вход 10 множителя устройства, вход 11 множимого устройства, состоящий из входов 1 -1 1 j тетрад разрядов, вход 12 коррекции устройства, вход первой 13 и второй 14 констант устройству, вход 15 нулевого потенциала устройства, вход 16 начального адреса устройства, выход 17 .младшей части результата устройства, выход 18 старшей части результата устройства, выходы 19-25 микропрограммного блока 9 управления, выходы старших частей произведений и

выходы 27 ,-27 младших частей произведений блоков 1,-1 JJ, умножения, выходы 28;,-28 буферных регистров. 2 ,-2 первой группы, выходы 29 буферных регистров 3 ,-3 второй группы, выходы 30,-30 , суммы блоков 4.,-4 .., суммирования, выходы , регистров 5i-5 „ результата, выходы 32.-32 j переноса блоков сум- мирования.

Блок 4 суммирования содержит (фиг.2) первый 33 и второй 34 сумматоры, первый 35 и второй 36 корректирующие сумматоры, триггер 37 переноса и коммутатор 38 переноса.

Микропрограммный блок 9 управления содержат, (фиг.3) счетчик 39, элемент 40 памяти микрокоманд, регистр 41 микрокоманд.

Рассмотрим функциональное назначение и реализацию основных блоков и узлов устройства.

Каждый из блоков 1 -1 р, умножения осуществляет умножение соответствующей тетрады разрядов множимого на тетраду разрядов множителя. В зависимости от значения потенциала, по- ступающего с выхода 22 микропрограммного блока управления на вход выбор режима блока 1 умножения, на его выходе 26 старшей и выходе 27- младше

)Q 15

20

25

30

35

40

ай

45

4957854

частей произведения появляется результат умножения либо в двоичном, либо в двоично-десятичном коде, при-, чем потенциал логической единицы на выходе 22 блока 9 обеспечивает работу устройства в десятичной системе счисления, а потенциал логического нуля - его работу в двоичной системе счисления.

Блоки умножения целесообразно реализовать в виде ППЗУ. В этом случае младшая или старшая части двоично-десятичного произведения на выходах блока умножения могут формироваться уже скорректированными на +6 без каких-либо дополнительных аппаратных затрат. Такая коррекция двоично-десятичного кода произведения необходима для формирования в дальнейшем в блоках , суммирования десятичного результата.

Буферные регистры первой 2,-2 „ и второй 3,-3 групп позволяют распараллелить в устройстве процесс вычисления тетрадных произведений в блоках умножения с процессом суммирования полученных в предыдущих тактах тетрадных произведений и частичных результатов.

Блоки 4,-4 „.,,суммирования предназначены для формирования промежуточных и окончательного результатов при выполнении операции двоичного и десятичного умножения, а также преобразования, причем все они работают идентичным образом.

Триггеры 37 переноса и коммутаторы 38 переноса в блоках суммирования позволяют сбалансировать время выполнения суммирования тетрадных произведений и частичных результатов в блоках суммирования с временем вычисления тетрадных произведений в бло ках умножения.

Первый корректирующий сумматор 35 фактически осуществляет коррекцию

-6 при отсутствии переноса сумматора 33, а второй корректирующий сумматор 36 - коррекцию +6 при наличии переноса сумматора 34. В противных случаях корректоры 35 и 36 передают информацию без изменений.

Если старшие тетрады произведений на выходах блоков умножения формируются уже скорректированными на +6, то на вход 13 первой константы устройства подается код 0000, а на вход 14 второй констаиты - код 0110. Если младшие тетрады произведений на выходах блоков 1,1„ умножения формируются уже скорректированными на +6, то на вход 13 пер вой константы подается код 0110, а на вход 14 второй константы - код 0000. Свободный первый вход первого сумматора 33 первого блока 4, суммирования является входом 12 коррекции устройства,.через который при двоичном умножении чисел в дополнительных кодах может вводиться коррекция, либ подсуммироваться в процессе умножени двух чисел третье число к получающе- муся произведению.

Регистры j операнда предназначены для хранения значения множимого при выполнении в устройстве операции умножения и временного хранения двоичных или двоично-десятичных эквивалентов весов преобразуемых групп разрядов при выполнении операции преобразования.

Блок 8 хранения смещенных эквива- лентов и группы коммутаторов 7 необходимы для преобразования чисел из двоичной системы счисления в десятичную и обратно.

Устройство для умножения работает следующим образом.

Устройство работает в двух режимах: режиме умножения чисел и в режиме преобразования чисел. На фйг.4- 6 изображены микропрограммы выполне- ния соответственно операций двоичного умножения, десятичного умножения, преобразования из двоично-десятичного кода в двоичный и преобразова- ния из двоичного кода в двоично-деся тичный. Выражение вида YN где , 20,21,22,24,25, на фиг.4-6 означает наличие на соответствующем выходе N блока 9 управления сигнала логической единицы.

Значения адресов, по которым в блоке 8 записаны первый двоичный и первьй двоично-десятичный эквиваленты, равны соответственно а и Ь.

Перед началом работы выполнения микропрограммы двоичного умножения, а также всех других микропрограмм предполагается, что на цепи синхро- низации устройства подается два предварительных синхроимпульса. По пер- Бому синхроимпульсу счетчик 39 блока 9 управления устанавливается в исходное состояние посредством подачи на вход 16 устройства начального адреса микропрограмм. По второму синхроимпульсу согласно содержимому .счетчика 39, которое служит адресом обращения к памяти 40 микрокоманд, из этой памяти в регистр 41 записывается значение первой микрокоманды, а значение адреса в счетчике 39 увеличивается на единицу. При выполнении операции двоичного умножения по втб- рому синхроимпульсу на втором вхо- де 11 устройства также появляется п-разрядный двоичный код множимого.

При выполнении первой микрокоманд (фиг.4) под воздействием управляющих сигналов У 21 и У 24 значение множимого с входа 11 устройства записьгаа- ется в регистры 6 -6 операнда. Одновременно на входе 10 устройства устанавливается значение самой младшей тетрады множителя.

В первом такте собственно двоичного умножения ( вторая микрокоманда) в блоках I, самая младшая тетрада множителя перемножается на соответствующие тетрады множимого. Двоичные результаты этих тетрадных умножителей записываются в буферные регистры 2, сигналу разрешения У 20. Одновременно происходит обнуление регистров „, + , результата и триггеров блоков 4 ,-4 4, суммирования (сигнал У 19), а также подача на вход 10 устройства следующей тетрады множителя.

На втором такте собственно умножения (третья микрокоманда) происходит перемножение очередной (второй ) тетрады множителя на тетрады множимого и одновременно с этим суммирование предыдущих тетрадных произведений в блоках ,, суммирования. В конце второго такта с разрешения сигнала У 20 в буферных регистрах 2,-2 , 3,-3, регистрах 5,-5 „ i Результата и триггерах 37 переноса блоков 4 - fnt-1 суммирования фиксируется промежуточная информация, а на входе IО устройства появляется значение сле - дующей (третьей) тетрады множителя.

Аналогичным образом устройство функционирует и в других тактах (микрокоманды с четвертой по ()-ю). В каждом такте с выхода 7 устройства считывается значение очередной тетрады младшей части результата.

После выполнения последнего ш-го такта собственно умножения (га+1)-я микрокоманда) в буферных регистрах

н запоминаются значения тетрадных произведений последней (самой старшей) тетрады множителя на все тетрады множимого,

При выполнении (т+2)-й микрокоманды происходит суммирование значений содержимого буферных регистров 2 -2 и соответствующими значениями регистров результата и триггеров 37 переноса блоков 4 -4 суммирования. С входа 10 устройства при этом на все входы множителя блоков 1,- f умножения подается нулевая тетрада, В конце такта образуемые на выходах блоков нулевые произведения запоминаются в буферных регистрах , и , а в регистра 5,-5 , результата и триггерах 37 переноса запоминается значение окон- чательного результата в двухрядном коде.

При выполнении (т+3)-й микрокоманды сигнал У 25 настраивает коммутаторы 38 переноса блоков , на пе- редачу информации через их первые входы,, тем самым выход переноса первого сумматора 33 оказывается соединенным с входом переноса первого сумматора 33 соседнего старшего блока суммирования. В результате этого значение содержимое триггеров 37 переноса п.)дсуммируется к содержимому соответствующих регистров 5 .езуль- тата через второй .вход первых сумма- торов 33 и двухрядный код произведения преобразуется к однорядному, при этом сигнал У 25 поддерживается в течение двух или более микрокоманд

После выполнения (т+3)-й и (т+4)-й микрокоманды в регистрах . результата будет находиться старшая часть окончательного произведения в однорядном коде. Младшая часть произведения уАе выведена через выход 17 устройства во время выполнения предыдущих микрокоманд. Первый 35 и вто рой 36 корректируюи;ие сумматоры блоков 4 ,-4 41 отсутствии сигнала У 2 настраиваются на передачу информации с входов на выходы без изменений.

Десятичное умножение выполняется в основном аналогично двоичному.

Отличие от двоичного умножения состоит в том, -Что в микрокомандах с второй до (тп+3)-й присутствует .дополнительный сигнал У 22, который настраивает блоки 1,-1 на умножение в десятичной системе счисления,

а корректирующие сумматоры 35-36 - на режим коррекции. Первый корректирующий сумматор 36 осуществляет вы- читание 6, когда выходной перенос сумматора 33 равен нулю. Второй корректирующий сумматор 36 производит прибавление 6, когда выходной перенос сумматора 34 равен единице.

Микропрограмма выполнения операции преобразования двоично-десятичного кода в двоичный изображена на фиг.5, Предполагается, что количество десятичных разрядов в преобразуемом операнде равно т. Преобразование заключается в вычислении произведений двоично-ьдесятичных тетрад разрядов преобразуемого числа на двоичные эквиваленты весов этих тетрад и суммировании полученных произведений.

По значению начального адреса микропрограммы, занесенного в счетчик 3 блока 9 управления, из памяти 40 в регистр 41 записывается значение первой микрокоманды, которой соответствуют :управляющие сигналы У 21 и У 23 а.

При выполнении первой микрокоманды по сигналу У 23, поступающему на вход блока 8 ,из него по адресу а выбирается двоичный эквивалент веса первой преобразуемой двоично-десятичной тетрады, который записывается с разрешения сигнала У 21 в регистры 6 .,-6 операнда. Наличие нулевого потенциала на выходе 24 блока 9 при этом обеспечивает настройку коммута- iTopOB 7, передачу информации на входы регистров выхода 33 блока 8 хранения смещенных эквива- .пентов. Одновременно на входе 0 устройства устанавливается значение самой младшей тетрады преобразуемого числа.

При выполнении второй микрокоманды происходит обнуление регистров 5,,-5 „.ц результата и триггеров 37 переноса блоков 4 -4 4 суммирования (сигнал У 10), в буферные регистры 2 f 2 и 3 ,3 ,„ записываются значения тетрадных произведений с. выходов блоков. -(сигнал У 20), а в регистры 6 1-6 ,„операнда (также как и в первой микрокоманде) заносится двоичный эквивалент веса второй преобразуемой тетрады (У 12 а+, У 21). Одновременно на входе 10 устройства появляется значение второй тетрады преобразуемого числа.

В третьей микрокоманде выполняется умножение второго двоичного эквивалента на значение второй тетрады и суммирование двоичных тетрадных произведений , которые получены на предыдущем такте и хранятся в буферных регистрах 2 ,-2 ,„ и Зд-3р,в блоках суммирования. Результаты тетрадных умножений в блоках „и суммирования в блоках ,, полученные в данном такте, запоминаются соответственно в буферных регистрах 2,-2„и 3,-3, а также в регистрах

10

данных микрокомандах распространяется через все блоки 4 -4 - суммирова ния, В конце выполнения микрокоманды результат преобразования в однорядном коде запоминается в регистрах „4 1 результата и в следующем так те может быть считан с выходов I7 и 18 устройства.

На фиг.6 изображена микропрограмма выполнения операции из двоичного кода в двоично-десятичный. Преобразо вание заключается в вычислении двоич но-десятичных произведений триаД дво

,, результата и триггерах 37 пе- 15 ичных разрядов преобразуемого числа реноса (сигнал У 20). По окончании вьтолнения данной микрокоманды на входе 10 устройства появляется значение следующей (третьей) тетрады прена двоично-десятичные эквиваленты их весов и суммировании полученных произведений. Поскольку в каждом такте работы обрабатываются три разряда

данных микрокомандах распространяется через все блоки 4 -4 - суммирования, В конце выполнения микрокоманды результат преобразования в однорядном коде запоминается в регистрах „4 1 результата и в следующем такте может быть считан с выходов I7 и 18 устройства.

На фиг.6 изображена микропрограмма выполнения операции из двоичного кода в двоично-десятичный. Преобразование заключается в вычислении двоично-десятичных произведений триаД двоичных разрядов преобразуемого числа

на двоично-десятичные эквиваленты их весов и суммировании полученных произведений. Поскольку в каждом такте работы обрабатываются три разряда

| название | год | авторы | номер документа |

|---|---|---|---|

| Вычислительное устройство | 1988 |

|

SU1545215A1 |

| Преобразователь двоично-десятичного кода в двоичный | 1985 |

|

SU1285604A1 |

| Множительное устройство | 1982 |

|

SU1053104A1 |

| Устройство для умножения | 1989 |

|

SU1668979A1 |

| Устройство для умножения чисел | 1989 |

|

SU1817091A1 |

| Устройство для умножения | 1985 |

|

SU1262484A1 |

| Устройство для умножения | 1983 |

|

SU1180881A1 |

| Устройство для умножения чисел | 1985 |

|

SU1259254A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Множительное устройство | 1982 |

|

SU1116427A1 |

Изобретение относится к вычислительной технике и может быть применено для быстрого выполнения операций умножения и преобразования чисел из двоичной системы счисления в десятичную и обратно. Особенно эффективно его использование в качестве основы при разработке быстродействующих арифметических устройств универсальных ЭВМ, работающих как с двоичными, так и с десятичными числами. Целью изобретения является повышение быстродействия и расширение функциональных возможностей устройства за счет операций преобразования чисел из двоичной системы счисления в десятичную и обратно. Устройство содержит блоки умножения, блоки суммирования, регистры операнда, регистры результата, микропрограммный блок управления и введенные буферные регистры первой и второй групп, коммутаторы, блок хранения смешенных эквивалентов. С помощью введенных блоков и связей обеспечивается положительный эффект, заключающийся в повышении быстродействия в 7,7 раз по сравнению с известным и возможности выполнять не только операции умножения с двоичными и десятичными числами, но и операцию преобразования чисел из двоичной системы счисления в десятичную и обратно. 6 ил.

образуемого числа, а в регистры двоичного операнда, то разрядность

операнда заносится двоичный эквивалент веса третьей преобразуемой тетрады (У 23 а+2, У 21).

Затем выполняются (т+3) микрокоманды, каждая из которых отличается от третьей только другим значением адреса двоичного эквивалента. После выполнения т-й микрокоманды в регистрах .„ операнда запоминается знаоперанда, который может быть преобразован в устройстве, состоящем из блоков 1 умножения, равна 3т, что и предполагается.

25 Ио значению начального адреса ми ропрограммы, занесенного в счетчик 39 блока 9 управления, из памяти 40 в регистр 41 микрокоманд записывает значение первой микрокоманды, коточение последнего т-го двоичного экви- зо Р соответствуют управляющие сигнавапента.

При выполнении (т+1)-и микрокоманды в блоках 4,-4, суммируется содержимое /регистров 5 ,-5 , резу тьтата триггеров 37 переноса и содержащихся в буферных регистрах 2 ,-2 ,„и 3 ,-3 значений тетрадных произведений последнего т-го двоичного эквивалента на последнюю преобразуемую тетраду.

После выполнения данной микрокоманды в регистрах 5,-5, триггерах 37 переноса запоминается окончательный результат в двухрядном коде ;(сигнал У 20). На последних (т+2)-й и (т+3)-и микрокомандах осуществляется приведение двухрядного кода к однорядному. Как и при умножении сигнал У 25 настраивает коммутаторы 37 переноса блоков суммирования на передачу информации с их первых входов. При этом образуется цепь из последовательно соединенных первых сумматоров 33 блоков 4 ,- 4 суммирования. В каждом из блоков

35

40

45

50

лы У 21 и У 23 в. При выполнении первой микрокоманды под воздействием этих управляющих сигналов осуществляется занесение в регистры операндов первого двоично-десятичного эквивалента аналогично, как и в операции преобразования из двоично- десятичного кода в двоичный.

В колце этого такта на входе 10 устройства появляется значение тетрады, три младших разряда которой являются самыми младшими раз.рядами преобразуемого двоичного числа, а значение старшего разряда устанавливается равным нулю.

При выполнении второй микрокоманды происходит обнуление регистров 5,-5 4.1 результата и триггеров 37 переноса блоков 4 ,-4 „,+, суммирования (сигнал У 19) в блоках 1,-1, которые настраиваются на умножение в двоично-десятичных кодах, выполняется умножение первого двоично-десятичного эквивалента на значение первой триады

,„, суммирования значение тригге- gg и в буферные регистры 2-, 3 ,-3,„зара 37 переноса поступает через второй сумматор 36 и второй корректирую- рщй сумматор 34 на второй вход перво- го сумматора 33. Сквозной перенос в

двоичного операнда, то разрядность

операнда, который может быть преобразован в устройстве, состоящем из m блоков 1 умножения, равна 3т, что и предполагается.

Ио значению начального адреса ропрограммы, занесенного в счетчик 39 блока 9 управления, из памяти 40 в регистр 41 микрокоманд записывается значение первой микрокоманды, кото5

0

5

0

лы У 21 и У 23 в. При выполнении первой микрокоманды под воздействием этих управляющих сигналов осуществляется занесение в регистры операндов первого двоично-десятичного эквивалента аналогично, как и в операции преобразования из двоично- десятичного кода в двоичный.

В колце этого такта на входе 10 устройства появляется значение тетрады, три младших разряда которой являются самыми младшими раз.рядами преобразуемого двоичного числа, а значение старшего разряда устанавливается равным нулю.

При выполнении второй микрокоманды происходит обнуление регистров 5,-5 4.1 результата и триггеров 37 переноса блоков 4 ,-4 „,+, суммирования (сигнал У 19) в блоках 1,-1, которые настраиваются на умножение в двоично-десятичных кодах, выполняется умножение первого двоично-десятичного эквивалента на значение первой триады

писываются значения тетрадных двоично-десятичных произведений (сигнал У 20 ), а в регистры 6 ,-6 операнда, также как и в первой микрокоманде,

заносится двоично-десятичный эквивалент веса второй триады разрядов преобразуемого числа. Само же значение этой триады с присоединением слева нулевым разрядом подается в конце данного такта на вход 10 устройства,

В третьей микрокоманде выполняется умножение второго эквивалента на значение второй триады и суммирование двоично-десятичных тетрадных произведений, которые получены на предыдущем такте и хранятся в буферных регистрах 3, блоках 4 ,-4 „, суммирования, настроенных управляющим сиг- налом У 22 на работу в двоично-десятичном коде. Результаты тетрадных умножений .в блоках ,и суммирования в блоках , полученные в данном такте, запоминаются соответственно в буферных регистрах к 3,-3,, а также регистрах , результата и триггерах 37 переноса (сигнал У 20) По окончании выполнения данной микрокоманды на входе 10 устройства появ- ляется значение третьей триады преобразуемого числа.

Затем выполняются (tr+3) микрокоманды, каждая из которых отличается от третьей только другим значением адреса двоично-десятичного эквивалента. После выполнения т-й микрокоманды в регистрах 6, операнда запоминается значение последнего т-го двоично-десятичного эквив.алента,

При выполнении (т+1)-и микрокоманды в блоках ,суммируется содержимое регистров 5 -,-5 результата, триггеров 37 переноса блоков . 1 «41 тетрадных произведений по- среднего двоично-десятичного эквивалента на соответствующую преобразуемую триаду (управляю11ц й сигнал У 22 настраивает блоки li-lmH на обработку двоично-десятичного ко- да), По окончании такта в регистрах 5,-5 П1-И и триггерах 37 блоков 4 ,-4 суммирования запоминается окончательный результат в двухрядном коде (сигнал У 20).

На последних (т+2)-й и (т+3)-й микрокомандах двухрядный код приводится к однорядному -точно также, как это делалось при выполнении операций умножения и преобразования в двоичный код, В конце выполнения (т+3)-й микрокоманды результат преобразования записывается в регистры результата и в следующем

такте может быть считан с выходов 17 и 18 устройства.

Формула изобретения

Устройство для умножения, содер- жащее та блоков умножения (, где п - разрядность операндов), m блоков суммирования, каждый из которых содержит первый и второй сумматоры, m регистров операнда и т+1 регистров результата, причем выход i-ro регистра операнда (,2,,,,,т) соединен соответственно с входом множимого i-ro блока умножения, вход множителя которого соединен с входом множителя устройства выход К-го регистра результата (,2,,,,,т-1) соединен соответственно с входом первого слагаемого первого сзгмматора (К+1)-го блока суммирования, отличающ ё е с я тем, что, с целью повышения быстродействия и расширения функциональных возможностей за счет выполнения операции преобразования чисел из двоичной системы счисления в десятичную и обратно, в него введены две группы по ю буферных регистров, m коммутаторрв, блок хранения смещенных эквивалентов, микропрограммный блок управления, (га+О-й блок суммирования, причем каждый из га+1 блоков суммирования дополнительно содержит два корректирующих сумматора, триггер переноса и коммутатор переноса, первый информационный вход которого соединен с выходом переноса первого сумматора, входом переноса первого корректирующего сумматора и информационным входом триггера переноса, выход которого соединен с входом переноса второго сумматора, выход суммы которого соединен с информационны входом второго корректирующего сумматора, выход которого соединен с входом второго слагаемого первого сумматора, выход суммы которого соединен с информационным входом первого корректирующего сумматора, выход переноса второго сумматора соединен с . зходом переноса второго корректирующего сумматора и вторым информационным входом коммутатора переноса, управляющий вход которого соединен с первым выходом микропрограммного блока управления, второй выход которого Iсоединен с управляющими входами т коммутаторов, первый информационный

вход 1-го коммутатора соединен с выодом соответствующих разрядов блока хранения смещенных эквивалентов, адресный вход которого соединен с третьим выходом микропрограммного блока управления, вход которого соединен с входом начального адреса устройства, входы соответствующих разрядов множимого которого соединены с вторыми информационными входами m коммутаторов, выход i-ro коммутатора соединен с информационным входом i-ro регистра операнда, вход разрешения записи кот орого соединен с четвертым выходом микропрограммного блока управления, пятый выход которого соединен с входами выбора режима работы m блоков умножения и входами разрешения коррекции первых и вторых корректирующих сумматоров (т+) блоков суммирования , выходы старшей и младшей частей произведения i-ro блока умноения соединены соответственно с информационными входами i-x буферных регистров первой и второй групп, вхо- ы разрешения записи которых соединены с входами разрещения записи триггеров переноса т+1 блоков суммирования, т+1 регистров результата и шестым выходом микропрограммного блока управления, седьмой выход которого соединен с входами сброса триггеров переноса m+l блоков суммирования и m+I регистров результата, информационный вход J-го регистра результата

(j ) ,2,... ,т-ь1 ) соединен соответственно с выходом первого корректирующего сумматора j-ro блока суммирова ния, вход первого слагаемого второго сумматора i-ro блока суммирования соединен соответственно с выходом i-ro буферного регистра первой группы, выход i-ro буферного регистра

0 второй группы соединен соответствей- но с входом второго слагаемого второго сумматора (i+l)-ro блока суммирования, вход второго слагаемого второго сумматора первого блока суммиро5 вания соединен с входом первой константы устройства, вход второй константы которого соединен с входом первого слагаемого второго сумматора ()-го блока суммирования, вход

0 переноса первого сумматора i-ro блока суммирования соединен соответственно с выходом коммутатора переноса (i+l)-ro блока суммирования, входы первого слагаемого и переноса первого

5 сумматора (т+1)-го блока суммирова- . ния соединены соответственно с выходом т-го регистра результата и, входом нулевого потенциала устройства, вход первого слагаемого первого сумматора

0 первого блока суммирования соединен с входом коррекции устройства, выходы m регистров результата соединены . с выходами старшей части результата устройства, выход младшей части ре- .

5 зультата которого соединен с выходом (т+1)-го регистра результата.

2

2

2

j.t

,,J

2(8

iCJ

0001

0100

Кч

t

У 21.

I yj9.

У19, У 20

гЗ

да

фиаЛ

Ml

JL

Фиг.З

г-1

у21 т

JL

Ш.у 20. у 22

г5У20. У 22

Фиг. 5

Г.

УГ/

tis-а

rZ-Ж.

yi3.yzo.nzi yZ3

г J j/го, У2;

L

т n0.ii21

yiZ a-tm l

y

.w

yZ5

ж

y, y/5гГ

nf-SL

т.т.шш

ж

mifzim

I y/J i

т

I j/

/П./Ж.

У20. угг

2Ж

Иг2.У25

r/nTSE

у20.i/22.25

Фиг.6

| Множительное устройство | 1982 |

|

SU1116427A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Десятичное множительное устройство | 1972 |

|

SU468239A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1989-07-23—Публикация

1987-09-07—Подача