123

Изобретение относится к электроизмерительной технике,

Цель изобретения расширенае функциональных, возможностей путем обеспечения преобразования сигналов s обеих полярностей.

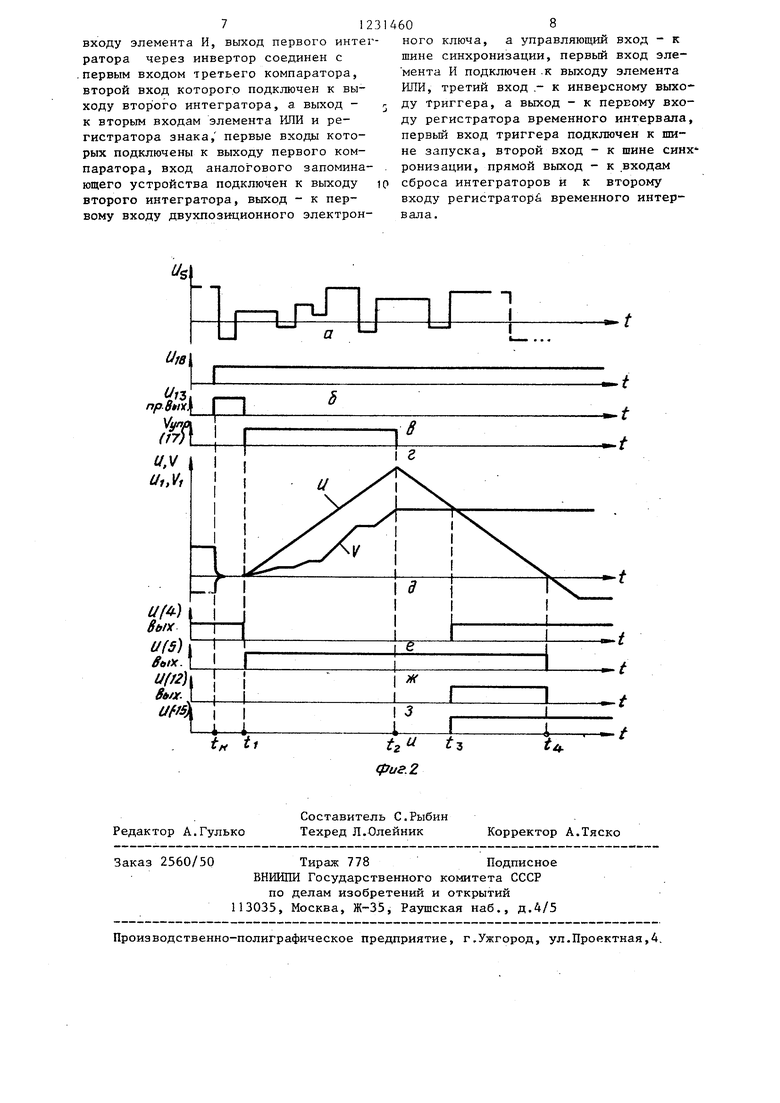

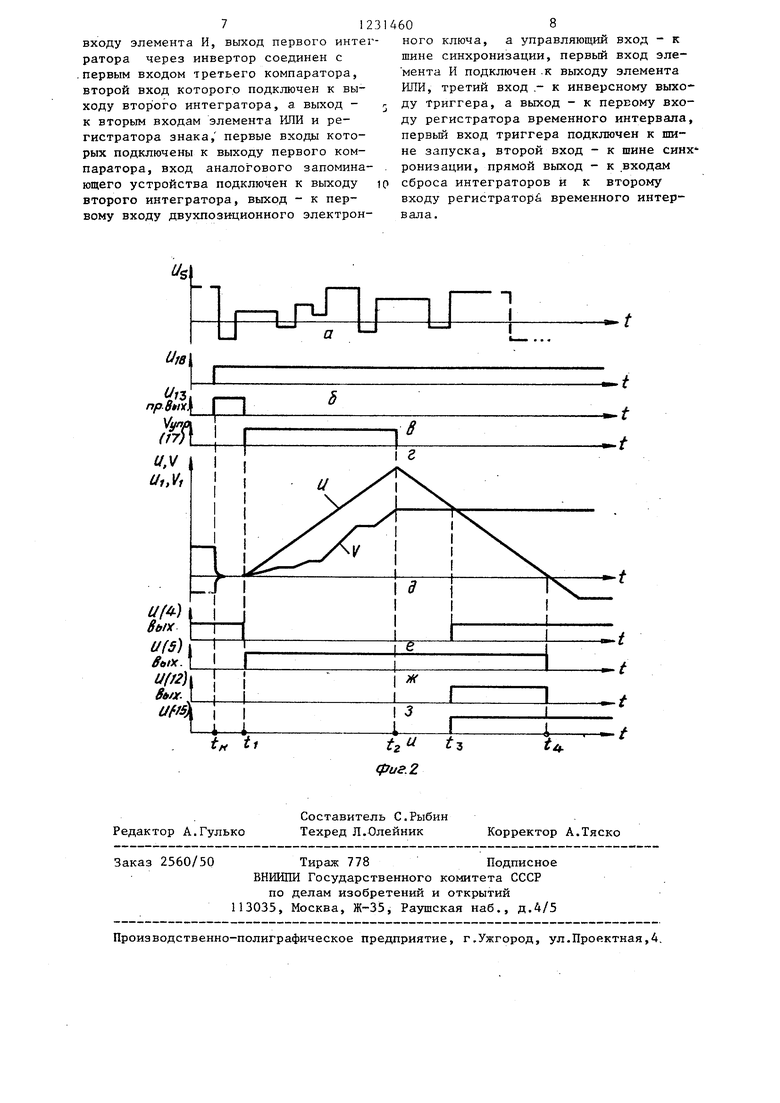

На фиг. 1 представлена блок-схема преобразователя; на фиг, 2 - временные диаграммы, поясняющие его работу.

Преобразователь содержит первьш HI интегратор , второй интегратор 2, источник 3 опорного напряжения, под- ключенньш к общей шине, первый компаратор 4, первьш вход которого подключен к выходу интегратора 1, второй IS вход - к выходу ннтегратора 2, второй компаратор 5, первый вход которого подключен к общей шине, второй вход - к выходу интегратора 2 и к второму входу третьего компаратора 6, ана- 20 логовое запоминающее устройство 7, вход которого соединен с ыходом интегратора 2, входной электронный ключ 8, выход которого соединен с

4602

вход устройства 7, конденсатор 19 подключен между выходом ключа 20 и общей шиной,

Преобразователь работает следую щим образом,

В исходном состоянии на шине 17 синхронизации и шине 18 запуска ус тановлены напряжения- нулевого уров ня ,

Б результате этого электронный ключ 9 находится в первом состояни при котором его выход скоммутирой с первым информационным входом 1п (фиг,, 1), Электронный ключ 8 разомк нут ,

В момент времени t, характеризующий конец стадии подготовки к измерению, на шину 18 запуска пос тупает сигнал уровня логической ед ницы (фиг,2S)5 который подается на первый вход триггера 13,

При этом триггер 13 взводится и с момента t на его прямом выходе устанавливается уровень логической

входом интегратора 1, двухпозиционный единицы (фиг, 2&), поступающий -на

электронный ключ 9, первый вход которого соединен с выходом устройства 7, второй вход - с выходом источника 3, а выход - с входом интегратора 2, инвертор 10, включенный между выходом интегратора 1 и первым входом компаратора 6, элемент ИЛИ 11, первый вход которого подключен к выходу компаратора 4, второй вход - к выходу компаратора 6, а выход - к первому входу элемента И 12, второй вход которого соединен с выходом компаратора 5, третий вход - с инверсным выходом триггера 13, а выход - с первым входом регистратора 14 временного интервала, второй вход которого подключен к прямому выходу триггера 13 и к входам сброса интеграторов 1 и 2, регистратор 1 знака, первый вход которого подключен к выходу компаратора 4, второй вход - к выходу компаратора 6, вход ключа 8 соединен с входной шиной 16, управляющие входы ключей 8 и 9 и устройства 7, а также второй вход триггера 13 соединены с шиной 17 синхронизации, первый вход триггера 13 соединен с шиной 18 запуска.

Анало1-овое запомин;1ющее устройство 7 выполнено на конденсаторе 19 и ключе 20, вход, выход и управляющий вход ключа 20 образуют соответственно вход, выход и управляющий

602

вход устройства 7, конденсатор 19 подключен между выходом ключа 20 и общей шиной,

Преобразователь работает следующим образом,

В исходном состоянии на шине 17 синхронизации и шине 18 запуска установлены напряжения- нулевого уровня ,

Б результате этого электронный ключ 9 находится в первом состоянии, при котором его выход скоммутиройан с первым информационным входом 1п (фиг,, 1), Электронный ключ 8 разомкнут ,

В момент времени t, характеризующий конец стадии подготовки к измерению, на шину 18 запуска поступает сигнал уровня логической единицы (фиг,2S)5 который подается на первый вход триггера 13,

При этом триггер 13 взводится и с момента t на его прямом выходе устанавливается уровень логической

входы сброса интеграторов 1 и 2 и регистратора 14 временного интервала. В результате этого выходные напряжения интеграторов сбрасываются до нулевого уровня, а показание индикатора 14 обнуляется,

В момент времени t на шину 7 синхронизации устройства подается управляющий импульс уровня логической

единицы (фиг.2), который поступает на управляющие входы электронных ключей 3 и 9, аналогового запоминающего устройства 7-, а также на второй вход, триггера 13, В течение дейстВИЯ управляющего импульса длительностью Т t -- t, ,электронный ключ 9 с момента t. переключается во второе состояние, при котором его вьпсод соедк1няется с его вторым информационным входом 2п, электронный ключ 8 замьжается, в результате чего информационный вход интегратора I подключается к входной шине 16 устройства, а триггер 13 с момента t сбрасывается, от чего уровни напряжения на его выходах меняются на противоположные (фиг,2&,. момент t, ). Под действием сигнала на управляющем входе аналоговое запоминающее устройство 7 обеспечивает равенство потенциалов на первом информационном входе электронного ключа 9 и на выходе интегратора, 2.

Состояния сброса с интеграторов

1и 2 и регистратора 14 снимаются.

При этом с момента t, , исследуемый сигнал Vg , поступая с входной шины 16 устройства на вход интегратора 1, интегрируется последним, в результате чего напряжение на выходе интегратора изменяется согласно

Vt , t

llvt (1)

-t.

где f - постоянная интегрирования

интегратора 1;

t - время, отсчитанное от момента t ,. Напряжение на выходе интегратора

2с момента t изменяется линейно (фиг.2а)-в соответствии с выражением

i.+t

€Я .

(2)

-t.

где с - постоянная интегрирования

интегратора 2;

и - величина напряжения источника опорного напряжения 3.

Напряжение с выхода интегратора

1поступает на вход компаратора 4 и череа инвертор 10 - на вход компаратора 6.

Напряжение с выхода интегратора

2поступает на вторые входы компараторов 4, 5 и 6.

При выполнении условий

Ue,n UBX,

(3)

на выходах компараторов 4 и 6 появляется напряжение уровня логического нуля (фиг.2е), а на выходе компаратора 5 - напряжение уровня логической единицы..

По окончании действия управляющего импульса на шине 17 устройства, а следовательно, и на управляющих входах электронных ключей 8 и 9 аналогового запоминающего устройства 7 в момент tg , электронный ключ 9 с момента t п ереключается в первое состояние, электронный ключ 8 кается, а аналоговое запоминающее устройство 7 переводится в режим хранения выходного напряжения, что обеспечивается размыканием электронного

ключа 20. При этом потенциал конденсатора 19 сохраняется неизменным.

В момент t напряжение V на выходе интегратора 1 равно значению ин- теграла напряжения сигнала Vg за время усреднения

V(t,) j/VgJt -K.- V,

(4)

1

О где К, ;г - коэффициент пропорциональности;

Vw I V,Jt. It J 6 о

(5)

5 Напряжение U на выходе интеграто- ра 2 в момент t определяется величиной

20

.- ) fJUo«Jt l7

2

-t,

Uo

где К коэффициент пропор циональности.

С момента t напряжение интегратора

2 изменяетсясогласно

U() U(t-) - A(t - t,), (7)

где

A - U(ts.l

A л л.

(8)

В момент tj напряжения на входах компаратора 4 сравниваются

vct,,-) u(t) uct,,) - )

(9)

в последующие момент времени напряжение на его выходе устанавливается равным уровню логической единицы и поступает на вход элемента ИЛИ 11 и первый вход регистратора 15 знака. При этом на выходе элемента/ИЛИ 11 и

с момента t формируете напряжение уровня логической единицы, поступающее на вход элемента И J2, на выходе которой с момента t формируется импульс напряжения уровня логической

единицы (так как на втором и третьем входах этой схемы действуют импульсы напряжения уровня логической единицы соответственно с выхода компаратора 5 НС инверсного триггера 13),

который поступает на информационный вход регистратора 14 временного интервала. Напряжение интегратора 2 после момента t продолжает линейно

уменьшаться и в момент времени t напряжения на входах компаратора 5 сравниваются

V(tJ О U(t,)-- A-(t 4 - t),

(to)

в последующие моменты времени напряжение на выходе компаратора 5 устанавливается уровнем логического нуля. В результате с момента t на выходе схемы И 12 устанавливается напряжение уровня логического нуля.

При этом длительность сформированного на выходе схемы И 12 импульса напряжения

.

- f- - -Э

(П)

зафиксированного регистр атором 1 4 временного интервала, определяет величину, пропорциональную среднему значению сигнала за время усреднения Т, что вытекает из следующего. Момент времени t определяется из решения уравнения (10)

U(tp A-(t - t,),

t У(t.l . t4 A + Ч(12)

Момент времени t определяется решением уравнения (9)

-3

тогда

VCt) -U(t) A.(t, -Ц),

t Yit.).

A A

t t - t t -n-iM, L C,j

yit.) + Ylt) .

TL,, ,

,

где В - масштабный коэффициент, определяемый выражением

,2

В 1- . ги

(15)

Отсюда следует, что длительность импульса напряжения, сформированного с момента t, н-а выходе элемента

О

5

5

0

5

И 12, пропорциональна среднему значению сигнала Vg за время усреднения Т.

С момента t и в течение всего послед- дош,его времения на первьш вход регистратора 15 знака поступает импульс напряжения уровня логической единицы (фиг.2е). При этом на регистраторе 15 высвечивается с момента t знак +, что соответствует положительной величине определенного устройством среднего значения сигнала Vg.

Масштаб выходных напряжений интеграторов 1 и 2 выбирается из наступления условий V и к моменту времени t .

Инвертор 10 и компаратор 6 обеспечивают работоспособность устройства при условии, что к моменту t напряжение на выходе интегратора (т.е. . интеграл напряжения сигнала V) имеет отрицательное значение. При этом на регистраторе 5 высвечивается знак что соответствует отрицательной величине среднего значения сигнала.

Формула изобретения

Усредняюш,ий преобразователь, со- держащи:й первый интегратор, вход которого соединен с входной шиной через входной электронный ключ, а выход подключен к первому входу первого ком1 :аратора, второй интегратор, вход кс торого соединен с ВЬЕХОДОМ двух- позиционного электронного ключа, а вых.од - с вторым входом первого компаратора, источник опорного,напряжения, выход которого соединен с вторым входом двухпозиционного электронного ключа, управляющие входы электронных ключей подключены к шине синхронизации, входы сброса интеграторов объединены, отличающий- с я тем, что, с целью расширения функциональных возможностей путем обеспечения преобразования сигналов обеих полярностей, в него введены второй и третий компараторы, аналоговое запоминаюш,ее устройство, инвертор, элемент ИЛИ, элемент И, триггер, регистратор временного интервала и регистратор знака, первый вход второго компаратора подключен к общей шине, второй вход - к выходу второго интегратора, а выход - к второму

входу элемента И, выход первого интегратора через инвертор соединен с .первым входом третьего компаратора, второй вход которого подключен к выходу второго интегратора, а выход - к вторым входам элемента ИЛИ и регистратора знака, первые входы которых подключены к выходу первого компаратора, вход аналогового запоминающего устройства подключен к выходу второго интегратора, выход - к первому входу двухпозиционного электронI-LrMJ -

8

ггюного ключа, а управляющий вход - к шине синхронизации, первый вход эле- мента И подключен .к выходу элемента ИЛИ, третий вход .- к инверсному выходу Триггера, а выход - к первому входу регистратора временного интервала, первый вход триггера подключен к шине запуска, второй вход - к шине ронизации, прямой выход - к входам сброса интеграторов и к второму входу регистратора временного интервала.

t

Ul8

3 пр.Вн Х,

UflSj

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор | 1988 |

|

SU1728871A1 |

| СПОСОБ ИЗМЕРЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ ПРОИЗВОЛЬНОЙ ФОРМЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1990 |

|

RU2034302C1 |

| Способ измерения среднего значения напряжения произвольной формы и устройство для его осуществления | 1983 |

|

SU1150561A1 |

| Способ определения деформаций лопаток рабочего колеса турбомашины и устройство для его осуществления | 1989 |

|

SU1749748A1 |

| Цифровой регистратор повторяющихся сигналов | 1987 |

|

SU1610279A1 |

| Аналоговый интегратор | 1983 |

|

SU1128271A1 |

| Генератор пилообразного напряжения с переменной крутизной | 1987 |

|

SU1495982A1 |

| ЦИФРОВОЙ РЕГИСТРАТОР ПЕРЕХОДНЫХ ПРОЦЕССОВ | 1990 |

|

RU2029310C1 |

| РЕГУЛЯТОР ТЕМПЕРАТУРЫ | 2010 |

|

RU2431177C1 |

| Устройство для измерения средних значений нестационарных сигналов | 1985 |

|

SU1347028A1 |

Изобретение относится к электроизмерительной технике. Цель изобретения - расширение функциональных возможностей путем преобразования сигналов обеих полярностей. Устройство содержит интеграторы 1 и 2, источник 3 опорного напряжения, первый компаратор 4, входной ключ 8, двухпозиционный электронный ключ 9, входные шины 16 и шины 17 синхронизации . Для достижения поставленной цели в него дополнительно введены, . второй и третий компараторы 5 и 6, аналоговое запоминающее устройство 7, инвертор 10, логические элементы ИЛИ 11 и И 12, триггер I3, регистр 14 временного интервала и регистр 15 знака. Инвертор 10 и компаратор 6 обеспечивают работоспособность устройства при условии, когда на выходе интегратора 1 формируется отрицательное напряжение. При этом на ре- гистраторе 15 отображается знак - что соответствует отрицательной величине среднего сигнала. Ил. 2. с S . (Л

Редактор А.Гулько

Составитель С.Рыбин Техред Л.Олейник

2560/50

Тираж 778Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д.А/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная,4.

Корректор А.Тяско

| Справочник по нелинейным схемам/ Под ред | |||

| Д.Шейнголда | |||

| М.: Мир, 1977, с.116-117, фиг | |||

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для выделения постоянной составляющей переменного напряжения | 1982 |

|

SU1167512A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

Авторы

Даты

1986-05-15—Публикация

1983-09-27—Подача