(54) УСТРОЙСТВО ДЛЯ ОПРЕДЕЛЕНИЯ ДИСПЕРСИИ

I

Изобретение относится к цифровоЯГ вычислительной технике и может быть использовано при ангшизе случайшах величин.

Известно устройство, предназна-ченное для вычисления дисперсий случайных величин, построенное на базе квадраторов, счетчиков-делителей и счетных регистров, содержащее блок входной информации, соединенный с входом счетчика выборки, счетчик среднего арифметического, счетчик среднего квадратов, а также квадраторы, при этом выход блока входной информации через первый квадратор подключен к первому аходу счетчика среднего квгщратов и счетчик среднего ад ифметического и второй квадратор - ко второму входу счетчика среднего квадратов, а выход счетчика выборки подключен к соответствующему входу второго квсщратора ilj.

наиболее близким к предлагаемому является УСТРОЙСТВО пля опрепеления дисперсии, содержащее блок управления, выход которого подключен к первому входу арифметического блока 2.

Известные устройства реализуют вычисление дисперсии только по достижении некоторого лаперед заданного объема кл&оркн в остальных же дисперсия рассчитывается в два этапа: предвефительйо по выборке некоторого объема определяется математическое ожидание случайной величины и лишь по новой выборке рассчитывается дисперсия.

Цель изобретения - расширение

to функциональных возможностей устройства для определения дисперсии Сза счет г«апиза нестационарных случайных процессов}.

Поставленная; цель достигается тем,

15 что в устройство для определения дшсперсии введе(1Ы счетчик замеров, три регистра, два буферных регистра, пять блоков элементов И, два блока элементов ИЛИ, при этом выход блока управления подключен к первому вхо20ду первого блока элементов И, второй вход которого является первым входом устройстда,выход первого блока элементов И через первый регистр

25 соединен с первыми входами . первого и блоков элементов ИЛИ, выходы- которых поключены соотв тртвенно ко второ му и третьему входам арифметического вло30 ка, первый выход которого соедаV

нен с первыми входами второго, третьего, четвертого и пятого блоков элементов И, вторые входы которых объединены и подключены к выходу блока управления, выход генератора импульоов соединен с первым входом блока управления и четвертым входом арифметического блока, второй выход которого подключен ко второму входу блока управления, третий вход которого является вторым входом устройства, выход блока управления соединен со входом счетчика аамеров, выхо которого подключен ко второму входу второго блока элементов ИЛИ, третий вход которого объединен со вторым входом первого блока элементов ИЛИ и соединен с выходом первого буферного регистра, вход которого подключен к выходу второго блока регистра, вход которого подключен к выходу второго блока элементов И, выход третьего блока элементов И через второй регистр соединен с третьим входом первого блока элементов ИЛИ, четвертый вход которого подключен к выходу третьего регистра, вход которого соединен с выходом четвертогоблока элементов И, выход пятого блока элементов И через второй буферный регистр подключен к четвертому входу второго блока элементов ИЛИ, . пятый вход которого объединен с пятым.входом первого блока элементов ИЛИ и соединен с выходом блока управления.

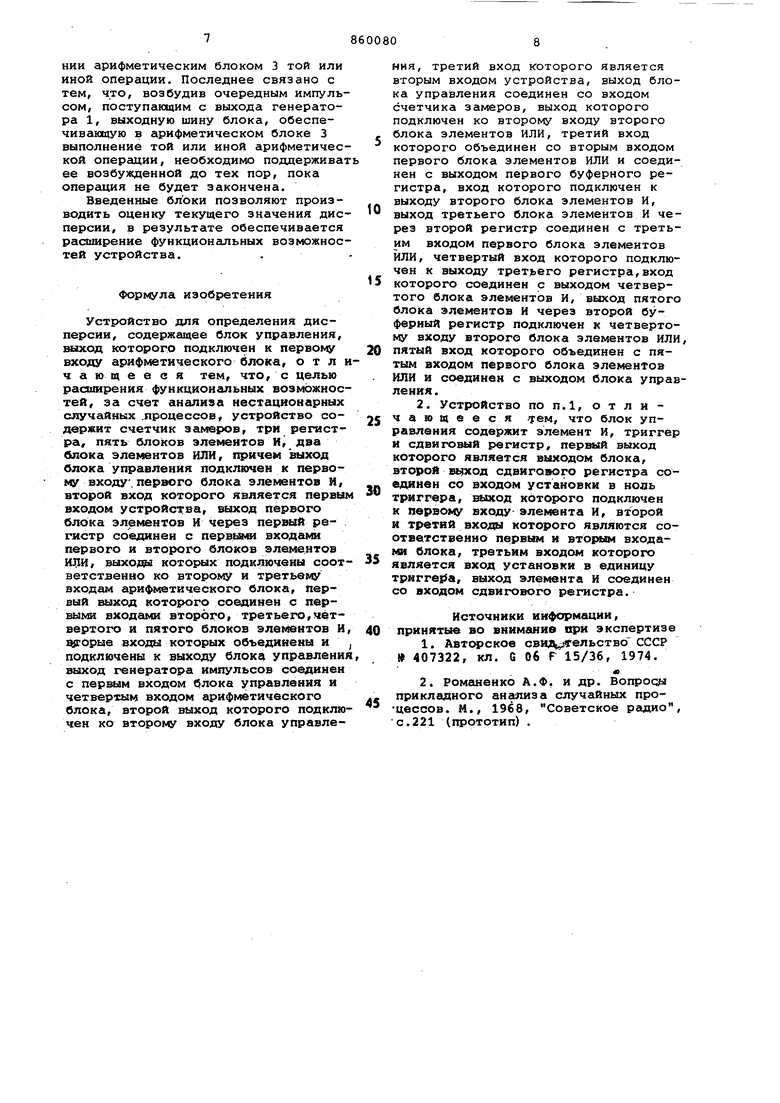

Кроме того, блок управления содержит элемент И, триггер и сдвиговый регистр, первый выход которого является выходом блока, второй выход сдвигового регистра соединен со вхъд установки в ноль триггера, выход которого подключен к первому входу элемента И, второй и третий входы которого являются соответственно первым и вторым входами блока, третьим входом которого является вход устанойки в единицу триггера, выход элемента И соединен со входом сдвигового регистра.

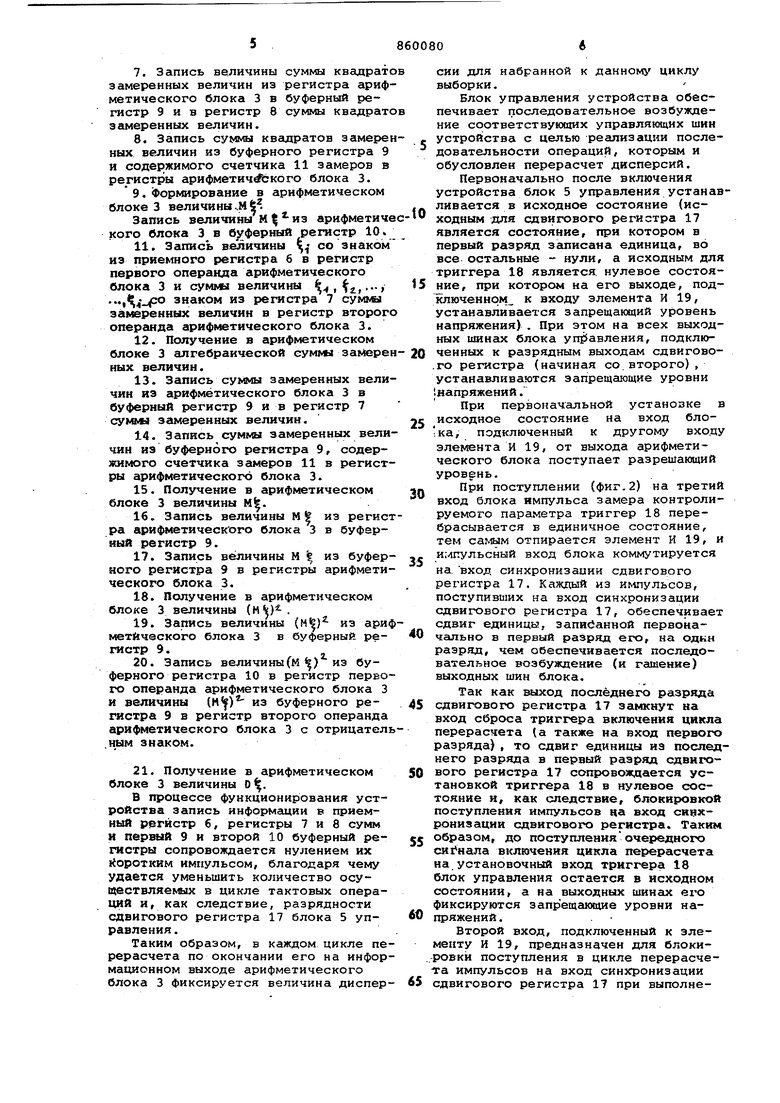

Ёлок-схема устройства и блока ,управления представлены на фиг.1 и фиг.2.

Устройство содержит генератор 1 импульсов, первый блок 2 элементов или, арифметический блок 3, второй блок (4 элементов ИЛИ, блок 5 управление, первый, второй и третий регистры 6,7 и. 8, первый второй буферные регистры 9 и 10, счетчик 11 замеров, первый, второй, третий, четвертый и пятый блоки 12, 13,14, 15..и 16 элементов И. Блок управления (фиг.2) содержит сдвиговый регистр 17, триггер 18 и элемент И 19.

Устройство работает слепукаугм образом,

Дисперсия вычисляется в соответствии с выражением

(

где символами ЛЭ и М обозначены соответственно дисперсия и математическое ожидание, причем

.,

где И - количество произведенных к

данному моменту замеров; Ф - реализация случайного параметра § при 4-ом замере.

Первоначально регистры 7 и 8 сумм соответственно замеренных величин и квадратов замеренных величин, арифметический: -блок 3, а также счетчик Ц замеров устанавливаются в исход- . ное (нулевое состояние. На втором выходе арифметического блока 3, соеjopiiHeHHOM со входом блока управления, устанавливается разрешакяций уровень. Одновременно устанавливается в исходное состояние и блок 5 управления, при этом на управляющих входах всех узлов устройства, подключенных к выходным шинс1м блока управления, устанавливаются запрещающие уровни напряжений.

При поступлении на третий вход блока управления очередного замера контролируемой величины включается блок 5 управления,тем самым обеспечивается последовательное возбуждение и гашение) его выходных 1ин,способст|Вукадее реализации цикла перерасчета дисперсии, по окончании цикла пёрёрасчета блок 5 управления вновь устанавливается в исходное состояние до прихода очередного импульса.

В каждом цпкле перерасчета дисперсии в устройстве реализуется приводимая ниже последовательность действий, (всё передачи чисел осуществляются в параллельном коде).

1.Прием в прямом коде со знаком в приемный регистр 6 и увеличение содержимого счетчика 11 замеров на единицу.

2.Запись величины - иэ, приемного регистра 6 в регистры арифгдетического блока 3 через блоки 2 и 4.

3.Формирование в арифметическом блоке 3 величины - .

4.Запись величины яз арифметического блока 3 в буферный регистр 10

5.Запись из буферного регистра 9 в регистр первого операнла аои(1 тического блока 3 и суммы из регистра 8 суммы квадратов в регистр второго операнда арифметического блока 3.

6.Получение в .регистре результата арифметического блока 3 суммы квадратов замеренных величин.

7.Запись величины сумкм квадрато замеренных величин из регистра арифметического блока 3 в буферный регистр 9 и в регистр 8 суммы квещрато замеренных величин.

8.Запись суммы квещратов замеренных величин из буферного регистра 9

и содержимого счетчика 11 замеров в регистры арифметич кого блока 3.

9.Формирование в арифметическом блоке 3 величины..

Запись величины арифметиче кого блока 3 в буферный регистр Ю.

11.Запись величины , со знаком из приемного регистра 6 в регистр первого операнда арифметического

блока 3 и суммы величины ,г,.., , знаком из регистра 7 сумкы замеренных величин в регистр второго опергшда арифметического блока 3.

12.Получение в арифметическом блоке 3 алгебраической сумкл замерен ных величин.

13.Запись суифол замеренных величин из арифметического блока 3 в буферный регистр 9 и в регистр 7

суювл замеренных величин.

14.Запись СУМ1МЫ замеренных величин из буферного регистра 9, содержимого счетчика замеров 11 в регистры арифметического блока 3.

15.Получение в арифметическом блоке 3 величины М.

16.Запись величины М из регистра арифметического блока 3 в буферный регистр 9.

17.Запись величины М из буферного регистра 9 в регистры арифметического блока 3.

18.Получение в арифметическом блоке 3 величины (н).

19.Запись величины (М) из арифметического блока 3 в буферный регистр 9.

20.Запись величины(М ) из буферного регистра 10 в регистр первого операнда арифметического блока 3

и величины (М) из буферного регистра 9 в регистр второго операнда арифметического блока 3 с отрицатель.ным знаком.

21.Получение в арифметическом блоке 3 величины О .

В процессе функционирования устройства запись информации в приемный регистр б, регистры 7 и 8 сумм и первый 9 и второй 10 буферный регистры сопровождается нулением их Коротким импульсом, благодаря чему удается уменьшить количество осуществляемых в цикле тактовых операций и, как следствие, разрядности сдвигового регистра 17 блока 5 управления.

Таким образом, в каждом цикле перерасчета по окончании его на информационном выходе арифметического блока 3 фиксируется величина дисперсии для набранной к данному циклу выборки.

Блок управления устройства обеспечивает последовательное возбуждение соответствующих управляющих шин устройства с целью -реализации последовательности операций, которым и обусловлен перерасчет дисперсий.

Первоначально после включения устройства блок 5 управления устанавливается в исходное состояние (исходным для сдвигового регистра 17 является состояние, при котором в первый разряд записана единица, во все остёьльные - нули, а исходным для триггера 18 является, нулевое состояние, при котором на его выходе, подТслюченнрм к входу элемента И 19, устанавливается запрещающий уровень напряжения). При этом на всех выходных ишнах блока уп 4авления, подключенных к разрядным выходам сдвнгово.го регистра (начиная со.второго), устанавливаются запрещающие уровни .напряжений.

При первоначальной установке в исходное состояние на вход бло.ка, подключенный к другому вхо.цу элемента И 19, от выхода арифметического блока поступает разрешающий уровень.

При поступлении (фиг.2) на третий вход блока импульса замера контролируемого параметра триггер 18 перебрасывается в единичное состояние, тем самым отпирается элемент И 19, и импульсный вход блока коммутируется на. вход синхронизации сдвигового регистра 17. Каждый из и iпyльcoв, поступивших на вход синхронизации сдвигового регистра 17, обеспечивает сдвиг единицы, записанной первоначально а первый разряд его, на один разряд, чем обеспечивается последовательное возбуждение (и гашение) выходных шин блока.

Так как ет«од последнего разряда сдвигового регистра 17 замкнут ва вход сброса триггера включения цикла перерасчета (а также на вход первого разряда), то сдвиг единицы иэ последнего разряда в первый разряд сдвигового регистра 17 сопровождается установкой триггера 18 в нулевое состояние и, как следствие, блокировкой поступления импульсов ца вход синхронизации сдвигового регистра. Таким образом, до поступленияочередного включения цикла перерасчета на установочный вход триггера 18 блок управления остается в исходном состоянии, а на выходных шинах его фиксируются запрещгиощие уровни напряжений .

Второй вход, подключенный к злемепту и 19, предназначен для блокировки поступления в цикле перерасче1га импульсов на вход синхронизации сдвигового регистра 1 при выполнеНИИ арифметическим блоком 3 той или иной операции. Последнее связано с тем, что, возбудив очередным импульсом, поступающим с выхода генератора 1, выходную шину блока, обеспечивающую в арифметическом блоке 3 выполнение той или иной арифметичес кой операции, необходимо поддержива ее возбужденной до тех пор, пока операция не будет закончена. Введенные блоки позволяют производить оценку текущего значения дис персии, в результате обеспечивается расширение функциональных возможнос тей устройства. Формула изобретения Устройство для определения дисперсии, содержащее блок управления, шгход которого подключен к первому входу арифметического блока, отл чающееся тем, что, с целью расширения функциональных возможнос тей, за счет анализа нестационарных случайных .процессов, устройство содержит счетчик замеров, три регистра, пять блоков элементов И два блока элементов ИЛИ, причем выход блока управления подключен к первому входу, первого блока элементов И, второй вход которого является первы входом устройствЗг выход первого блока элементов И через первый регистр соединен с первшв входами первого и второго блоков элементов ИДИ, выходаа которых подключены соот ветственно ко второму и третьему входам арифметического блока. Первый выход которого соединен с перBHNsi входами второго, третьего,четвертого и пятого блоков элементов И здгорые входы которых объединены и подключены к выходу блок9 управлени выход генератора импульсов соединен с первым входом блока управления и четвертым входом арифметического блока, второй выход которого подклю чен ко второко входу блока управления, третий вход которого является вторым входом устройства/ выход блока управления соединен со входом счетчика замеров, выход которого подключен ко второму входу второго блока элементов ИЛИ, третий вход которого объединен со вторым входом первого блока элементов ИЛИ и соединен с выходом первого буферного регистра, вход которого подключен к выходу второго блока элементов И, выход третьего блока элементов И через второй регистр соединен с третьим входом первого блока элементов ИЛИ, четвертый вход которого подключен к выходу третьего регистра,вход которого соединен с выходом четвертого блока элементов И, выход пятого блока элементов И через второй буферный регистр подключен к четвертому входу второго блока элементов ИЛИ, пятый вход которого объединен с пятым входом первого блока элементов ИЛИ в соединен с вьлходом блока управления. 2. Устройство по п.1, о т л и чающееся тем, что блок управления содержит элемент И, триггер и сдвиговый регистр, первый выход которого является выходом блока, второй анход сдвигового регистра соединен со входом установки в водь триггера, шшод которого подключен к первому входу элемента и, второй и тр«1тнй входы которого являются соответственно первым и втором входами блока, третьим входом которого является вход установки в единицу трнгге1$а, выход элемента и соединен со входом сдвигового регистра. Источники информации, принятые во внимгшив при экспертизе 1.Авторское саад «тельство СССР 407322, кл. G 06 Р 15/36, 1974. 2.Романенко А.Ф. и др. Bonpoq j прикладного анализа случайных процессов. М., 1968, Советское радио, с.221 (прототип) .

jTb

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор | 1984 |

|

SU1247884A1 |

| Система для обработки данныхпАРАМЕТРОВ СКАНиРуЕМыХ изОбРАжЕНий | 1978 |

|

SU805329A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Процессор быстрого преобразования Фурье | 1982 |

|

SU1086438A1 |

| Устройство для тестового контроля блоков памяти | 1986 |

|

SU1365134A1 |

| Устройство памяти на кадр цифрового теливизионного изображения | 1988 |

|

SU1600002A1 |

| Устройство для редактирования | 1982 |

|

SU1117669A1 |

| Устройство для измерения динамических характеристик аналого-цифровых преобразователей | 1984 |

|

SU1290521A1 |

| Устройство для отображения информации | 1988 |

|

SU1649530A1 |

| Устройство для селекции изображений объектов | 1989 |

|

SU1709358A1 |

Авторы

Даты

1981-08-30—Публикация

1978-02-20—Подача