Изобретение относится к электромузыкальным инструментам (ЭМИ), в частности к устройствам генерирования шкалы частот.

Целью изобретения является расширение функциональных возможностей путем обес- нечения одновременного генерирования всех частот звукоряда при одновременном повышении надежности работы за счет сокра- и.1,ения числа элементов и цепей.

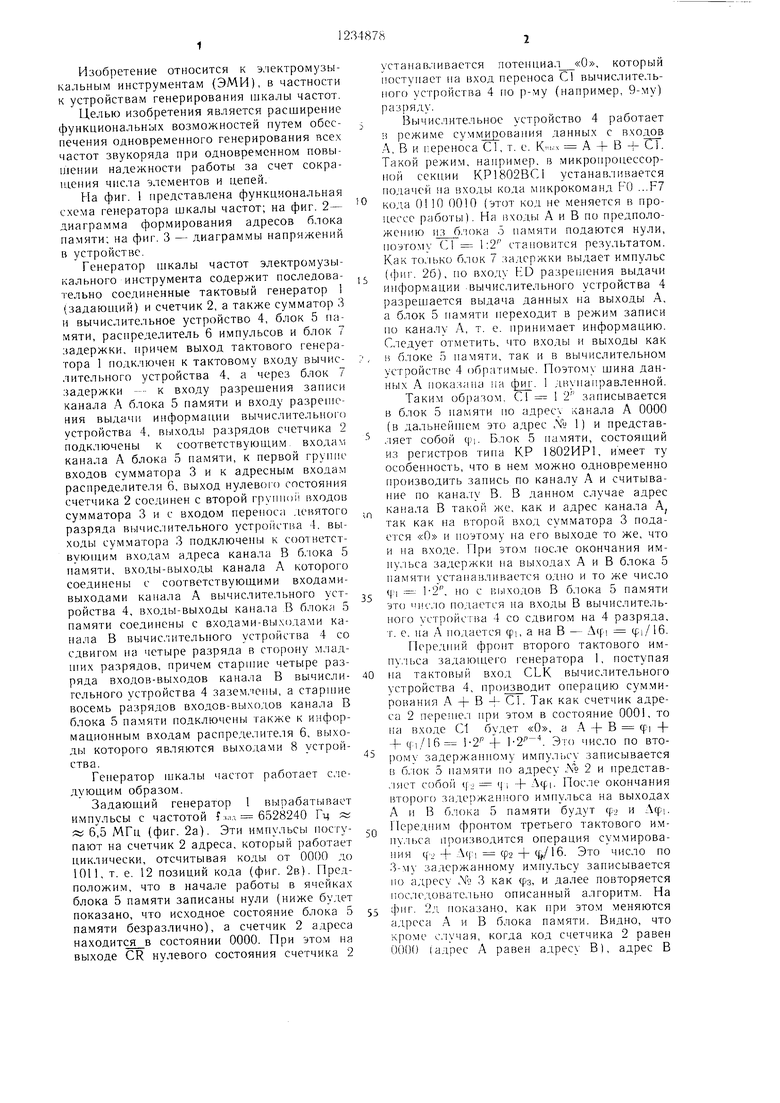

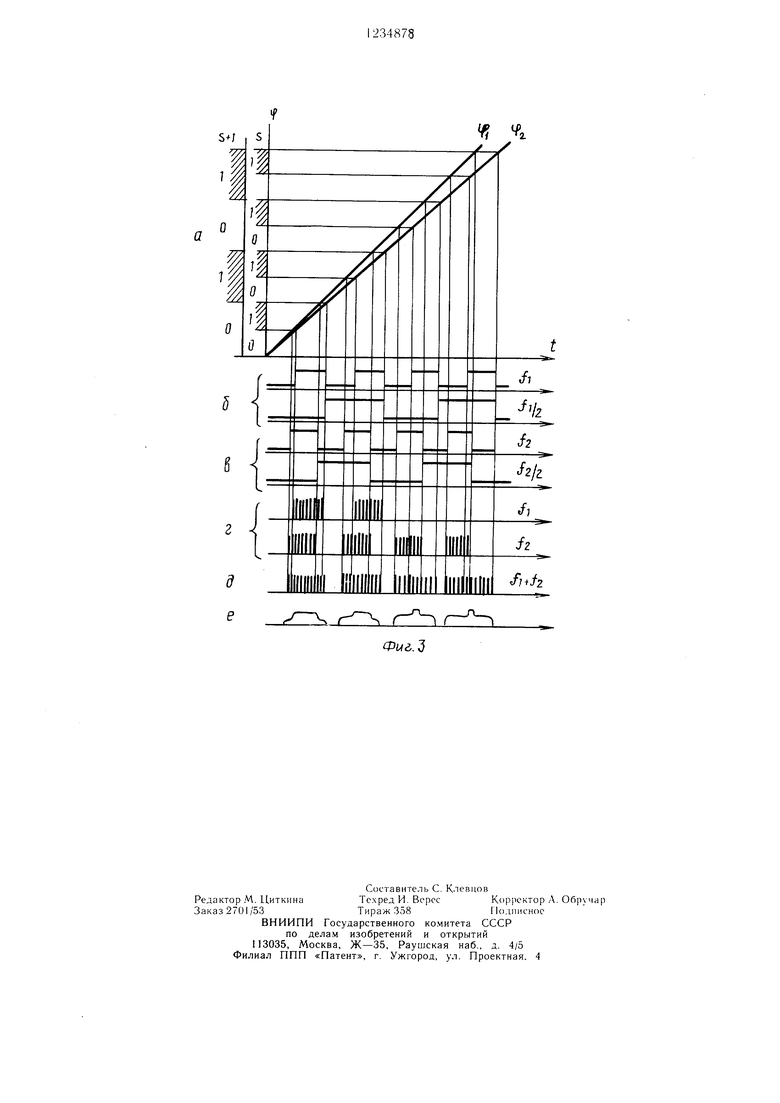

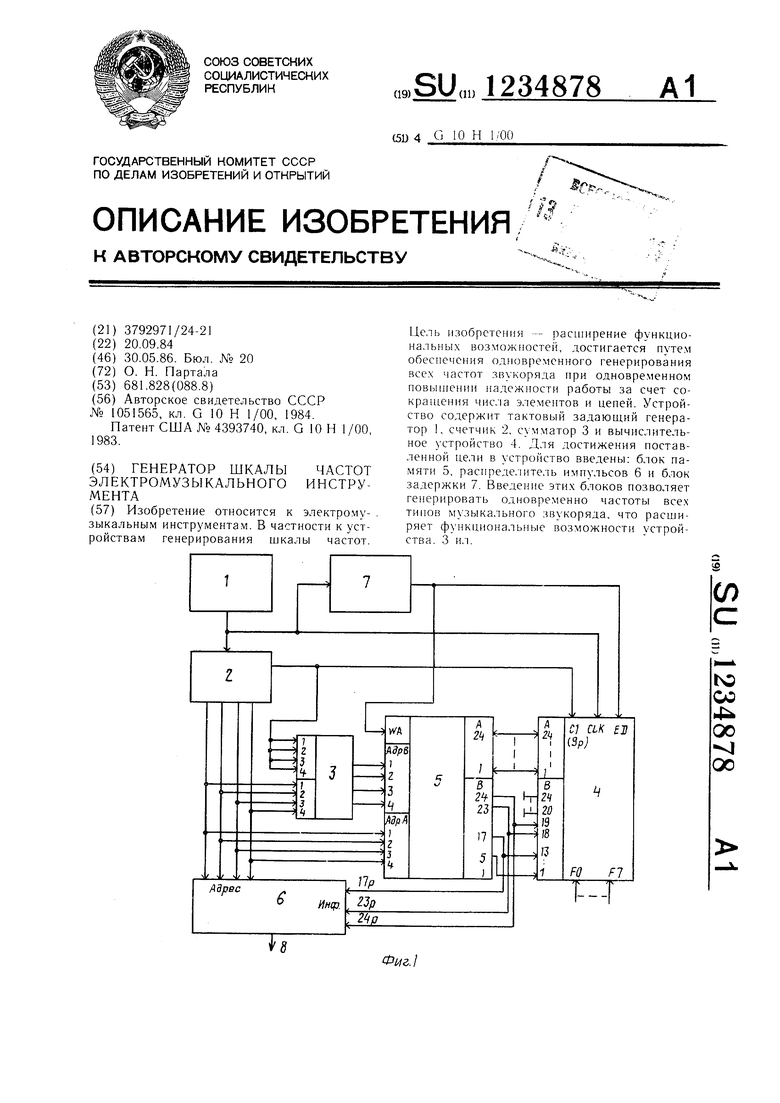

На фиг. 1 представлена функциональная с.хема генератора шкалы частот; на фиг. 2- диаграмма формирования адресов блока памяти; на фиг. 3 - диаграммы напряжений в устройстве.

Генератор шкалы частот электромузыкального инструмента содержит последовательно соединенные тактовый генератор 1 (задающий) и счетчик 2, а также сумматор 3 и вычислительное устройство 4, блок 5 la- мяти, распределитель б импульсов и блок 7 задержки, причем выход тактового генератора 1 подключен к тактовому входу вычислительного устройства 4, а через блок 7 задержки -- к входу разрешения записи канала А блока 5 памяти и входу разрепю- ния выдачи информации вычислительного устройства 4, выходы разрядов счетчика 2 подключены к соответствующим, входам канала А блока 5 памяти, к первой группе входов сумматора 3 и к адресным входам распределителя 6, выход нулевого состояния счетчика 2 соединен с второй rpynnoii входов сумматора 3 и с входом переноса девятого разряда вычислительного устр011ства 4. выходы сумматора 3 подключены к COOIHCTCT- вуюшим входам адреса канала В б.юка 5 памяти, входы-выходы канала А которого соединены с соответствующими входами- выходами канала А вычислительного устройства 4, входы-выходы канала В блоки 5 памяти соединены с входами-вы.чодами канала В вычислительного устройства 4 со сдвигом на четыре разряда в сторону млад- 1НИХ разрядов, причем старшие четыре разряда входов-выходов канала В вычисли- гельного устройства 4 зазем.чены, а старп1ие восемь разрядов входов-выходов канала В блока 5 памяти подключены также к информационным входам распределителя 6, выходы которого являются выходами 8 устройства.

Генератор шкалы частот работает следующим образом.

Задающий генератор 1 вырабатывает импульсы с частотой дал 6528240 Гц л « 6,5 МГц (фиг. 2а). Эти импульсы поступают на счетчик 2 адреса, который работает циклически, отсчитывая коды от 0000 до 1011, т. е. 12 позиций кода (фиг. 2в). Предположим, что в начале работы в ячейках блока 5 памяти записаны нули (ниже будет показано, что исходное состояние блока 5 памяти безразлично), а счетчик 2 адреса находится в состоянии 0000. При этом на выходе CR нулевого состояния счетчика 2

0

5

0

5

устанав. 1ивается потенциал«О, который

поступает на вход переноса С вычислительного устройства 4 по р-му (например, 9-му) раз)яду.

Вычислительное устройство 4 работает в режиме )овапия данных с входов А, В и переноса сТ, т. с. К.х А + В -J- СТ. Такой режим, например, в микропроцессорной секции КР1802ВС1 устанавливается подачей на входы кода микрокоманд FO ...F7 кола 0110 0010 (эт(Л код не меняется в процессе работы). На иходы А и В по предположению 1П блока о памяти подаются нули, ПОЭТОМУ С1 - 1:2 ста1ювится результатом. Как то;1ько блок 7 задержки выдает импульс ((jnir. 26), по входу t:D разрешения выдачи информации вычислительного устройства 4 разрешается выдача данных на выходы А, а блок 5 памяти переходит в режим записи но каналу у, т. е. принимает информацию. Следует отметить, что входы и выходы как и блоке 5 памяти, так и в вычислительном устройстве 4 обратимые. Поэтому шина данных А показана па ф и г;. 1 двунаправленной.

Таким об)азом. С1 1 2 записывается в блок 5 памяти по адрес канала А 0000 (в дальнейшем это адрес ХУ 1) и представляет собой q)i. Блок 5 памяти, состоящий из регистров типа КР 1802ИР1, имеет ту особенность, что в нем можно одновременно производить запись по каналу А и считывание по каналу В. В данном случае адрес канала В такой же, как и адрес канала А, так как на второй вход сумматора 3 подается «О п поэтому на его выходе то же, что и па входе. При этом после окончания импульса задержки на В1)1ходах А и В блока 5 памяти устанаиливастся одно и то же число 1-2, по с р.ыходов В блока 5 памяти

это подается на входы В вычислитель- пого устрг)йсгва 4 со сдвигом на 4 разряда, т. е. на А подается ф1, а на В - A(pi cpi/16. Передний фронт второго тактового импульса задающего 1 енератора 1, поступая па тактовый вход CLK вычислительного устройства 4, произв одит операцию суммирования А + В -L С1. Так как счетчик адрепри этом в состояние 0001, то будет «О, а .А + В ф: -|са 2 переп1ел па входе С1

-f q:,/16 2 - Это число по вто- )ому задержанному импульсу записывается в б.юк 5 памяти по адресу 2 и представ- , 1яст собой ((v qi + Аф|. После окончания второго задержанного импульса на выходах А и В блока 5 памяти будут (р2 и Лф1. Передним фронтом третьего тактового импульса производится операция суммирова1П1Я (f 2 --Ь A(|:I ф2 + %/1б. Это число ПО

3-му задержанному импульсу записывается по адресу Ж 3 как фз, и далее повторяется последовательно описанный алгоритм. На фпг. 2д показано, как при этом меняются адреса А и В блока памяти. Видно, что кроме случая, когда код счетчика 2 равен 0000 (адрес А равен адресу В), адрес В

на 1 меньше адреса А. Для организации адреса В используется сумматор 3. На его пергзый вход подается код счетчика 2, а на второй вход - импульс н левого состояния CR счетчика 2. При CR О число 0000 на первом входе сумматора поступает па выход без изменений. При других состояниях счетчика 2 CR 1 и в сумматоре 3 производятся, например, операции (без учета переноса): 0001 + , 0010 + -|- 1111 0001 и т. д., что эквивалентно вычитанию единицы.

В качестве сумматора 3 может быть использована микросхема 155ИД13.

В первом цикле из двенадцати импульсов задаюпа.его генератора 1 в двенадцать ячеек памяти блока 5 заносятся исходные значения (pi, (f:, ((;s, -.., (р в следующем цикле в ячейку Л 1 заносится еще единица через вход переноса С1, т. е. (fi удваивается, iioc.ie этого последовательно удваиваются ((. pi, ..., cpio. ГТосле гп-го цикла числа в ячейках 1 12 увеличиваются в m раз. Этот процесс накопления чисел показан на фиг. За. При этом видно, что на S-м разряде блока 5 памяти во вре.мени образуется меандр с частотой 1|, а в S -Ь 1-м - с частотой 1:/2 и т. д. (фиг. 36. в), т. е. могут быть одновременно получеш час юты раз.чичных октав.

Абсолютные значения частот f, определяются следующим образом. Если в ячейку № I блока 5 памяти на каждом цикле из 12 импульсов задающего генератора 1 поступает «1 по р-му разряду, то на S-M разряде () образуется .меандр с частотой

Г.лд/12 „,:-. fi. 1 ячейке № 2, где благодаря

добавке Л(ч накопление происходит быстрее, на S-M разряде fi (1 + 1/16) fi, в ячейке ЛГо 3 f-i f,, + All, в ячейке К« 4 f., f, + + Af2 и т. д. Разрядная сетка данпого устройства имеет вид

a i3i; aifi . ,.:. . auy

часть фазы t

V 24-разрядная сетка делится на три части: чообную часть фазы, целую часть фазы, разряды октав, при этом в ячейку N° 1 едини- ia через вход переноса С1 вводится на 9-м разряде, а сигнал ноты 4-й октавы снимается с 17-го разряда. В 17-.м разряде д.чя I l единица появляется через 256 2 циклов, поэтому и период частоты равен 256 циклам

г /,о:f - -i6,5 .МГц

частоты f,a.712, т. е. t, 209 Гц, что соответствует «до 4-й октавы. С 18-го разряда снимается, следовательно, «до 3-й октавы, с 19-го. - «до 2-й октавы и т. д. С ячейки № 2, очевидно, с 17-го разряда снимается «до-диез 4-й октавы, с 18-го разряда - «до-диез 3-й октавы и т. д.

0

S

о

5

0

5

Со временем 24-разрядпая сетка в процессе накопления чисел переполняется, и происходит переход в ну.ювые состояния по всем разрядам. Поскольку темп накопления в различных ячейках , то эти переходы происходят иеодновременио и ec.in. например, в ячейке .V 1 в какой-то момент установился ny.ib. то в друг их ячейках будуг какие-то нача.1ьиые фазы. Для работы уег- ройства это не имеет значения, т. к. темп накои.чения чисе.1 в ячейках опреде, яется прежде всего темпом поетун. 1ения единипы в ячейку 1, от которой к другим ячейкам темп постепенно парапи1вается, а начальн1)1с фазы сигналов нот д.1я работы ЭМП несущественны.

Информации со старших разрядов блока 5 памяти (с 17-го по 24-й) поступает па информациоппьк входы распределителя (i. Расиределите. И) состоит из пабора строби- руемых деп1И(()аторо1). количество которых равно числ октав. Па каждый и: этих де- и ифраторов па адресные входы подается код счетчпка 2, а на информационный вхо.ч (вход строба) юстуиает сигна,1 с одного из разрядов б.юка п памяти. Например, Koi - да в б. юке 5 памяти опрап1И15ается jVo 7, в деп1И1)раторе информация noi rv- iaer на 7-i i выход. Распределитель б, га-чпм об- )азом, имеет cTo.ibKo выходов, ско.чько noi имеется во Bcei i клавиатуре Э.МИ. Па ка:нч- до.м из В1)1ходон де1пи1|1раторо1 (шспрсдели- теля 6 нояв.1яюпч я пачки со скважностью 12, соот1 ,етстьуюии1е меанд 1 на даином разряде ((иг. 3 б, в, г). иачки частота пмпхльсов равна Ь.;./12. а частота самих пачек соответствует часготе ноты. Если па к,1авиатуре (иа контакты которой подаются ciinia. ibi с выхода 8) нажать одиовремсппо две или бо.чее, то образуется пачек имиульсов, как показано иа фи1 . Зд. В .1а.и нейн1см в уси.штеле низкой частоты выделяются суммарные низкочастогпые сигпа.1ы, как пока:5ап() па фиг.- 3с.

Поскольку дробная часть занимает 8 разрядов, то обеснечиваетея точность в 1/256 по частоте, т. е. ±0,2%.

Таким образом, введение новых у:. 1он (блока 5 памяти, блока 7 задержки, lac- преде. штеля 6) иозполяет -енерпровать од- новременно частоты всех типов музыка. ib- ного звукоряда, что расп1иряет функциональные возможности устройства. Кроме того, цутем применения крунных функциональных блоков снижается число элементов и цепей и иов зппается падежносгь работы устройства.

Генератор П1ка.1ы частот э.1ектпо ; ,:-- кальпого ппсгр л1е1гга. содержании икмслп вате, сос.чинеипые такт;)..)Г1 генератор

и счетчик, а также сумматор и вычислительное устройство, отличающийся тем, что, с целью расширения функциональных возможностей путем обеспечения одновременного генерирования всех частот звукоряда при одновременном повышении надежности работы, в него введены блок памяти, распределитель импульсов и блок задержки, причем выход тактового генератора подключен к тактовому входу вычислительного устройства, а через блок задержки - к входу разрешения записи канала А блока памяти и входу разрешения выдачи информации вычислительного устройства, выходы разрядов счетчика подключены к соответствующим входам канала А блока памяти, к первой группе входов сумматора и к адресным входам распределителя, выход нулевого состояе Операц, ,+ 41/-,

Фиг.2

ния счетчика соединен с второй группой входов сумматора и с входом переноса вычислительного устройства, выходы сумматора подключены к соответствующим входам адреса канала В блока памяти, входы-выходы канала А которого соединены с соот- 1 етствую1цими входами-выходами канала А вычислительного устройства, входы-выходы канала В блока памяти соединены с входами- выходами канала В вычислительного устройства со сдвигом на четыре разряда в сторону младших разрядов, причем старшие четыре разряда входов-выходов канала В вычислительного устройства заземлены, а старшие восемь разрядов входов-выходов канала В блока памяти подключены также к информационным входам распределителя, выходы которого являются выходами устройства.

f,,/

Фиг,.

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь тональных сигналов электронного музыкального инструмента | 1986 |

|

SU1370667A1 |

| ОПЕРАТИВНЫЙ КОНТРОЛЛЕР СУММАРНОЙ МОЩНОСТИ НАГРУЗКИ ГРУППЫ ЭНЕРГОПОТРЕБИТЕЛЕЙ | 1998 |

|

RU2145717C1 |

| Устройство для контроля блоков оперативной памяти | 1985 |

|

SU1314388A1 |

| БЫСТРОДЕЙСТВУЮЩИЙ ПРЕЦИЗИОННЫЙ ЧАСТОМЕР ПРОМЫШЛЕННОГО НАПРЯЖЕНИЯ | 2006 |

|

RU2333501C1 |

| Микропрограммное устройство управления | 1984 |

|

SU1168940A1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Канальный процессор-тонгенератор для электронного музыкального инструмента | 1986 |

|

SU1465903A1 |

| Устройство для ввода информации | 1985 |

|

SU1327087A1 |

| Электронный генератор звуковых сигналов | 1980 |

|

SU896679A1 |

| Устройство для сопряжения каналов передачи данных с ЭВМ | 1985 |

|

SU1226476A1 |

Изобретение относится к электромузыкальным инструментам. В частности к устройствам генерирования шкалы частот. Т Цель изобретения -- рас1нирение функциональных возможностей, достигается путе.м обеспечения одновременного генерирования всех частот звукоряда ири одновременном новьипении надежности работы за счет сокращения чис, 1а элементов и пеней. Устройство содержит тактовый задающий генератор 1, счетчик 2, сумматор 3 и вычислительное устройство 4. Для достижения поставленной цели в устройство введены: блок памяти 5, раснредел ите, 1Ь имнульсов 6 и блок задержки 7. Введение этих блоков позволяет генерировать одновременно частоты всех тинов музыкального звукоряда, что расширяет функциональные возможности устройства. .3 ил. N3 оо 4 00 ОО Фиг. I

| Генератор шкалы частот электромузыкального инструмента | 1981 |

|

SU1051565A1 |

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

| Патент США № 4393740, кл | |||

| Печь-кухня, могущая работать, как самостоятельно, так и в комбинации с разного рода нагревательными приборами | 1921 |

|

SU10A1 |

Авторы

Даты

1986-05-30—Публикация

1984-09-20—Подача