Изобретение относится к вычислительной технике и может быть исполь- зоэано для автономной проверки и наладки блоков оперативной памяти.

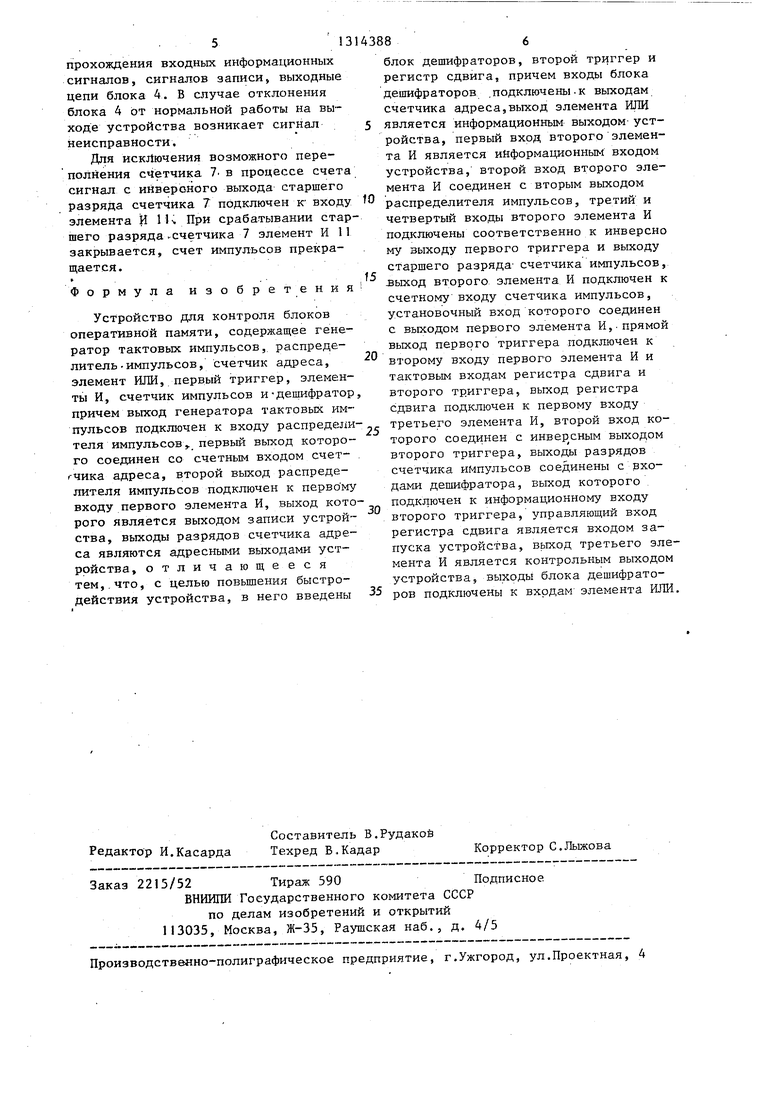

Цель изобретения - повышение бы- стродействия устройства.На чертеже изображена функциональная схема устройства для контроля. блоков оперативной памяти.

Устройство содержит генератор 1 тактовых импульсов, распределитель 2 импульсов, счетчик 3 адреса и подключается к контролируемому блоку 4 оперативной памяти. Устройство также сюдержит первый триггер 5, первый элемент И. 6,. счетчик 7 импульсов, дешифратор 8, блок 9 дешифраторов,, элемент ИЛИ 10, второй элемент И П., второй триггер 12, регистр 13- сдвига и третий элемент И 14.

Генератор 1 - автоколебательный генератор последовательности импульсов. Частота генерации выбирается с учетом максимально допустимой час- тоты смены адреса в блоке 4.

Распределитель 2 импульсов может быть выполнен, например, по схеме цифрового делителя частоты импульсов на три. При этом на вхоД счетчика 3 адреса подключают последовательность вьщеленных первых импульсов. На Другом выходе распределителя 2 формируется последовательность выделенных вторых импульсов.

Дешифратор 8 выделяет одно из состояний счетчика 7 и может быть выполнен, например, на многовходовом .элементе И. Блок 9 дешифраторов

представляет собой совокупность деши- 0 няет свое состояние каждый раз в мофраторов, аналогичных дешифратору В.

Устройство работает следующим образом.

В исходном состоянии, при отсутствии команды Пуск, двухразрядный регистр 13-удерживается по установочному входу в обнуленном состоянии. .Элемент И 14 закрыт и на выходе устройства отсутствует сигнал неисправмент переполнения счетчика 3 адреса, т.е. один раз за полный цикл последовательного обращения ко всем ячейкам памяти блока 4. Полный цикл 5 работы счетчика 3 адреса, при котором на прямом выходе триггера 5 имеет мес.то разрешающий потенциал, является циклом записи. В цикле записи элемент И 6 открыт. Импульсы заности. Ячейки памяти ко.нтролируемого 50 поступающие с второго выхода блока 4 оперативной памяти находятся распределителя 2, проходят на вход

в произвольном состоянии.

Генератор 1 формирует непрерывную последовательность тактовых импульсов. Распределитель 2 импульсов осуществляет деление частоты тактовых импульсов на три. Сформированная на выходе распределителя 2 последовательность первых импульсов поступает

на вход счетчика 3 адреса; Сформированная на втором выходе распр едели- теля 2 последовательность вторых- импульсов поступает на входы элементов И 6 и 11 и осуществляет строби- рование сигналов, поступаюш 1х на другие входы этих элементов.

Счетчик 3 адреса имеет количество разр)ядов п, равное количеству адресных входов блока 4, Просчитывая импульсы, поступающие с выхода распределителя 2, счетчик 3 адреса формирует на своих выходах двоичные числа от О до 2 - 1. При этом осуществляется последовательное обращение ко всем ячейкам памяти блока 4.

Блок 9 дешифраторов содержит п дешифраторов и дешифрирует двоичные

.числа, содержащие в своих разрядах только одну единицу. Например, при четырехразрядном счетчике 3 адреса эти двоичные числа равнь 0001, 0010, 0100,- 1000. Сигналы с выходов дешифраторов блока 9 объединяются на элементе ИЛИ 10-и поступают в качестве тестовых сигналов на информационный вход блока 4 оперативной памяти для записи в ячейки памяти. Таким образом для данного примера в ячейки памяти с адресами 0001, 0010, 0100,. 1000 в цикле записи записана единица, в остальных ячейках памяти - нуль.

Режимы записи и считывания в устройстве переключаются триггером 5, на вход которого по.даются импульсы с выхода старшего разряда счетчика 3 адреса. При этом триггер 5 изме

мент переполнения счетчика 3 адреса, т.е. один раз за полный цикл последовательного обращения ко всем ячейкам памяти блока 4. Полный цикл 5 работы счетчика 3 адреса, при котором на прямом выходе триггера 5 имеет мес.то разрешающий потенциал, является циклом записи. В цикле записи элемент И 6 открыт. Импульсы за55

записи блока 4. Осуществляется запись единиц, поступающих с выхода элемента ИЛИ 10 в ячейки памяти с указанными адресами. В конце цикла записи триггер.5 изменяет свое.состояние . При этом закрывается элемент И 6 и открывается элемент И 11. Счетчик 7 в режиме записи обнуляет

ся по установочному входу импульсами с выхода элемента И 6.

В цикле считывания на выходе исправного блока 4.оперативной памяти появляются записанные в цикле запи- си п единиц Счетчик 7 осуществляет счет этих единиц. Для обеспечения его нормальной работы сигналы с выхода блока 4 стробируются на элементе И 1 Г импульсами записи. Количест- во разрядов счетчика 7 выбирается равным ближайшему целому числу, большему числа 1 + Iog2 .

В конце цикла считывания вновь срабатывает триггер 5.- К этому моменту счетчик 7 в процессе своего счета устанавливается в состояние п./ Это состояние дешифрируется дешифратором 8. В момент срабатывания триггера 5 на тактовом входе триггера 12 возникает перепад напряжения, по которому он устанавливается в состояние, соответствующее сигналу на его информационном входе. Если дешифратор 8 в этот момент открыт, триггер 12 устанавливается в состояние , при котором на его инверсном выходе сигнал неисправности отсутствует. При любом другом состояний счетчика 7 на-инверсном выходе триггера 12 появляется сигнал неисправности, который хранится в триггере 12 до поступления на его тактовый вход следующего положительного перепада напряжения, т.е. до начала следующего цикла записи.

Таким образом, для контроля блока 4 оперативной памяти достаточно осуществить один цикл записи тестовых сигналов и один цикл считывания Дл исключения появления на выходе устройства ложного сигнала неисправности, который может возникнуть в момент включения устройства или при смене проверяемого блока 4 оперативной памяти, в устройстве осуществляется дополнительное стробирова- ние сигнала неисправности.

После включения устройства или смены блока 4 на устройство подается команда Пуск посредством установочного входа регистра 13, При этом регистр 13 перестает удерживатся в обнуленном состоянии. При пос- туплении на .тактовый вход регистра 13 перепадов напряжения, формируемы триггером 5, регистр 3 начинает заполняться единицами. Второй по сче

5

0

5

0

5

0

5

0

ту перепад напряжения вызывает срабатывание второго разряда регистра 13. При этом элемент И 14 открывается, разрешается поступление сигнала неисправности на выход устройства.

Поскольку между двумя перепадами напряжения, возникающими на выходе триггера 5, заключены один цикл считывания и один цикл записи, к моменту открывания элемента И 14 контроль блока 4 закончен. Тем самым предотвращается появление на выходе устройства ложного сигнала неисправности.

Устройство при возможных неисправно ст ях контролируемого блока 4 оперативной памяти функционирует следующим образом.

В случае, если в блоке 4 оперативной памяти происходит обрыв одной или нескольких адресных цепей, количество единиц на выходе блока 4, появляющихся в цикле считывания, увеличивается. Например-, при п 4 производится запись единиц в блок 4 при состояниях счетчика 3 адреса 0001, Q010, OiOO, 1000, Пусть произошел обрыв в цепи подключения младшего (на чертеже справа) разряда адреса. При этом в данной цепи устанавливается произвольный потенциал, например О, Тогда запись происходит в ячейки памяти с адресами 0000, 0010 0100, 1.000.

В цикле считывания младший разряд адреса также сохраняет состояние О. Поэтому единицы на выходе блока 4 появляются при состояниях счетчика 3 адреса 0000, 0001, 0010, 0011 0100, 010, 1000, Ш01, Таким образом, на выходе элемента И 1 появляется вдвое больше импульсов, чем это происходит при исправном блоке 4. В конце цикла, считывания на выходе дешифратора 8 оказывается О. Триггер 12 устанавливается в состояние,.свидетельствующее о неисправности блока 4. На вы- х;оде устройства появляется сигнал неисправности. I

При выбранном в устройстве тестовом сигнале количество единиц, воз- никаюш 1х на выходе блока 4 в цикле считывания, будет увеличиваться rfb сравнению с нормальным при любой неисправности в цепях подключения адресных сигналов, т.е. и при обрывах, и при замыканиях. При работе устройства контролируются также цепи

51314388

х информационных записи, выходные учае отклонения ной работы на вызникает сигнал 5

возможного пере7. в процессе счета о выхода старшего подключен к входу О срабатывании старика 7 элемент И 11 импульсов прекра

бл ре де сч яв ро т у м ра че по му ст вы сч ус с вы вт та вт сд тр то вт сч да по вт ре пу ме ус ро

Формула изобретения

Устройство для контроля блоков оперативной памяти, содержащее генератор тактовых импульсов, распределитель-импульсов, счетчик адреса, элемент ИЛИ, первый триггер, элементы И, счетчик импульсов и-дешифратор причем выход генератора тактовых импульсов подключен к входу распределителя импульсов первый выход которого соединен со счетным входом счет- гчика адреса, второй выход распределителя импульсов подключен к перво му входу первого элемента И, выход которого является выходом записи устройства, выходы разрядов счетчика адреса являются адресными выходами устройства, отличающееся тем,.что, с целью повьш1ения быстродействия устройства, в него введены

Редактор И.Касарда

Составитель В.Рудаков Техред Б.Кадар

Кор Под

2215/52 Тираж 590

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

блок дешифраторов, второй триггер и регистр сдвига, причем входы блока дешифраторов .подключены.к выходам счетчика адреса,выход элемента ИЛИ является информационным выходом- устройства, первый вход второго элемента И является информационным входом устройства, второй вход второго элемента И соединен с вторым выходом распределителя импульсов, третий и четвертый входы второго элемента И подключены соответственно к инверсно му выходу первого триггера и выходу старшего разряда- счетчика импульсов, выход второго элемента И подключен к счетному входу счетчика импульсов, установочный вход которого соединен с выходом первого элемента И,.прямой выход первого триггера подключен к второму входу первого элемента И и тактовым входам регистра сдвига и второго триггера, выход регистра сдвига подключен к первому входу третьего элемента И, второй вход которого соединен с инвер сным выходом второго триггера, выходы разрядов счетчика импульсов соединены с входами дешифратора, выход которого , подключен к информационному входу второго триггера, управляющий вход регистра сдвига является входом запуска устройства, вьгход третьего элемента И является контрольным выходом устройства, выходы блока дешифраторов подключены к входам элемента ИЛИ.

Корректор С.Лыжова Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для отображения графической информации на экране телевизионного индикатора | 1987 |

|

SU1439672A1 |

| Трехканальное резервированное устройство для приема и передачи информации | 1990 |

|

SU1758646A1 |

| Многоканальное буферное запоминающее устройство | 1990 |

|

SU1721631A1 |

| Устройство для отладки программ | 1983 |

|

SU1290334A1 |

| Устройство для записи информации в оперативную память | 1990 |

|

SU1751811A1 |

| Устройство для сопряжения вычислительной машины с каналом связи | 1985 |

|

SU1291994A1 |

| Устройство для контроля многоразрядных блоков оперативной памяти | 1987 |

|

SU1495854A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Устройство для контроля полупроводниковой оперативной памяти | 1981 |

|

SU991516A1 |

| Устройство для вывода графической информации | 1987 |

|

SU1437908A1 |

Изобретение относится к вычислительной технике и может быть ис.- .пользовано для автономной проверки и наладки блоков оперативной памяти. Цель изобретения - повьшение быстродействия устройства. Устройство для контроля блоков оперативной памяти содержит генератор 1 тактовых импульсов, распределитель 2 импульсов,, счетчик 3 адреса, блок 9 депшфрато- ров, триггеры 5 и 12, счетчик 7 импульсов, дешифратор 8, ре- гистр 13 сдвига, элементы И 6, 11 и 14, элемент ИЛИ 10, Работа устройства основана на записи в блок 4 оперативной памяти тестовой информации, обеспечивающей при считывании определенное количество единиц на выходе исправного блока оперативной памяти. Тест организован таким образом, что при возникновении любой неисправности в блоке 4 количество единиц иа его выходе возрастает или убывает. Осуществляется счет количества единиц на выходе блока, формируется потенциальный сигнал неисправности. 1 ил. с S (Л I ВыхоЗ СО 4 САЭ 00 00

| Устройство для контроля памяти | 1982 |

|

SU1061174A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Устройство для контроля оперативной памяти | 1981 |

|

SU1014041A1 |

| Солесос | 1922 |

|

SU29A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1987-05-30—Публикация

1985-12-09—Подача