Изобретение относится к цифровой вычислительной технике и может быть использовано в качестве устройства синхронизации и управления в многоканальных вычислительных системах.

Цель изобретения - сокращение объема оборудования.

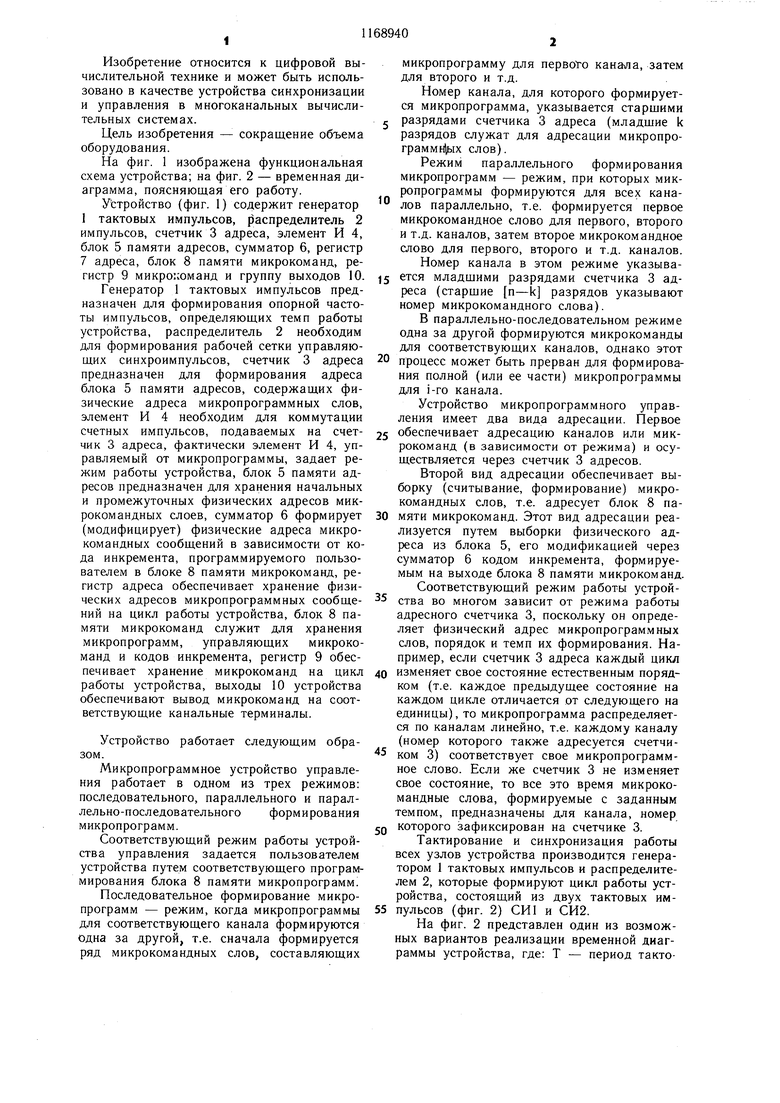

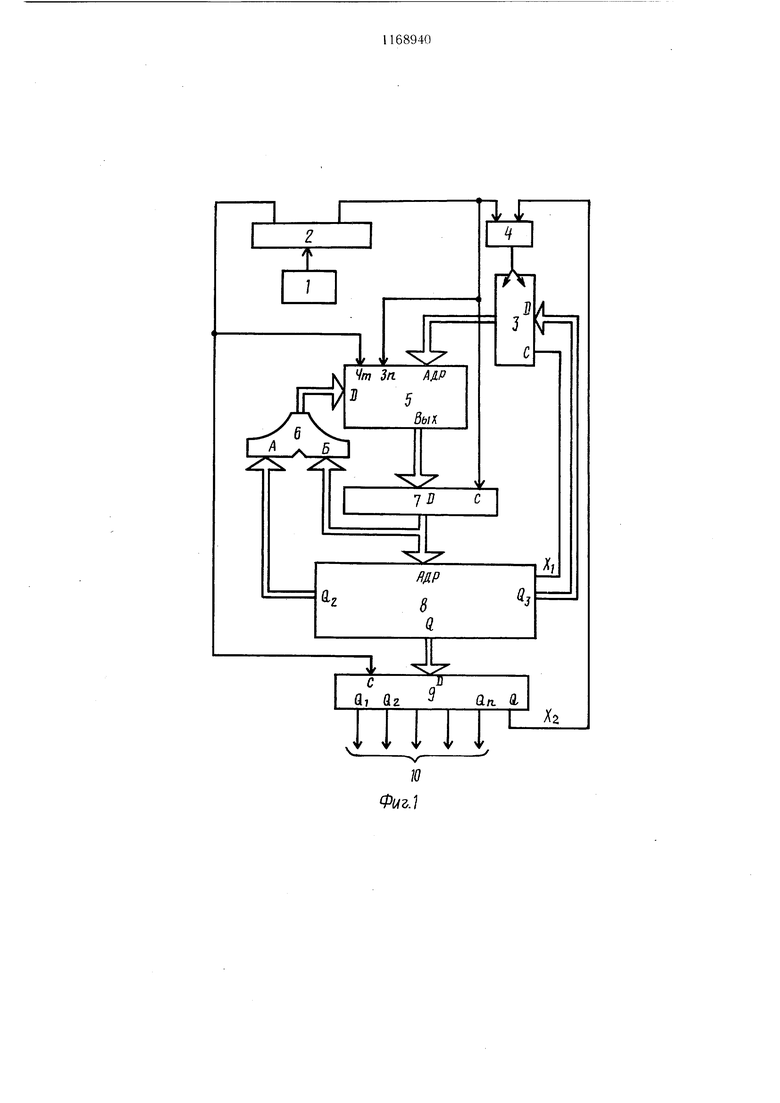

На фиг. 1 изображена функциональная схема устройства; на фиг. 2 - временная диаграмма, поясняющая его работу.

Устройство (фиг. 1) содержит генератор 1 тактовых импульсов, распределитель 2 импульсов, счетчик 3 адреса, элемент И 4, блок 5 памяти адресов, сумматор 6, регистр 7 адреса, блок 8 памяти микрокоманд, регистр 9 микро:;оманд и группу выходов 10.

Генератор 1 тактовых импульсов предназначен для формирования опорной частоты импульсов, определяющих темп работы устройства, распределитель 2 необходим для формирования рабочей сетки управляющих синхроимпульсов, счетчик 3 адреса предназначен для формирования адреса блока 5 памяти адресов, содержащих физические адреса микропрограммных слов, элемент И 4 необходим для коммутации счетных импульсов, подаваемых на счетчик 3 адреса, фактически элемент И 4, управляемый от микропрограммы, задает режим работы устройства, блок 5 памяти адресов предназначен для хранения начальных и промежуточных физических адресов микрокомандных слоев, сумматор 6 формирует (модифицирует) физические адреса микрокомандных сообщений в зависимости от кода инкремента, программируемого пользователем в блоке 8 памяти микрокоманд, регистр адреса обеспечивает хранение физических адресов микропрограммных сообщений на цикл работы устройства, блок 8 памяти микрокоманд служит для хранения микропрограмм, управляющих микрокоманд и кодов инкремента, регистр 9 обеспечивает хранение микрокоманд на цикл работы устройства, выходы 10 устройства обеспечивают вывод микрокоманд на соответствующие канальные терминалы.

Устройство работает следующим образом.

Микропрограммное устройство управления работает в одном из трех режимов: последовательного, параллельного и параллельно-последовательного формирования микропрограмм.

Соответствующий режим работы устройства управления задается пользователем устройства путем соответствующего программирования блока 8 памяти микропрограмм

Последовательное формирование микропрограмм - режим, когда микропрограммы для соответствующего канала формируются одна за другой, т.е. сначала формируется ряд микрокомандных слов, составляющих

микропрограмму для первотго каначпа, затем для второго и т.д.

Номер канала, для которого формируется микропрограмма, указывается старщими разрядами счетчика 3 адреса (младщие k разрядов служат для адресации микропроrpaMMHlf ix слов).

Режим параллельного формирования микропрограмм - режим, при которых микропрограммы формируются для всех каналов параллельно, т.е. формируется первое микрокомандное слово для первого, второго и т.д. каналов, затем второе микрокомандное слово для первого, второго и т.д. каналов. Номер канала в этом режиме указывается младщими разрядами счетчика 3 адреса (старщие п-k разрядов указывают номер микрокомандного слова).

В параллельно-последовательном режиме одна за другой формируются микрокоманды для соответствующих каналов, однако этот

0 процесс может быть прерван для формирования полной (или ее части) микропрограммы для i-ro канала.

Устройство микропрограммного управления имеет два вида адресации. Первое

5 обеспечивает адресацию каналов или микрокоманд (в зависимости от режима) и осуществляется через счетчик 3 адресов.

Второй вид адресации обеспечивает выборку (считывание, формирование) микрокомандных слов, т.е. адресует блок 8 памяти микрокоманд. Этот вид адресации реализуется путем выборки физического адреса из блока 5, его модификацией через сумматор 6 кодом инкремента, формируемым на выходе блока 8 памяти микрокоманд. Соответствующий режим работы устройства во многом зависит от режима работы адресного счетчика 3, поскольку он определяет физический адрес микропрограммных слов, порядок и темп их формирования. Например, если счетчик 3 адреса каждый цикл

0 изменяет свое состояние естественным порядком (т.е. каждое предыдущее состояние на каждом цикле отличается от следующего на единицы), то микропрограмма распределяется по каналам линейно, т.е. каждому каналу (номер которого также адресуется счетчиком 3) соответствует свое микропрограммное слово. Если же счетчик 3 не изменяет свое состояние, то все это время микрокомандные слова, формируемые с заданным темпом, предназначены для канала, номер

Q которого зафиксирован на счетчике 3.

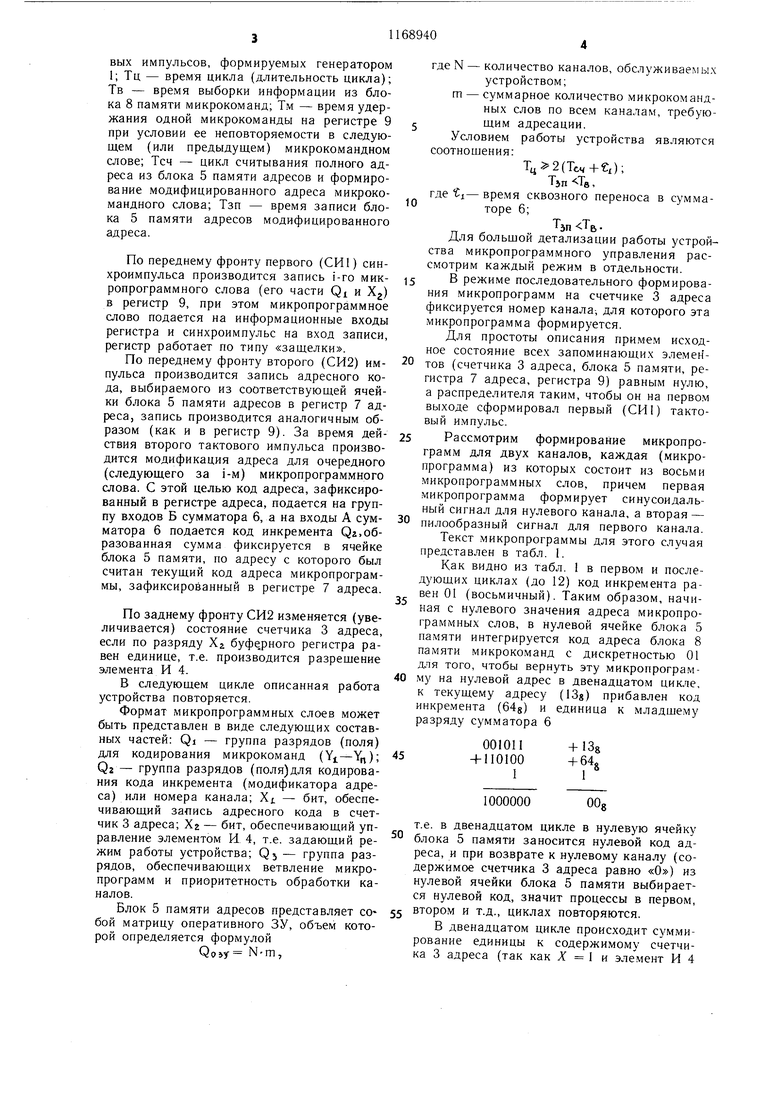

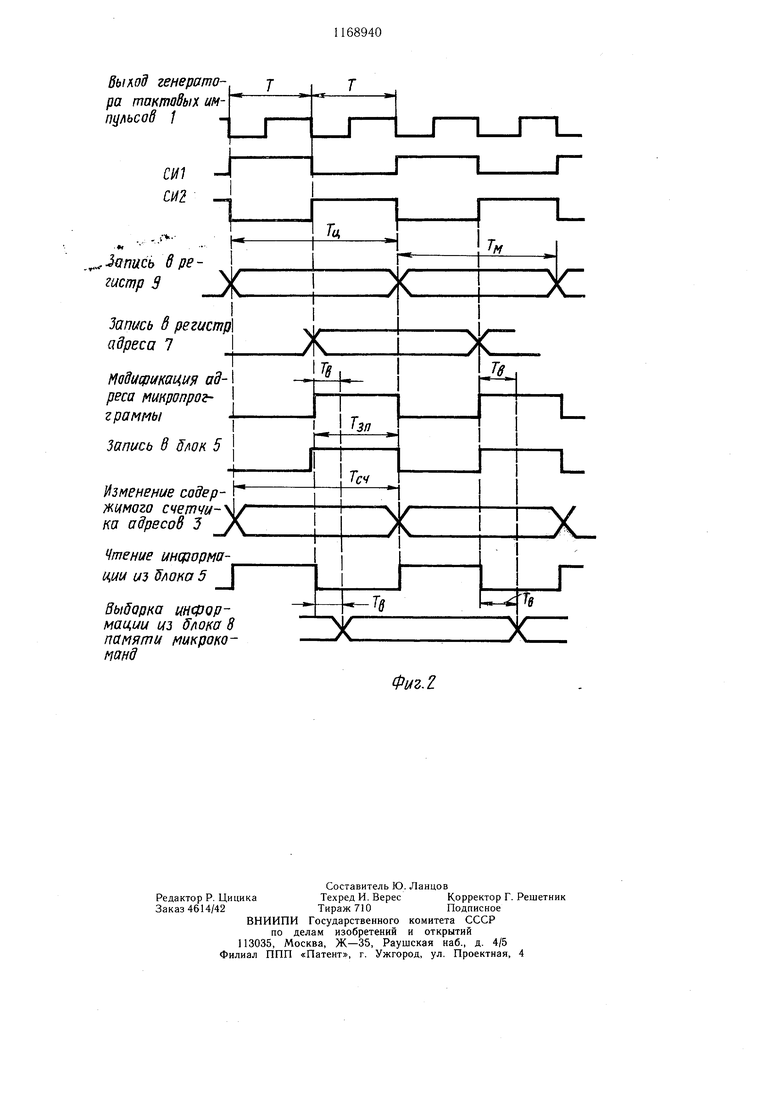

Тактирование и синхронизация работы всех узлов устройства производится генератором 1 тактовых импульсов и распределителем 2, которые формируют цикл работы устройства, состоящий из двух тактовых им5 пульсов (фиг. 2) СИ1 и СИ2.

На фиг. 2 представлен один из возможных вариантов реализации временной диаграммы устройства, где: Т - период тактовых импульсов, формируемых генератором 1; Тц - время цикла (длительность цикла); Тв - время выборки информации из блока 8 памяти микрокоманд; Тм - время удержания одной микрокоманды на регистре 9 при условии ее неповторяемости в следующем (или предыдущем) микрокомандном слове; Тсч - цикл считывания полного адреса из блока 5 памяти адресов и формирование модифицированного адреса микрокомандного слова; Тзп - время записи блока 5 памяти адресов модифицированного адреса.

По переднему фронту первого (СИ1) синхроимпульса производится запись i-ro микропрограммного слова (его части Qi и Xj) в регистр 9, при этом микропрограммное слово подается на информационные входы регистра и синхроимпульс на вход записи, регистр работает по типу «защелки.

По переднему фронту второго (СИ2) импульса производится запись адресного кода, выбираемого из соответствующей ячейки блока 5 памяти адресов в регистр 7 адреса, запись производится аналогичным образом (как и в регистр 9). За время действия второго тактового импульса производится модификация адреса для очередного (следующего за i-м) микропрограммного слова. С этой целью код адреса, зафиксированный в регистре адреса, подается на группу входов Б сумматора 6, а на входы А сумматора б подается код инкремента Qz,образованная сумма фиксируется в ячейке блока 5 памяти, по адресу с которого был считан текущий код адреса микропрограммы, зафиксированный в регистре 7 адреса.

По заднему фронту СИ2 изменяется (увеличивается) состояние счетчика 3 адреса, если по разряду Хг буферного регистра равен единице, т.е. производится разрещение элемента И 4.

В следующем цикле описанная работа устройства повторяется.

Формат микропрограммных слоев может быть представлен в виде следующих составных частей: Qi - группа разрядов (поля) для кодирования микрокоманд (); Qz - группа разрядов (поля)для кодирования кода инкремента (модификатора адреса) или номера канала; Хд - бит, обеспечивающий запись адресного кода в счетчик 3 адреса; Хг - бит, обеспечивающий управление элементом И 4, т.е. задающий режим работы устройства; Q5 - группа разрядов, обеспечивающих ветвление микропрограмм и приоритетность обработки каналов.

Блок 5 памяти адресов представляет со бой матрицу оперативного ЗУ, объем которой определяется формулой N-m,

где N - количество каналов, обслуживаемых

устройством;

m - суммарное количество микрокомандных слов по все.м каналам, требую5щим адресации.

Условием работы устройства являются соотношения:

(Tc4+trj;

Т}п Тв,

где tj-вре.мя сквозного переноса в сумма0торе 6;

Tjn TB .

Для больщой детализации работы устройства микропрограммного управления рассмотрим каждый режим в отдельности.

5 В режиме последовательного формирования микропрограмм на счетчике 3 адреса фиксируется номер канала, для которого эта микропрогра.мма формируется.

Для простоты описания примем исходное состояние всех запоминающих элемен0 тов (счетчика 3 адреса, блока 5 памяти, регистра 7 адреса, регистра 9) равным нулю, а распределителя таким, чтобы он на перво.м выходе сформировал первый (СИ1) тактовый импульс.

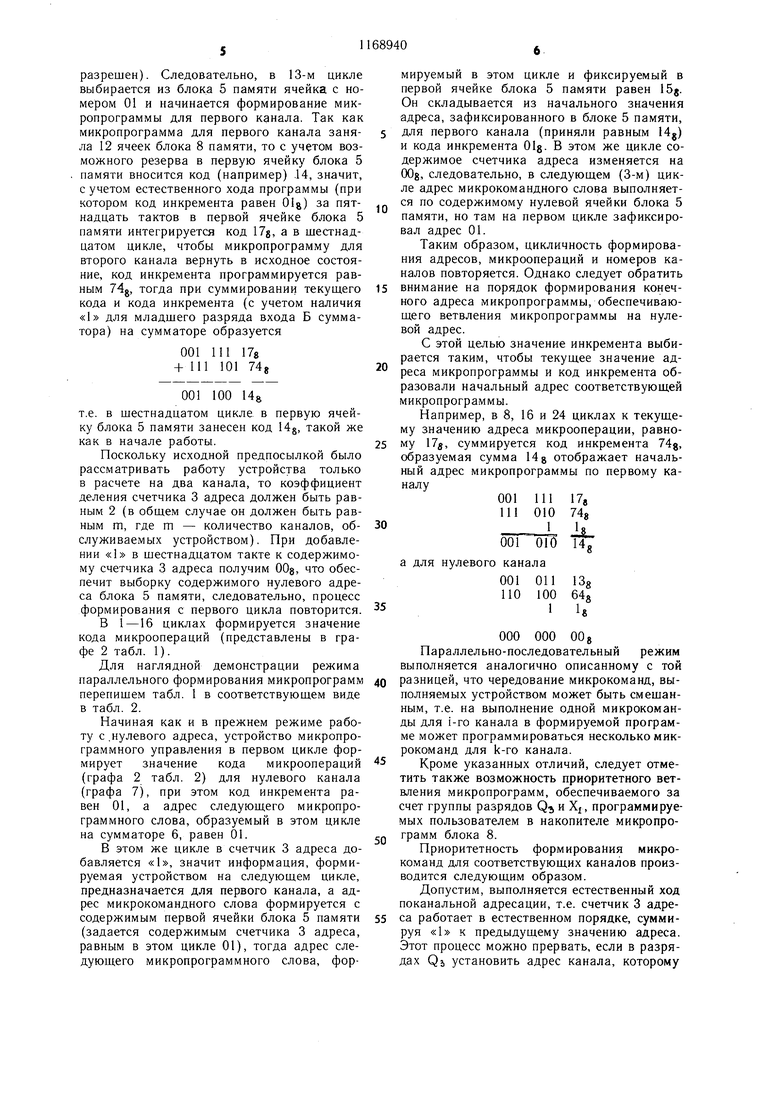

5 Рассмотрим формирование микропрограмм для двух каналов, каждая (микропрограмма) из которых состоит из восьми микропрограммных слов, причем первая микропрограмма формирует синусоидальный сигнал для нулевого канала, а вторая -

0 пилообразный сигнал для первого канала. Текст микропрограммы для этого случая представлен в табл. 1.

Как видно из табл. 1 в первом и последующих циклах (до 12) код инкремента равен 01 (восьмичный). Таким образом, начиная с нулевого значения адреса микропрограммных слов, в нулевой ячейке блока 5 памяти интегрируется код адреса блока 8 памяти микрокоманд с дискретностью 01 для того, чтобы вернуть эту микропрограмму на нулевой адрес в двенадцатом цикле, к текущему адресу (138) прибавлен код инкремента (64g) и единица к младшему разряду сумматора 6

001011

+ 138 4-110100 + 64

S

1

1

ООя

1000000

т.е. в двенадцатом цикле в нулевую ячейку блока 5 памяти заносится нулевой код адреса, и при возврате к нулевому каналу (содержимое счетчика 3 адреса равно «О) из нулевой ячейки блока 5 памяти выбирается нулевой код, значит процессы в первом, втором и т.д., циклах повторяются.

В двенадцатом цикле происходит суммирование единицы к содержимому счетчика 3 адреса (так как 1 и элемент И 4

разрешен). Следовательно, в 13-м цикле выбирается из блока 5 памяти ячейка с номером 01 и начинается формирование микропрограммы для первого канала. Так как микропрограмма для первого канала заняла 12 ячеек блока 8 памяти, то с учетом возможного резерва в первую ячейку блока 5 памяти вносится код (например) .14, значит, с учетом естественного хода программы (при котором код инкремента равен Olg) за пятнадцать тактов в первой ячейке блока 5 памяти интегрируется код 17g, а в шестнадцатом цикле, чтобы микропрограмму для второго канала вернуть в исходное состояние, код инкремента программируется равным 74g, тогда при суммировании текуш,его кода и кода инкремента (с учетом наличия «1 для младшего разряда входа Б сумматора) на сумматоре образуется

001 111 178 +111 101 748

001 100 14

т.е. в шестнадцатом цикле в первую ячейку блока 5 памяти занесен код 148, такой же как в начале работы.

Поскольку исходной предпосылкой было рассматривать работу устройства только в расчете на два канала, то коэффициент деления счетчика 3 адреса должен быть равным 2 (в общем случае он должен быть равным т, где m - количество каналов, обслуживаемых устройством). При добавлении «1 в шестнадцатом такте к содержимому счетчика 3 адреса получим ООд, что обеспечит выборку содержимого нулевого адреса блока 5 памяти, следовательно, процесс формирования с первого цикла повторится.

В 1-16 циклах формируется значение кода микроопераций (представлены в графе 2 табл. 1).

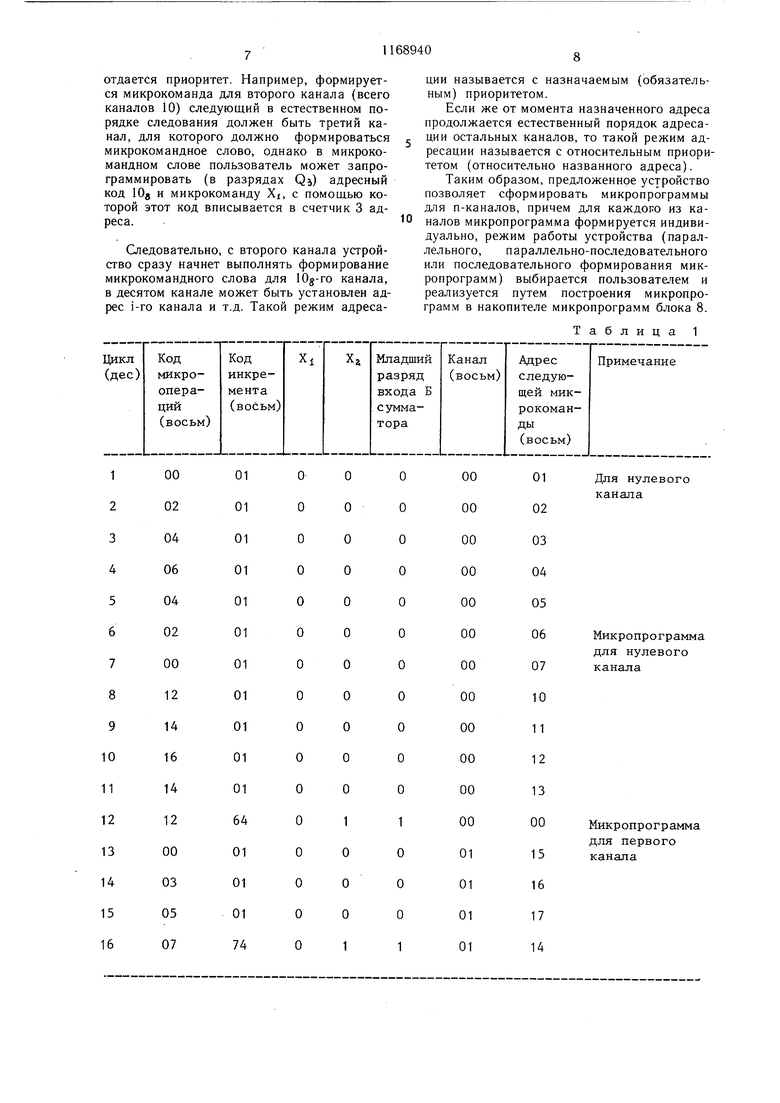

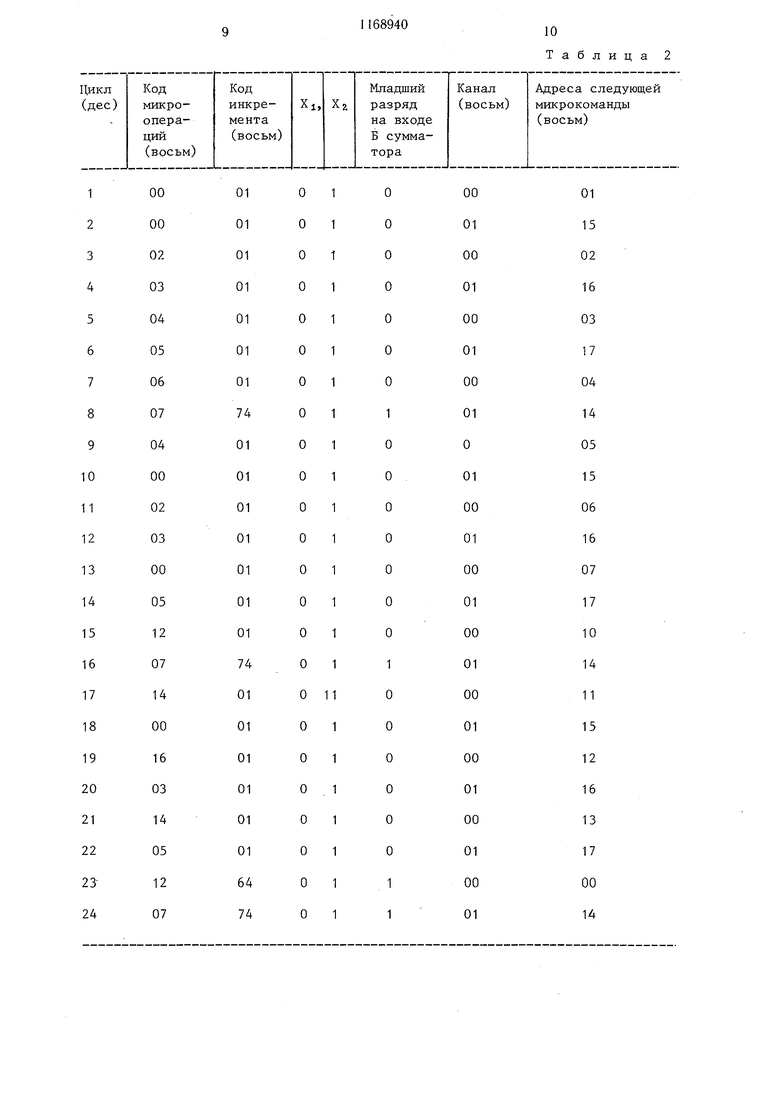

Для наглядной демонстрации режима параллельного формирования микропрограмм перепишем табл. 1 в соответствующем виде в табл. 2.

Начиная как и в прежнем режиме работу с .нулевого адреса, устройство микропрограммного управления в первом цикле формирует значение кода микроопераций (графа 2 табл. 2) для нулевого канала (графа 7), при этом код инкремента равен 01, а адрес следующего микропрограммного слова, образуемый в этом цикле на сумматоре 6, равен 01.

В этом же цикле в счетчик 3 адреса добавляется «1, значит информация, формируемая устройством на следующем цикле, предназначается для первого канала, а адрес микрокомандного слова формируется с содержимым первой ячейки блока 5 памяти (задается содержимым счетчика 3 адреса, равным в этом цикле 01), тогда адрес следующего микропрограммного слова, формируемый в этом цикле и фиксируемый в первой ячейке блока 5 памяти равен 15g. Он складывается из начального значения адреса, зафиксированного в блоке 5 памяти, для первого канала (приняли равным 14j) и кода инкремента Dig. В этом же цикле содержимое счетчика адреса изменяется на OOg, следовательно, в следующем (3-м) цикле адрес микрокомандного слова выполняется по содержимому нулевой ячейки блока 5 памяти, но там на первом цикле зафиксировал адрес 01.

Таким образом, цикличность формирования адресов, микроопераций и номеров каналов повторяется. Однако следует обратить внимание на порядок формирования конечного адреса микропрограммы, обеспечивающего ветвления микропрограммы на нулевой адрес.

С этой целью значение инкремента выбирается таким, чтобы текущее значение адреса микропрограммы и код инкремента образовали начальный адрес соответствующей микропрограммы.

Например, в 8, 16 и 24 циклах к текущему значению адреса микрооперации, равному 7g, суммируется код инкремента 74, образуемая сумма 14 g отображает начальный адрес микропрограммы по первому каналу

001 111 17g 111 010 748

il.

001 010 14

о

а для нулевого канала

001 011 138 ПО 100 648

1 U

000 000 OOg

Параллельно-последовательный режим выполняется аналогично описанному с той разницей, что чередование микрокоманд, выполняемых устройством может быть смешанным, т.е. на выполнение одной микрокоманды для i-ro канала в формируемой программе может программироваться несколько микрокоманд для k-ro канала.

Кроме указанных отличий, следует отметить также возможность приоритетного ветвления микропрограмм, обеспечиваемого за счет группы разрядов Q и Xj, программируемых пользователем в накопителе микропрограмм блока 8.

Приоритетность формирования микрокоманд для соответствующих каналов производится следующим образом.

Допустим, выполняется естественный ход поканальной адресации, т.е. счетчик 3 адреса работает в естественном порядке, суммируя «1 к предыдущему значению адреса. Этот процесс можно прервать, если в разрядах QJ, установить адрес канала, которому

отдается приоритет. Например, формируется микрокоманда для второго канала (всего каиалов 10) следующий в естественном порядке следования должен быть третий канал, для которого должно формироваться микрокомандное слово, однако в микрокомандном слове пользователь может запрограммировать (в разрядах Qj) адресный код lOg и микрокоманду Xj, с помощью которой этот код вписывается в счетчик 3 адреса.

Следовательно, с второго канала устройство сразу начнет выполнять формирование микрокомандного слова для lOg-ro канала, в десятом канале может быть установлен адрес i-ro канала и т.д. Такой режим адресации называется с назначаемым (обязательным) приоритетом.

Если же от момента назначенного адреса продолжается естественный порядок адресации остальных каналов, то такой режим адресации называется с относительным приоритетом (относительно названного адреса).

Таким образом, предложенное устройство позволяет сформировать микропрограммы для п-каналов, причем для каждого из каналов микропрограмма формируется индивидуально, режим работы устройства (параллельного, параллельно-последовательного или последовательного формирования микропрограмм) выбирается пользователем и реализуется путем построения микропрограмм в накопителе микропрограмм блока 8.

Таблица 1

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство адресации многопроцессорной вычислительной машины | 1983 |

|

SU1129613A1 |

| Микропрограммное устройство управления | 1987 |

|

SU1490676A1 |

| Многоканальное устройство для сопряжения ЭВМ | 1988 |

|

SU1695311A1 |

| Устройство для формирования характеристических матриц | 1988 |

|

SU1596334A1 |

| Многоканальный микропрограммный счетчик | 1985 |

|

SU1280598A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для приема заказов | 1985 |

|

SU1316020A1 |

| Устройство для сопряжения двух магистралей | 1989 |

|

SU1615730A2 |

| Микропрограммное устройство управления | 1985 |

|

SU1367013A1 |

| Устройство для сопряжения двух магистралей | 1988 |

|

SU1509915A2 |

МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ, содержащее генератор тактовых импульсов, распределитель импульсов, регистр микрокоманд, блок памяти микрокоманд и счетчик адреса, причем группа выходов кода микроопераций регистра микрокоманд является группой выходов устройства, группа информационных входов регистра микрокоманд соединена с группой выходов кода операций блока памяти микрокоманд, вход записи регистра микрокоманд соединен с первым выходом распределителя импульсов, вход которого соединен с выходом генератора тактовых импульсов, отличающееся тем, что, с целью сокращения оборудования, оно содержит блок памяти адресов, сумматор, регистр адреса и элемент И, причем второй выход распределителя импульсов соединен с первым входом элемента И и с входами записи регистра адреса и блока памяти адресов, вход чтения которого соединен с первым выходом распределителя импульсов, выход признака режима регистра микрокоманд соединен с вторым входом элемента И, выход которого соединен со счетным входом счетчика адреса, группа информационных входов которого соединена с группой выходов кода ветвления микропрограмм блока памяти микрокоманд, выход признака ветвления которого соединен с входом записи счетчика адреса, группа информационных вы-ходов которого соединена с группой адресных входов блока (О памяти адресов, группа информационных (Л входов которого соединена с группой выходов сумматора, первая группа входов которого соединена с группой выходов кода модификации адреса блока памяти микрокоманд, группа адресных входов которого соединена с второй группой входов сумматора и с группой выходов регистра адреса, группа информационных входов которого соедиО5 нена с группой выходов блока памяти ад00 ресов. г 4

Для нулевого канала

Микропрограмма для нулевого канала

Микропрограмма для первого канала

Таблица 2

.2

| 0 |

|

SU342380A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| МИКРОПРОГРАММНОЕ УСТРОЙСТВО УПРАВЛЕНИЯ | 0 |

|

SU331387A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-07-23—Публикация

1984-02-28—Подача