00 05 ;О

Nti

I - О

15, коммутаторы 4, 11 и 22, Б 16 формирования импульсов, Б 33 управления, элементы И 17-21, и шертор 34, сумматор 28, счетчики 5 и 6, генератор 12 псевдослучайных кодов, Б 31 начальной установки, дешифратор 23, регистр 24 пороговых значений, мультиплексоры 13, 25 и 26, демультиплек- сор 27, Б 29 памяти, цифроаналоговый

138

преобразователь 50 и Б 33 управления- В описании изобретения даны электрические схемы сумматора 28, Б 29 памяти, Б 33 управления, генератора 12 псевдослучайных кодов. Устройство имеет повышенную точность определения границ областей работоспособности за счет учета воздействия случайных возмущений. 7 ил., 1 табл.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для определения области работоспособности электронных схем | 1985 |

|

SU1273853A1 |

| Устройство для контроля цифровых блоков | 1984 |

|

SU1238082A1 |

| Устройство для регистрации информации | 1985 |

|

SU1304170A1 |

| Устройство для контроля цифровых узлов | 1983 |

|

SU1124312A1 |

| Устройство для контроля логических блоков | 1986 |

|

SU1386998A1 |

| Устройство для задания тестовых воздействий | 1988 |

|

SU1541614A1 |

| Устройство для контроля цифровых блоков | 1985 |

|

SU1260961A1 |

| МОНОИМПУЛЬСНАЯ РАДИОЛОКАЦИОННАЯ СИСТЕМА ОБНАРУЖЕНИЯ И САМОНАВЕДЕНИЯ | 2010 |

|

RU2439608C1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1352624A1 |

| Сигнатурный анализатор | 1989 |

|

SU1756890A1 |

Изобретение относится к области контрольно-измерительной техники. Устройство для определения области работоспособности радиоэлектронных схем содержит блок (Б) 32, индикации; генератор 2 синхроимпульсов, делитель 3 частоты, преобразователи 7-10 воз- муп;ений, Б 14 анализа, логический Б

Изобретение относится к контрольно-измерительной технике и может быть использовано для контроля работоспособности радиоэлектронных схем.

Цель изобретения - повышение точности определения границ областей работоспособности за счет учета воздействия случайных возмущений.

На фиг. 1 приведена блок-схема устройства; на фиг, 2 и 3 - временные диаграммы работы устройства; . на (}«г. 4 - схема сумматора; на фиг. 5 - схема блока памяти; на фиг. 6 - схема блока управления; на фиг. 7 - схема генератора псевдослучайных кодов.

Устройство для определения области работоспособности радиоэлектронной схемы 1 содержит генератор 2 синхроимпульсов, делитель 3 частоты, первьш коммутатор 4, первый 5 и второй 6 счетчики, первый 7, второй 8, третий.9 и четвертый 10 преобразователи возмущений, второй коммутатор 11,:генератор 12 псевдослучайных кодовj первьй мультиплексор. 13, блок 14 анализа, логический блок 15, блок 16 формирования импульсов, первый 17, второй 18, третий 19, четвертый 20 и пятый 21 элементы И, третий коммутатор 22, дешифратор 23, регистр 24 пороговых значений, второй 25 и третий 26 мультиплексоры, демультиплексор 27, сумматор 28, блок 29 памяти, цифроаналоговьй преобразователь 30, блок 31 начальной установки, блок 32 индикации, блок 33 управления и инвертор 34,

Сумматор 28 содержит комбинационный сумматор 35, третий счетчик 36,

одновибратор 37, шестой элемент И 38 и одновибратор 39-.

Блок 29 памяти содержит накопитель 40, первьй 41 и второй 42 дешифраторы адреса и блок 43 записи-считывания.

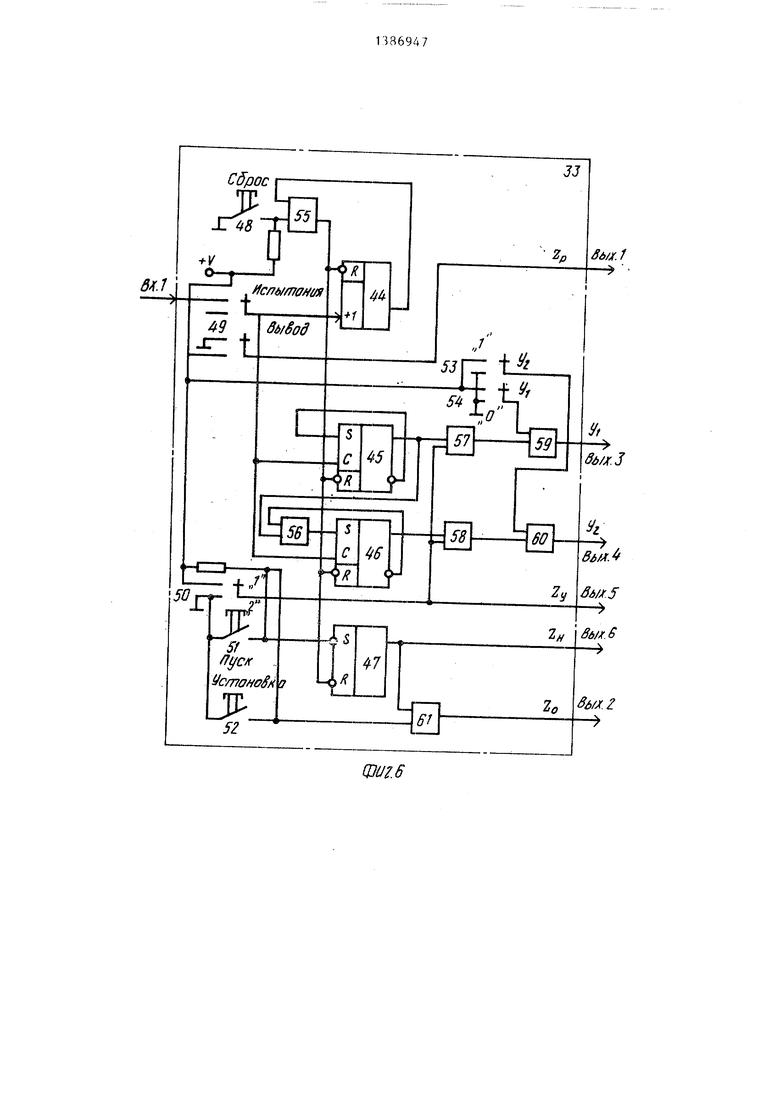

Блок 33 управления содержит .четвер- тьй счетчик 44, первьй 45, второй 46 и третий 47 триггеры, первую кнопку 48, первьй 49 и второй 50 переключатели, вторую 51 и третью 52 кнопки, третий 53 и четвертьй 54 переключатели, седьмой 55, восьмой 56,.девятьй 57 и десятый 58 элементы И, первьй 59, второй 60 и третий 61 элементы ИЛИ.

Генератор 12 псевдослучайных кодов содержит первьй 62, второй 63, третий 64 и четвертьй 65 цифровые генераторы кодов,одиннадцатьй 66 и двенадцатьй 67 элементы И. Генераторы 62-65 построены на основе регистров 68-71 сдвига с обратной связью.

Генератор 2 синхроимпульсов соединен вькодом с входом делителя 3 частоты. Первьй 7, второй 8, третий 9 и четвертьй 10 преобразователи возмущений соединены выходами с соответствующими выходами устройства, входы которого соединены с соответствующими входами блока 14 анализа, соединенного выходами с соответствующими входами логического блока 15, выход которого соединен с первым входом блока 16 формирования импульсов. Первьй и второй выходы делителя 3 частоты соединены с одноименными входами первого коммутатора 4, соединенного управляющим входом с первым выходом блока 33 управления и с первыми входами первого 17 и второго 18

элементов И, выходом - с входом инвертора 34, с управляющим входом сумматора 28 и со счетным входом первого счетчика 5.

Установочньш вход первого счетчика 5 соединен с установочным входом второго счетчика бис вторым выходо блока 33 управления, вькод переноса с вторыг- входом первого элемента И 17 и со счетным входом второго счетчика 6, соединенного выходом переноса с вторым входом второго элемента И 18 и с первым входом блока 33 управления , соединенного третьим выходом с первым входом третьего элемент И 19 и четвертым выходом - с первым входом четвертого элемента И 20. Выход инвертора 34 соединен с вторым входом блока 16 формирования импуль- сов, соединенного выходом с суммирующим входом сумматора 28 и с вторыми входами третьего 19 и четвертого 20 элементов И, соединенньк выходами с первым и вторым информационными входами блока 29 памяти.

Цифроаналоговый преобразователь 3 выходом соединен с информационным входом второго коммутатора 11, соединенного первым, вторым и третьим выходами с соответствующими первым, вторым и третьим сигнальными входами блока 32 индикации, соединенного первым и вторым управляющими входами с выходами первого 17 и второго 18 элементов И, Первьй, второй, третий и четвертый выходы блока 31 начальной установки соединены с одноименными информационными входами генератора 12 псевдослучайных кодов, соединенного установочным входом с установочным входом регистра 24 пороговых значений и вторым выходом блока 33 управления, первым синхровходом

с выходом первого коммутатора 4, вто- дг импульсов, переключающим входом треТьего мультиплексора 26, первым выходом блока 33 управления и управляющим входом первого мультиплексора 13, соединенного первым и вторым выходами с соответствующими первым и вторым адресными входами блока 29 памяти. Третий и четвертый выходы блока 33 управления соединены соответственно с первым и вторым управляющими входами генератора 12 псевдослучайных кодов и с третьим и четвертым входами третьего коммутатора 22, соединенного управляющим входом с пятым выхорым синхровходом с выходом переноса первого счетчика 5, счетным входом второго счетчика 6 и вторым входом первого элемента И 17, третьим синхровходом - с выходом переноса второго счетчика 6, первым входом блока 33 управления и вторым входом второго элемента И 18.

Первый и второй выходы генератора 12 псевдослучайных кодов соединены с входами первого 7 и второго 8 преобразователей возмущения и первым

и вторым входами первого мультидлек- дом блока 33 управления. Вход регист

0

5

0

5

0

сора 13, соединенного третьим и четвертым входами с информационными выходами первого 5 и второго 6 счетчиков соответственно. Третий и четвер- тьш выходы генератора 12 псевдослучайных кодов соединены с входами третьего 9 и четвертого 10 преобразователей возмущения. Вход сумматора соединен с выходом второго мультиплексора 25, информационными входами соединенного с выходами регистра 24 порогового значения, а управляющими входами - с соответствующими управляющими входами третьего мультиплексора 26, демультиплексора 27, второго коммутатора 11 и выходами дешифратора 23, соединенного входами с выходами третьего коммутатора 22,

Вычитающий вход сумматора 28 соединен с первым выходом третьего мультиплексора 26, вторым выходом соединенного с входом цифроаналогового преобразователя 30. Выход сумматора - 28 соединен со входом демультиплексора 27, соединенного первым, вторым и третьим выходами соответственно с третьим, четвертым и пятым информационными входами блока 29 памяти, соединенного первым и вторым выходами с одноименными входами третьего коммутатора 22, а третьим, четвертым и пятым выходами - с первым, вторым и третьим входами третьего мультиплексора 26.

Управляющий выход сумматора 28 соединен с первым управляюп1им входом блока 29 памяти, соединенного вторым управляющим входом с выходом пятого элемента И 21, соединенного прямым входом с выходом инвертора 34 и вторым входом блока 16 формирования импульсов, а инверсным входом - с третьим входом блока 16 формирования

импульсов, переключающим входом тре

Тьего мультиплексора 26, первым выходом блока 33 управления и управляющим входом первого мультиплексора 13, соединенного первым и вторым выходами с соответствующими первым и вторым адресными входами блока 29 памяти. Третий и четвертый выходы блока 33 управления соединены соответственно с первым и вторым управляющими входами генератора 12 псевдослучайных кодов и с третьим и четвертым входами третьего коммутатора 22, соединенного управляющим входом с пятым выхоpa 24 пороговых значений соединен с пятым выходом блока 31 начальной установки, а шестой выход блока 33 управления - с управляющим входом талера- тора 2 синхроимпульсов.

Устройство работает следующим образом.

В первом режиме происходит генерация испытательных сигналов, поступающих на входные зажимы испытуемой ра-- диоэлектронной схемы 1, и определяется область работоспособности, информация о которой записывается в блок 29 памяти.

: Во втором режиме производится периодическое считывание этой информа- 1ЦИИ из блока 29 памяти и вывод изоб- 1 ажения области работоспособности на 2|кране блока 32 индикации.

; Режим генерации испытательных Сигналов разделяется на четыре перио- Да: а)начальная установка б) воздей- .4твие на схему 1 двух (I и II) воз- Нущений-, в) воздействие трех (I, II И III) возмущений; г) воздействие че- 1|ырех (I, II, III и IV) возмущений. Все указанные режимы реализуются поочередно.

Возмущения на испытуемую схему 1 поступают с выходов преобразователей 7-10 возмущений. В качестве возмущающих воздействий могут использоваться напряжения питания схемы, активная и реактивная нагрузка по входам и выходам схемы 1, аддитивные по- йеховые сигналы на информационных входах схемы 1 и т.п. Входными сигналами для преобразователей 7-10 явля- к)тся случайные цифровые коды, с выхо дов генер атора 12 псевдослучайных кодов, Каждьй из преобразователей 7-10 содержит цифроаналоговый преобразователь и нормирующий усилитель, что позволяет преобразовывать входной код в аналоговую величину возмущения.

Режим генерации испытательных сигналов начинается с начальной установки блоков устройства. Б момент време

ни tp по сигналу Сброс в блоке 33 управления на его шестом выходе вьфа батывается низкий уровень управляющего сигнала Z, который запрещает выработку импульсов в генераторе 2 синхроимпульсов (фиг. 26).

Б блоке 31 начальной установки производится набор четырех начальных значений кодов для каждой серии воз

,-

0 5

0

5

О 5

5

0

0

5

мущающих воздействий, а также набор параллельного цифрового кода, содержащего три компоненты: пороговые значения числа срабатывания схемы 1 для каждого из трех режимов испытаний. В момент времени t, по сигналу Установка в блоке 33 управления на его втором выходе вьфабатывается сигнал Z (фиг. 2а), устанавливающий в нуль счетчики 5 и 6 и разрешающий занесение начальных значений кодов в регистры генератора 12 псевдослучайных кодов и занесение кода пороговых значений в регистр 24 пороговых значений. При этом на третьем и четвертом выходах блока 33 управления устанавливаются нулевые уровни управляющих сигналов У, и У , запрещающих прохождение сигналов через элементы И 19 и 20 на блок 29 памяти .

Генератор 2 синхроимпульсов вьща- ет импульсы высокой частоты на вход делителя 3 частоты. На одном выходе делителя 3 частота импульсов соответствует частоте изменения величины первого возмущающего воздействия, на другом выходе - частоте, соответствующей выводу изображения на экран блока 32 индикации. В режиме генерации нулевой уровень сигнала Zp на первом выходе блока 33 управления запрещает прохождение импульсов через элементы И 17 и 18 на входы синхронизации блока 32 индикации, разреща-. ет прохождение через элемент И 21 сигналов на блок 29 памяти и подклю- ч.ч.:т вькод коммутатора 4 к первому . выходу делителя 3 частоты.

В момент времени t по сигналу Пуск в блоке 33 управления устанавливается единичньй уровень сигнала Z и начинается генерация синхроимпульсов в генераторе 2 (фиг. 26, д). Эти синхроимпульсы через делитель 3 и коммутатор 4 проходят на первый синхровход генератора 12 и на вход счетчика 5. В период времени to,t5 управляющие сигналы У, У 00, что соответствует воздействию только двух возмущений I и II (фиг. 2в, г) . Это достигается запрещением прохождения синхросигналов на третий 64 и четвертый 65 цифровые генераторы кодов в генераторе 12 псевдослучайных кодов.

В то же время на первом и втором выходах генератора 12 формируются случайные последовательности кодов

первого и второго возмущений (фиг, 2з, и). Одновременно счетчик 5 подсчитывает число сгенерированных кодов Нулевой уровень сигнала Zp подключает к выходам мультиплексора 13 первые два выхода генератора 12, В результате коды, определяющие возмущающие воздействия, определяют также и адреса ячеек в блоке 29 памяти, в которые записываются результаты испытаний схемы 1 под действием именно этих возмущений. При заполнении счетчика 5 на его выходе переноса появляется сигнал (фиг, 2е), который посту- з допуска блок 14 анализа вьщает сигпает на вход счетчика 6 и он подсчитывает число серий псевдослучайных последовательностей, сгенерированных на первом и втором выходах генератора 12,

При первом заполнении счетчика 6 в момент tg на его выходе переноса появляется сигнал (фиг. 2ж), которьм поступает на первый вход блока 33 управления и устанавливает управляю- щий сигнал Y, , равный 1 (фиг, 2в), Теперь разрешается прохождение синхросигналов через элемент И 66 на вход третьего цифрового генератора 64 кодов и на третьем выходе генератора 12 формируется случайная последовательность кодов возмущения III с частотой, равной частоте сигналов на выходе переноса счетчика 5 (фиг, 2к).

При втором заполнении счетчика 6 в момент времени tg на его выходе переноса появляется сигнал, которьй устанавливает в блоке 33 управления уп

равляющий сигнал Y, равный 1 (фиг, 2г), Теперь в генераторе 12 разрешается прохождение синхросигналов через элемент 67 на вход цифрового генератора 65 кодов и на четвертом выходе генератора 12 формируется случайная по-дс ствуют свои уровни возмущающих возследовательность кодов возмутцения IV с частотой, равной частоте сигналов на выходе переноса счетчика 6 (фиг, 2л) ,

Таким образом, в режиме генерации испытательных сигналов формируются сначала два случайных возмущения I и II с одинаковой частотой изменения. При этом в силу различных начальных кодов в цифровых генераторах 62 и 63 кодов и различного числа разрядов в регистрах 68 и 69 сдвига этих генераторов производится случайный перебор возможньгх комбинаций значений

50

55

действий и свои ячейки памяти в блоке 29 памяти. Это позволяет одновременно с испытанием схемы 1 записывать оценку ее работоспособности в блок 29 памяти.

Для этого в каждом такте по синхросигналу X с выхода коммутатора 4 после установления адресных кодов на входах блока 29 памяти на его выходах появляется содержимое выбранной ячейки памяти. Информация вг каждой ячейке памяти блока 29 записывается в трех информационных полях и одном

первого и. второго возмущений. В период t , tg действуют три возмущения, причем перебор значений первых двух возмущений повторяется. Аналогично при действии четырех возмущений повторяется перебор значений первых трех возмущений.

Блок 14 анализа производит пороговый контроль правильности функционирования схемы 1, анализируя состояние по каждому ее выходу отдельно. При нахождении параметров схемы в поле

0

5 О

5

0

нал на входы логического блока 15, реализующего функцию И, который формирует на своем выходе сигнал, принимающий единичное значение, когда радиоэлектронная схема 1 по всем выходам находится в области работоспособности. Этот сигнал поступает на пер- вьй вход блока 16 формирования импульсов функционирования, на второй . вход которого приходят синхроимпульсы, проинвертированные инвертором 34, а на третий вход - управляющий сигнал Zp. В результате выходные импульсы блока 16 свидетельствуют о работоспособности схемы 1 при данных возмущениях (фиг, Зг).

Для запоминания условия работоспособности испытуемой схемы 1 используется блок 29 памяти матричного типа. Первый выход генератора 12 псевдослучайных кодов в режиме генерации испытательных сигналов подключен через мультиплексор 13 к первому адресному

рходу блока 29 и определяет строку матрицы, второй выход генератора 12- к второму адресному входу и определяет столбец матрицы,

В результате каждому значению кодов на выходах генератора 12 соответствуют свои уровни возмущающих воз

действий и свои ячейки памяти в блоке 29 памяти. Это позволяет одновременно с испытанием схемы 1 записывать оценку ее работоспособности в блок 29 памяти.

Для этого в каждом такте по синхросигналу X с выхода коммутатора 4 после установления адресных кодов на входах блока 29 памяти на его выходах появляется содержимое выбранной ячейки памяти. Информация вг каждой ячейке памяти блока 29 записывается в трех информационных полях и одном

управляющем поле. Управляющее поле ячейки содержит два разряда кода идентификации,в которых записываются сигналы с выходов элементов И 1У и 20 . fia первые входы этих элементов поступают управляющие сигналы Y, и Уг, а на вторые входы - стробирующий сигнал с выхода блока 16 формирования импульсов. Если схе- ма 1 работоспособна в данньй момент, то блок 16 вырабатывает импульс, разрешающий запись кода Y,Y в управляющее поле ячейки памяти блока 29 и добавляющий единицу к коду числа срабатываний испытуемой схемы 1.

По синхросигналу X также происходит запись считанного кода из выбранного информационного поля ячейки памяти в счетчик 36 сумматора 28. При этом выбор нужного поля ячейки зависит от кода идентификации Y Y, т.е. от числа действующих в данньй момент на схему 1 возмущений„ Для этого сигналы Y( и.У, от блока 33 управления через коммутатор 22 поступают на дешифратор 23, на вьосоде которого появляется трехразрядный унитарньш код. Унитарн ый код поступает на управляющие входы мультиплексора 26, в результате чего на вычитающий вход сумматора 28 проходит нужное информационное поле содержимого ячейки памяти, содержащее число предыдущих срабатываний схемы 1 при данных значениях действующих возмущений. Если схема 1 работоспособна и в данный момент испытаний при тех же ниях, то по переднему фронту импуль

са блока 16 содержимое информацион

ного ПОЛЯ увеличивается на 1 в счетчике 36.

Инверсные выходы счетчика 36 подключены к одним входам комбинационного сумматора 35 (фиг. 4), на другие входы которого поступает код порого - вого значения для оценки работоспособности схемы 1. Три кода q , q,j, q.j пороговых значений хранятся в регистре 24. Пороговое значение, соответствующее данному сочетанию деист- вующих возмущений, считывается из регистра 24 через мультиплексор 25. В комбинационном сумматоре 35 сумматора 28 проходит вычитание числа срабатываний из порогового значения. Ее- ли разность отрицательна, на выходе переноса комбинационного сумматора 35 появляется сигнал, стробирующий про5

Q

о 5Q

35

40

45

55

хождение через элемент И 38 импульса С выхода одновибратора 37, который запускается сигналом с выхода блока 16. В результате формируется сигнал Zg записи кода идентификации Y, Y в блок 29 памяти. Следовательно, при. превьпиении числом срабатываний схемы заданного порога сигнал Zg свидетельствует о работоспособности схемы 1 при данном числе возмущающих воздействий. Тогда по сигналу Z (фиг. Зз, и) в управляющее Поле ячейки блока 29 памяти записывается код идентификации YjYj (фиг. 5), показывающий наибольшее число действующих возмущений, при которых испытуемая схема 1 еще ,работоспособна.

Код чиспа срабатываний схемы 1 с прямых выходов счетчика 36 сумматора

28через демультиплексор 27, управля- ёмый дешифратором 23, поступает в соответствующее информационное поле выбранной ячейки памяти блока 29 по сигналу записи с выхода элемента И

21 (фиг. 3 и 5).

Таким образом, режим генерации испытательных сигналов состоит из трех периодов: первьй период - действие двух возмущений, код идентификации Y, Y 00, второй период t, действие трех возмущений, код идентификации Y (Yj, 10, третий период - действие четырех возмущений, код Y,Y2 11. Третий период заканчивается по сигналу Сброс в блоке 33 уп- равления. После этого сигнал Z. О и генерация синхросигналов X прег- кращается. В блоке 33 управления производится подготовка к режиму считывания информации. Для этого кнопка 48 (фиг. 6) переводится в положение Вывод.

Вывод информации производится в двух подрежимах: 1 и 2. В подрежиме 1 считывается то информационное поле ячейки памяти, которое соответствует последнему значению кода идентификации, записанному в управляющем поле этой ячейки. Для этого единпчньй уровень управляющего сигнала Zu на пятом выходе блока 33 управления подключает к выходу коммутатора 22 первьй и второй выходы блока

29памяти. Выводимая область работоспособности в этом случае соответствует воздействию наибольшего числа возмущений, при котором схема 1 работоспособна при данных значениях возмущений.

В подрежиме 2 возможен вывод области работоспособности при заданном числе возмущений, устанавливаемьй оператором в блоке 33 управления. Для этого Z;. устанавливается равным О и на выход коммутатора 22 подключаются выходы блока 33, на которых с помощью переключателей 53 и 54 (фиг. 6) устанавливаются заданные значения кода идентификации.

Режим считывания информации начинается по сигналу Пуск в блоке 33 управления. Единичньй уровень сигнаZP подключает к выходу коммутато

4 второй выход делителя 3 частоты

ла

РЗ

на котором частота синхроимпульсов

соответствует частоте вывода точек изображения в блоке 32 индикации. Выходные коды счетчиков 5 и 6 используются для адресации ячеек в накопителе блока 29 и подключаются к его адресньпу входам через мультиплексор 13. В режиме считывания управляющий сигнал ZP с выхода блока 33 управления переключает вывод информации через мультиплексор 26 на выходы, подключенные к входам цифроаналогового преобразователя 30о Процесс записи в блок 29 памяти в этом режиме блокируется по инверсному входу элемента И 21 и запретом выработки импульсов блоке 16 формирования импульсов.

С выходов блока 29 в преобразователь 30 поступают параллельные пд1ф- ровые коды, содержащие информацию о работоспособности радиоэлектронной схемы 1. Выходное напряжение преобразователя 30 поступает -на вход коммутатора 11, на управляющие входы которого подается- унитарньй код идентификации с выходов дешифратора 23. В результате яркость точки изображения, выводимой в данньй момент, определяется: а) в подрежиме 1 - суммарным числом срабатываний схемы 1 при действии двух, трех и четырех возмущений, б) в подрежиме 2 - числом срабатываний схемы 1 при возмущениях, соответствующих заданному в блоке 33 управления коду идентификации. Цвет точки зависит от количества действовавших возмущений и представлен в таблице.

5

0

5

5

0

0

5

0

5

Так как яркость точки изображения пропорциональна числу срабатываний схемы 1, то восприятие яркости оператором не должно зависеть от цвета области работоспособности. Для этого коммутатор 11 содержит в каждом канале нормирующие усилители, коэффициенты усиления которых определяются из кривой относительной видности так, чтобы обеспечить одинаковое восприятие различных цветовых зон области работоспособности.

На фиг. 4 приведено возможное выполнение сумматора 28. Счетчик 36 служит для увеличения числа срабатываний схемы на 1, если схема 1 работоспособна и в данньй момент. Код числа срабатываний записывается в счетчик 36 по информационным входам D,-D при действии инверсного сигнала С, сформированного из синхросигнала X с задержкой на одновибраторе 39.

Если на выходе блока 16 появляется импульс, он поступает на счетньй вход счетчика 36 и передним фронтом увеличивает его содержимое на 1. Если схема 1 не работоспособнд, код в счетчике 36 не меняется. В комбинационном сумматоре 35 происходит сравнение числа срабатываний с пороговым значением. Одновибратор 37 задерживает сигнал от блока 16 на вход элемента И 38 для того, чтобы успело произойти сложение в счетчике 36. Сигнал переноса Р на выходе сумматора 35 возникает при переполнении, т,е. в том Случае, когда число срабатываний схемы 1 становится больще, чем пороговое значение. Это необходимо для повьшения достоверности информации о работоспособности испытуемой схемы 1.

На фиг. 5 приведено возможное выполнение блока 29 памяти. Запоминание информации происходит в накопителе

На фиг. 6 приведена схема блока 33 управления. Работа начинается с подачи сигнала Сброс от кнопки 48, при этом счетчик 44 и триггеры 45-47 устанавливаются в нуль и вы- рабатьшается нулевой уровень сигнала ZH на шестом выходе блока 33. Переключатель 49 переводится в положение Испытания и разрешает прохождение на счетньш вход счетчика 44 сигналов переноса с выхода счетчика 6. Сигнал Установка от кнопки 52 вьфабатьгоае на втором выходе блока 33 сигнал Zо, по которому производится занесение начальных кодов в генератор 12 и регистр 24 пороговых значений с

По сигналу Пуск от кнопки 51 устанавливается в единичное состояние триггер 47. В первьй период испытаний двухтактные триггеры 45 и 46 вырабатывают управляющий код YjY 00. По первому сигналу с выхода переноса счетчика 6, поступающего на вход блока 33, триггер 45 переводится в единицу и самоблокируется по входу (код Y,Y,j 10). По второму сигналу на входе блока 33 в единицу устанавливается триггер 46 и также самоблокируется (код Y,Y2 11). Счетчик 44 счи тает серии испытательных последовательностей по сигналам переноса счетчика 6. При переполнении счетчика 44 вырабатывается сигнал сброса и режим генерации испытательных сигналов пре кращается. Кроме того, режим .генерации может быть остановлен оператором при нажатии кнопки 48 Сброс.

В режиме счит1:тания информации переключатель 49 устанавливается в положение Вывод и по сигналу Пуск начинается процесс считывания. Код идентификации в подрежиме 2 устанавливается с помощью переключателей 53 и 54. Элементы И 57 и 58 в э.то время заперты низким уровнем от переключателя 50.

На фиг о 7 приведено возможное исполнение генератора 12 псевдослучайны кодов. Цифровые генераторы 62-65 кодов устанавливаются в начальное состояние по сигналу ZP, при эхом в них записываются коды с выходов блока 31 начальной установки. Цифровые генераторы кодов выполняются на основе регистров сдвига с обратной связью, синхронизация сдвигов произ- водится сигналами на синхровходах генератора 12 Элементы Vi 66 и 67 запрещают прохождение синхроимпульсов в соответствующие периоды испытаний.

Формула изобретения/

Устройство для определения области работоспособности радиоэлектронных схем, содержащее блок индикации, генератор синхроимпульсов, соединенньш выходом с входом делителя частоты, первый, второй, третий и четвертый преобразователи возмущений, соединенные выходами с соответствующими вы- , ходами устройства, входы которого соединены с соответствующими входами блока анализа, соединенного выходами с соответствующими входами логического блока, выход которого соединен с первым входом блока формирования импульсов, первый и второй выходы делителя частоты соединены с одноименными входами первого коммутатора, соединенного управляющим входом с первым выходом блока управления и с первыми входами первого и второго элементов И, выходом -- с входом инвертора, с управляющим входом сумматора и со счетным входом первого счетчика, соединенного установочным входом с установочным входом второго счетчика и с вторым выходом блока управленпя, выходом переноса - с вторым входом первого элемента И и со счетным -входом второго счетчика, соединенного выходом переноса с вторым входом второго элемента И и с первым входом блока управления, соединенного третьим вькодом с первым входом третьего элемента И и четвертым выходом - с первым входом четвертого элемента И, выход инвертора соединен с вторым входом блока формирования импульсов, соединенного выходом с суммирующим входом сумматора и с вторыми входами третьего и четвертого элементов И, соединенных выходами с пер- вым и вторым информационными входами блока памяти, цифроаналоговьй преобразователь, выходом соединенньм с информационным входом второго коммутатора, соединенного первым, вторым и третьим выходами с соответствующими первым, вторым и третьим сигнальными входами блока индикации, соединенного первым и вторым управляющими входами с выходами соответственно первого и второго элементов И, отличающееся тем, что, с целью повышения точности определения границ областей работоспособности, в него введены генератор псевдослучайных кодов, блок начальной установки, третий коммутатор, дешифратор, регистр пороговых значений, первый, второй и третий мультиплексоры, демультиплексор и пятьм элемент И, причем первый, Q ка памяти, соединенного вторым управвторои, третий и четвертьш выходы блока начальной установки соединены с одноименными информационными входами генератора псевдослучайных кодов, соединенного установочным входом с установочным входом регистра пороговых, значений и вторым выходом блока управления, первым синхровходом - с выходом первого коммутатора, вторым синхррвходом.- с выходом переноса первого счетчика, третьим синхровходом - с выходом переноса второго счетчика, первый и второй выходы генератора псевдослучайных кодов соединены соответственно с входами первого и второго преобразователей возмущения и первым и вторым входами первого мультиплексора, соединенного третьим и четвертым входами с информационными выходами первого и второго счетчиков соответственно, третий и четвертьш выходы генератора псевдо35

40

45

50

ляющим входом с выходом пятого мента И, соединенного прямым в с выходом инвертора а инверсн входом - с третьим входом блок мирования импульсов, переключаю входом третьего мультиплексора .первым выходом блока управлени равляющим входом первого мульт ра, соединенного первым и втор ходами с соответствующими перв вторым адресными - входами блока третий и четвертый выходы блок равления соединены соответстве первым и вторым управляющими в5 генератора псевдослучайных код третьим и четвертым входами тре коммутатора, соединенного управ щим входом с пятым выходом блок равления, соединенного шестым в с управляющим входом генератора хроимпульсов, вход регистра пор вых значений соединен с пятым в

случайных кодов соединены соответст- дом блока начальной установки.

венно с входами третьего и четвертог преобразователей возмущения, вход сумматора соединен с выходом второго мультиплексора, информационными входами соединенного с выходами регистра пороговых значений, а управляющими входаьда - с соответствуюютми управляющими входами третьего мультиплексора, демультиплексора, второго коммутатора и выходами дешифратора, соединенного, входами с выходами третьего коммутатора, вычитающий вход сумматора соединен с первым выходом третьего мультиплексора, вторым вькодом соединенного с входом цифроана- логового преобразователя, выход сумматора соединен с входом демульти- плексора, соединенного первым, вторым и третьим выходами соответственно с третьим, четвертым и пятым информационными входами блока памяти, соединенного первым и вторым выходами с одноименньми входами третьего коммутатора, а третьим, четвер тым и пятым выходами - с первым, вторым и третьим входами третьего мультиплексора, управляющий выход сумматора соединен с первым управляющим входом бло5

0

5

0

ляющим входом с выходом пятого элемента И, соединенного прямым входом с выходом инвертора а инверсным входом - с третьим входом блока формирования импульсов, переключающим входом третьего мультиплексора, с .первым выходом блока управления и управляющим входом первого мультиплексора, соединенного первым и вторым выходами с соответствующими первым и вторым адресными - входами блока мамяти, третий и четвертый выходы блока управления соединены соответственно с первым и вторым управляющими в5содами генератора псевдослучайных кодов и с третьим и четвертым входами третьего коммутатора, соединенного управляющим входом с пятым выходом блока управления, соединенного шестым выходом с управляющим входом генератора синхроимпульсов, вход регистра пороговых значений соединен с пятым выхо° 0 SI,

s л

г У

д / fieoexoe

ecv.s ffepexac

я Си.Б

, Лиг /Y/l8ьа.г

гск

выяЗ ГСК

вбцЛ гск

и

фиг. г

Вых.

.

25

Вых.

5л. т

35

СТ

А

Д

7

36

SM 35

Zs

На бходы

двмульт. 27

8й/х.З

щи 16

Составитель В.Савинов Редактор П.Гереши Техред Л. Сердюкова Корректор С.Шекмар

Заказ 1А93/45

Тир.аж 772

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская йаб., д. 4/5

.7

Подписное

| Устройство для измерения области работоспособности электронных схем | 1975 |

|

SU555353A1 |

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для определения области работоспособности электронных схем | 1985 |

|

SU1273853A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1988-04-07—Публикация

1986-10-20—Подача