4

00

Изобретение относится к в.ычисли- тельной технике и предназначено для использования в системах сбора и обработки информации с использованием преобразования биполярного кода в па- раллельньлй.

Цель из,обретения - расширение функциональных возможностей устройства.

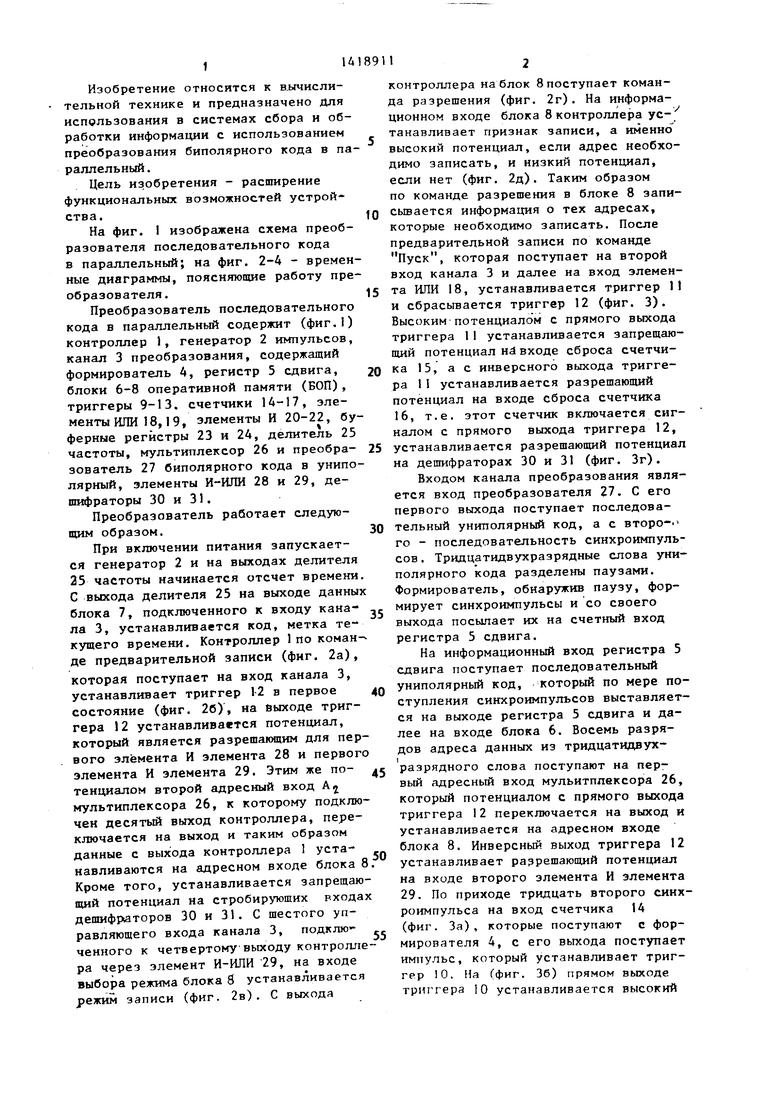

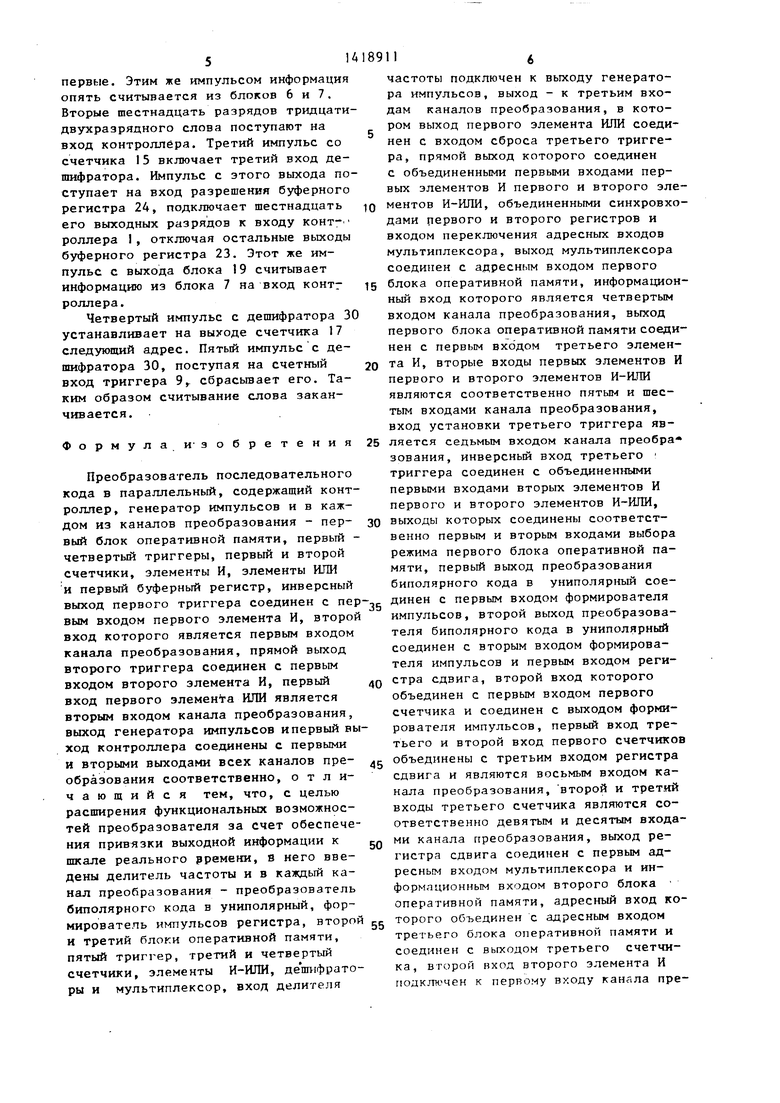

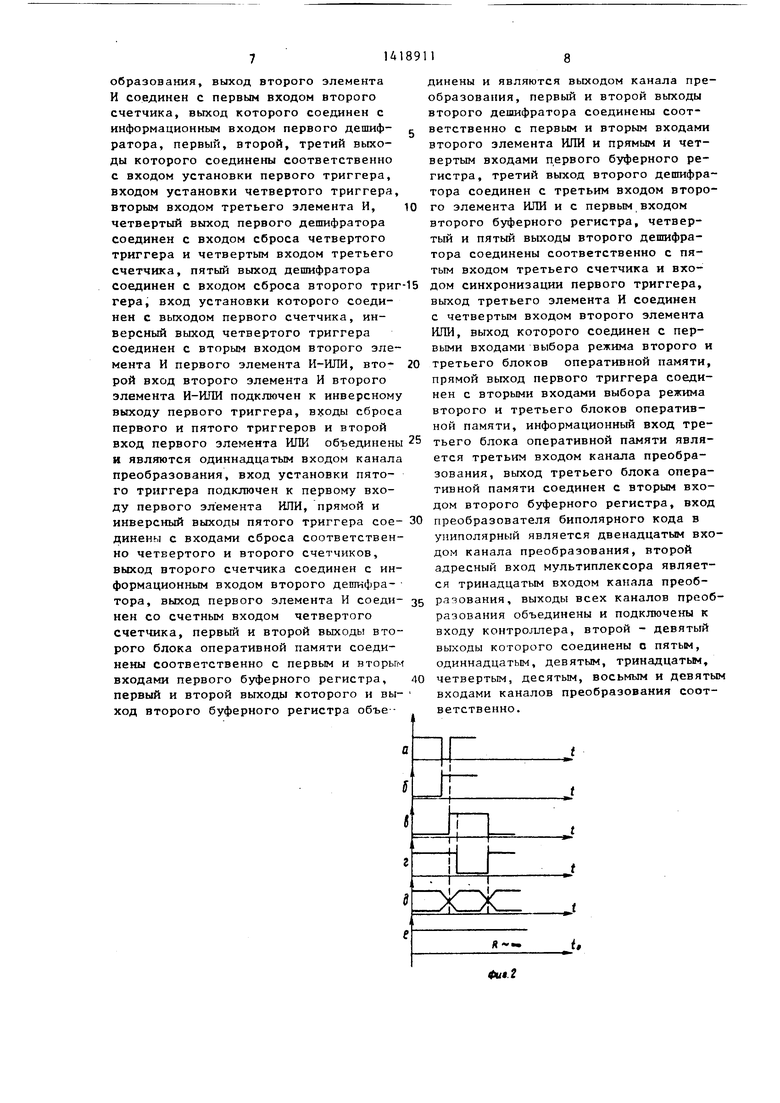

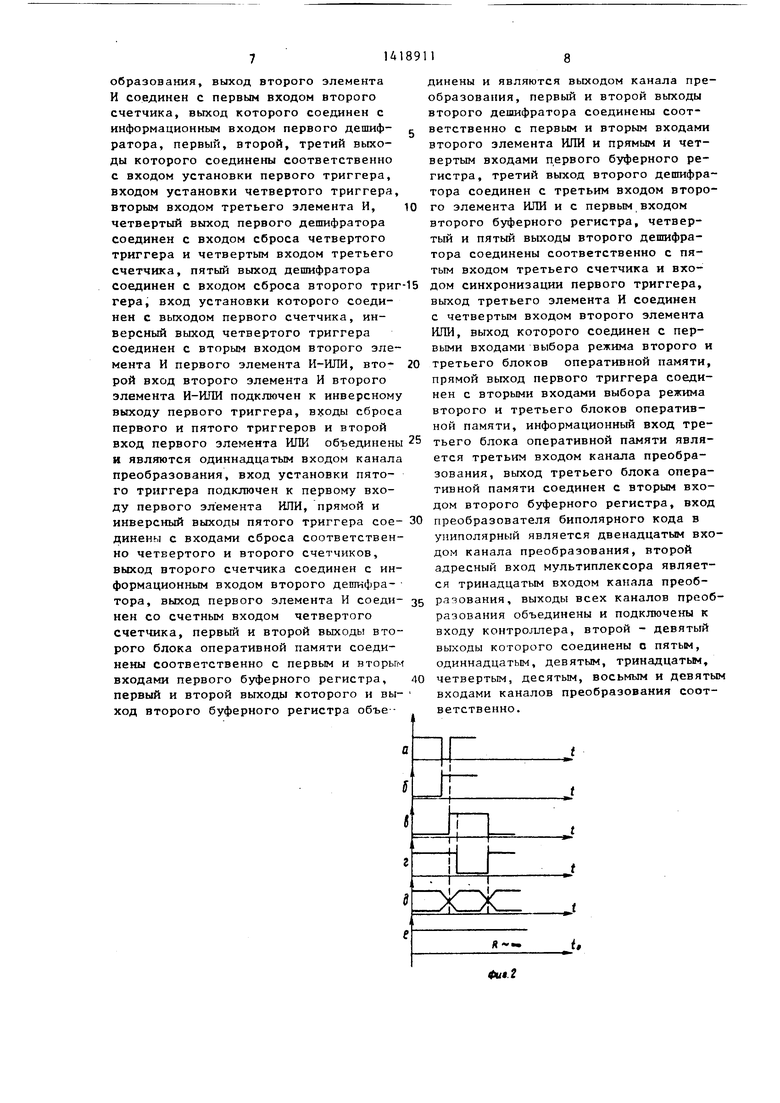

На фиг. I изображена схема преобразователя последовательного кода в параллельный; на фиг. 2-4 - временные диаграммы, поясняющие работу преобразователя.

Преобразователь последовательного кода в параллельный содержит (фиг.1) контроллер 1, генератор 2 импульсов, канал 3 преобразования, содержащий формирователь 4, регистр 5 сдвига, блоки 6-8 оперативной памяти (БОП), триггеры 9-13. счетчики 14-17, элементы ИЛИ 1 8, 1 9 , элементы И 20-22, буферные регистры 23 и 24, делитель 25

контроллера на блок В поступает команда разрешения (фиг. 2г). На информационном входе блока 8 контроллера ус- танавливает признак записи, а именнсГ высокий потенциал, если адрес необходимо записать, и низкий потенциал, если нет (фиг. 2д). Таким образом по команде разрешения в блоке 8 запиQ сьшается информация о тех адресах, которые необходимо записать. После предварительной записи по команде Пуск, которая поступает на второй вход канала 3 и далее на вход элемен5 та ИЛИ 18, устанавливается триггер 11 и сбрасывается триггер 12 (фиг. 3). Высоким потенциалом с прямого выхода триггера 11 устанавливается запрещающий потенциал ни входе сброса счетчи0 ка 15, ас инверсного выхода триггера 11 устанавливается разрешающий потенциал на входе сброса счетчика 16, т.е. этот счетчик включается сигналом с прямого выхода триггера 12,

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного кода в параллельный | 1988 |

|

SU1510099A1 |

| Преобразователь последовательного кода в параллельный | 1984 |

|

SU1231613A1 |

| УСТРОЙСТВО ИЗМЕРЕНИЯ ПАРАМЕТРОВ ТЕЛЕВИЗИОННЫХ ОПТИЧЕСКИХ СИСТЕМ | 1991 |

|

RU2010448C1 |

| Устройство для программного управления процессами | 1986 |

|

SU1328795A1 |

| Кольцевая система для обмена информацией | 1988 |

|

SU1550522A1 |

| Измеритель частоты | 1989 |

|

SU1691768A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Информационно-измерительное устройство | 1985 |

|

SU1256074A1 |

| Устройство для управления распределенными объектами | 1985 |

|

SU1290261A1 |

| Устройство для сопряжения оконечного устройства с мультиплексным каналом передачи информации | 1987 |

|

SU1538172A1 |

Изобретение относится к вычис лительной технике. Цель изобретения - расширение функциональных возможностей преобразователя последовательного кода в параллельный. Преобразователь последовательного кода в параллельный содержит контроллер 1, генератор 2 импульсов, канал 3 преобразования, содержащий формирователь 4, регистр 5 сдвига, блоки 6-8 оперативной памяти, триггеры 9-13, счетчики 14-17, элементы ИЛИ 18 и 19, элементы И 20-22, буферные регистры 23, 24, делитель 25 частоты, мультиплексор 26, преобразователь 27 биполярного кода в униполярный, элементы И-1ШИ 28 и 29, дегаифраторьГ 30, 31. 4 ил.

частоты, мультиплексор 26 и преобра- 25 устанавливается разрешающий потенциал зователь 27 биполярного кода в унипо- на дешифраторах 30 и 31 (фиг. Зг). лярный, элементы И-ИЛИ 28 и 29, деВходом канала преобразования является вход преобразователя 27. С его первого выхода поступает последова- 30 тельный униполярный код, а с второ-| го - последовательность синхроимпульсов. Тридцатидвухразрядные слова униполярного кода разделены паузами. Формирователь, обнаружив паузу, форшифраторы 30 и 31.

Преобразователь работает следующим образом.

При включении питания запускается генератор 2 и на выходах делителя 25 частоты начинается отсчет времени. С выхода делителя 25 на выходе данных

блока 7, подключенного к входу кана- - мирует синхроимпульсы и со своего ла 3, устанавливается код, метка те-

кущего времени. Контроллер 1 по коман- де предварительной записи (фиг. 2а), которая поступает на вход канала 3, устанавливает триггер 12 в первое до состояние (фиг. 2б), на выходе триггера 12 устанавливается потенциал, который является разрешающим для первого элемента И элемента 28 и первого элемента И элемента 29. Этим же по- д теициапом второй адресный вход А мультиплексора 26, к которому подключен десятый выход контроллера, переключается на выход и таким образом данные с выхода контроллера 1 уста- навливаются на адресном входе блока 8. Кроме того, устанавливается запрещающий потенциал на стробирующих входах дешифраторов 30 и 31. С шестого управляющего входа канала 3, подклю- ченного к четвертому выходу контроллера через элемент И-ИЛИ 29, на входе выбора режима блока 8 устанавливается режим записи (фиг. 2в). С выхода

выхода посылает их на счетный вход регистра 5 сдвига.

На информационный вход регистр сдвига поступает последовательный униполярный код, который по мере ступления синхроимпульсов выставл ся на выходе регистра 5 сдвига и д лее на входе блока 6. Восемь разр дов адреса данных из тридцатидвух I

разрядного слова поступают на пер вый адресный вход мульитппексора который потенциалом с прямого вых триггера 12 переключается на выход устанавливается на адресном входе блока 8. Инверсный выход триггера устанавливает раэрешаюошй потенци на входе второго элемента И элеме 29. По приходе тридцать второго си ро1 мпульса на вход счетчика 14 (фиг. За), которые поступают с фо мирователя 4, с его выхода поступа импульс, который устанавливает три гер 10. На (фиг. Зб) прямом выходе триггера 10 устанавливается высоки

устанавливается разрешающий потенциал на дешифраторах 30 и 31 (фиг. Зг).

Входом канала преобразования является вход преобразователя 27. С его первого выхода поступает последова- тельный униполярный код, а с второ-| го - последовательность синхроимпульсов. Тридцатидвухразрядные слова униполярного кода разделены паузами. Формирователь, обнаружив паузу, формирует синхроимпульсы и со своего

выхода посылает их на счетный вход регистра 5 сдвига.

На информационный вход регистра 5 сдвига поступает последовательный униполярный код, который по мере поступления синхроимпульсов выставляется на выходе регистра 5 сдвига и далее на входе блока 6. Восемь разрядов адреса данных из тридцатидвух- I

разрядного слова поступают на первый адресный вход мульитппексора 26, который потенциалом с прямого выхода триггера 12 переключается на выход и устанавливается на адресном входе блока 8. Инверсный выход триггера 12 устанавливает раэрешаюошй потенциал на входе второго элемента И элемента 29. По приходе тридцать второго синх- ро1 мпульса на вход счетчика 14 (фиг. За), которые поступают с формирователя 4, с его выхода поступает импульс, который устанавливает триггер 10. На (фиг. Зб) прямом выходе триггера 10 устанавливается высокий

потенциал, который поступает на вход элемента И 22. На второй вход элемента И 22 поступает частота с генератора 2. По приходе потенциала с десятого выхода импульсы начинают поступать на вход счетчика 16, с выхода счетчика, поступая на вход дешифратора 31 (фиг. Зв), включают его первый выход. Импульс с первого выхода дешифратора устанавливает триггер 9. Прямой выход триггера 9 устанавливает потенциал, определяющий режим записи на входах режима блоков 6 и 7 (фиг. Зг). На их адресных входах устанавливается адрес с выхода счетчика 17 (фиг. Зг), физический адрес на счетчик 17 устанавливается с седьмого выхода контроллера, подключенного к девятому входу канала 3. Команда записи адреса поступает с выхода контроллера, подключенного к десято 1у входу канала 3.

Потенциал с инверсного выхода триггера 9 через элемент 29 поступает на вход режима блока 8 (фиг. Зд), уста- навливая на этом входе режим считывания, -Второй импульс со счетчика 16 включает второй выход дешифратора 31 (фиг. Зв). Импульс со второго выхода дешифратора, поступая на вход уста- новкн триггера 13, взводит его. Инверсный выход триггера 13 через второй элемент 28 подключен в режиме записи к входу разрешения блока 8. Импульс с второго выхода дешифратора формирует передний фронт сигнала разрешения для блока В (фиг. Зж). Третий импульс с выхода дешифратора 31 поступает на второй вход элемента 20. К этому времени с выхода блока 8 при- ходит признак записи данных, записанный предварительно в блок 8. В случае, если признак записи адреса обозначен высоким уровнем, импульс проходит на выход элемента 20 и далее че- рез элемент 19 на .вход разрешения блоков 6 и 7 (фиг. 3,4). Таким образом производится запись данных в блок 6 и время записи э блок 7. Импульс с четвертого выхода дешифратора 31 поступает на счетный вход +1 счетчика 17 и устанавливает на его выходе следующий адрес. Этим же импульсом сбрасывается триггер 13 и формируется задний фронт сигнала разрешения на входе разрешения блока В (фиг.3.ж,в). Пятый импульс со счетчика 16 включает пятый выход дешифратора 31. Импульс с этого выхода поступает на вход сбро

5 о о g g

5

0

11 4

са триггера 10 и сбрасьшает его (фиг. Зб).

На его прямом выходе формируется потенциал, который запрещает прохождение частоты на вход элемента И 22. Процесс записи тридцатидвухразрядного слова закончен./

Команда считьгоания поступает на вход элемента ИЛИ 18 с девятого управляющего выхода контроллера, подключенного к одиннадцатому входу канала 3, и на вход сброса триггеров 11 и 12.

Потенциал с прямого выхода триггера 11 поступает на вход сброса счетчика 15 и разрешает его работу, в то время как с инверсного выхода запрещает работу счетчика 16. С выхода элемента ИЛИ 18 импульс поступает на вход сброса триггера 12. В результате на прямом выходе триггера устанавливается потенциал, который, поступая на вход стробирования дешифраторов 30 и 31, разрешает их работу. Кроме того, команда считьшания включает инверсный выход триггера 9 (фиг. 4а). Потенциал с инверсного выхода триггера 9 г оступает на первый вход элемента 21 и разрешает прохождение частоты с его второго входа на выход. На прямом выходе триггера 9 устанавливается потенциал, определяющий режим считывания для блокор 6 и 7. С выхода элемента И 21 импульсы поступают на вход счетчика 15. Первый импульс с выхода этого счетчика включает первый выход дешифратора 30 (фиг. 46). Импулье с этого выхода поступает на первый вход разрешения буферного регистра 23 и подключает шестнадцать выходных шин этого регистра к входу контролера,одновременно с этим поступая ни вход элемента ИЛИ 19 и далее с его выхода на входы разрешения блоков 6 и 7. Информация, записанная по адресу,.установленному на счетчике 17, устанавливается на вьтходах блоков 6 и 7 и таким образом шестнадцать первых разрядов подключаются к входу контроллера 1 (фиг. 4в).

Второй импульс с счетчика 15 включает второй выход дешифратора 30. Импульс с этого выхода включает второй вход разрешения буферного регистра 23, подключая вторые шестнадцать разрядов к входу контроллера и отключая

51

первые. Этим же импульсом информация опять считывается из блоков 6 и 7. Вторые шестнадцать разрядов тридцатидвухразрядного слова поступают на вход контроллера. Третий импульс со счетчика 15 включает третий вход дешифратора. Импульс с этого выхода поступает на вход разрешения буферного регистра 24, подключает шестнадцать его выходных разрядов к входу конт- роллера I, отключая остальные выходы буферного регистра 23. Этот же импульс с выхода блока 19 считьгаает информацию из блока 7 на вход контг роллера.

Четвертый импульс с дешифратора 3 устанавливает на выходе счетчика 17 следующий адрес. Пятый импульс с де- пшфратора 30, поступая на счетный вход триггера 9 сбрасьшает его. Таким образом считывание слова заканчивается.

Формулаи зобретения

Преобразователь последовательного кода в параллельный, содержащий контроллер, генератор импульсов и в каждом из каналов преобразования - первый блок оперативной памяти, первый - четвертый триггеры, первый и второй счетчики, элементы И, элементы ИЛИ и первый буферный регистр, инверсный выход первого триггера соединен с первым входом первого элемента И, второй вход которого является первым входом канала преобразования, прямой выход второго триггера соединен с первым входом второго элемента И, первый вход первого элемента ИЛИ является вторым входом канала преобразования, выход генератора импульсов и первый выход контроллера соединены с первыми и вторыми выходами всех каналов преобразования соответственно, отличающийся тем, что, с целью расширения функциональных возможностей преобразователя за счет обеспечения привязки выходной информации к шкале реального рремени, в него введены делитель частоты и в каждый канал преобразования - преобразователь биполярного кода в униполярный, формирователь импульсов регистра, второй и третий блоки оперативной памяти, пятый триггер, третий и четвертый счетчики, элементы И-ИЛИ, де шифрато- ры и мультиплексор, вход делителя

116

частоты подключен к выходу генератора импульсов, выход - к третьим входам каналов преобразования, в котором выход первого элемента ИЛИ соединен с входом сброса третьего триггера, прямой выход которого соединен с объединенными первыми входами первых элементов И первого и второго элементов И-ИЛИ, объединенными синхровхо- дами первого и второго регистров и входом переключения адресных входов мультиплексора, выход мультиплексора соединен с адресным входом первого

блока оперативной памяти, информационный вход которого является четвертым входом канала преобразования, выход первого блока оперативной памяти соединен с первым входом третьего элемента И, вторые входы первых элементов И первого и второго элементов И-ИЛИ являются соответственно пятым и шестым входами канала преобразования, вход установки третьего триггера является седьмым входом канала преобра зования, инверсный вход третьего триггера соединен с объединенными первыми входами вторых элементов И первого и второго элементов И-ИПИ,

выходы которых соединены соответственно первым и вторым входами выбора режима первого блока оперативной памяти, первый выход преобразования биполярного кода в униполярт)1Й соединен с первым входом формирователя импульсов, второй выход преобразователя биполярного кода в униполярный соединен с вторым входом формирователя импульсов и первым входом регистра сдвига, второй вход которого объединен с первым входом первого счетчика и соединен с выходом формирователя импульсов, первый вход третьего и второй вход первого счетчиков

объединены с третьим входом регистра сдвига и являются восьмым входом канала преобразования, второй и третий входы третьего счетчика являются соответственно девятым и десятым входами канала преобразования, выход регистра сдвига соединен с первым адресным входом мультиплексора и информационным входом второго блока оперативной памяти, адресный вход которого объединен с адресным входом третьего блока оперативной памяти и соединен с вьгходом третьего счетчика, второй вход второго элемента И подключен к первому входу канала преобразования, выход второго элемента И соединен с первым входом второго счетчика, выход которого соединен с информационным входом первого дешифратора, первый, второй, третий выходы которого соединены соответственно с входом установки первого триггера, входом установки четвертого триггера вторым входом третьего элемента И, четвертый выход первого дешифратора соединен с входом сброса четвертого триггера и четвертым входом третьего счетчика, пятый выход дешифратора

соединен с входом сброса второго триг-15 дом синхронизации первого триггера.

гера, вход установки которого соединен с выходом первого счетчика, инверсный выход четвертого триггера соединен с вторым входом второго элемента И первого элемента И-ИЛИ, вто- 20 рой вход второго элемента И второго элемента И-ИЛИ подключен к инверсному выходу первого триггера, входы сброса первого и пятого триггеров и второй

вход первого элемента ИЛИ объединены 25 тьего блока оперативной памяти является третьим входом канала преобразования, выход третьего блока оперативной памяти соединен с вторым входом второго буферного регистра, вход

инверсный выходы пятого триггера сое- 30 преобразователя биполярного кода в

и являются одиннадцатым входом канала преобразования, вход установки пятого триггера подключен к первому входу первого элемента ИЛИ, прямой и

динены с входами сброса соответственно четвертого и второго счетчиков, выход второго счетчика соединен с информационным входом второго дешифра- тора, выход первого элемента И соединен со счетным входом четвертого счет шка, первый и второй выходы второго блока оперативной памяти соединены соответственно с первым и вторьм входами первого буферного регистра, первый и второй выходы которого и выход второго буферного регистра объе

динены и являются выходом канала преобразования, первый и второй выходы второго дешифратора соединены соответственно с первым и вторым входами второго элемента ИЛИ и прямым и четвертым входами первого буферного регистра, третий выход второго дешифратора соединен с третьим входом второго элемента ИЛИ и с первым входом второго буферного регистра, четвертый и пятый выходы второго дешифратора соединены соответственно с пятым входом третьего счетчика и вховыход третьего элемента И соединен с четвертым входом второго элемента ИЛИ, выход которого соединен с первыми входами выбора режима второго и третьего блоков оперативной памяти, прямой выход первого триггера соединен с вторыми входами выбора режима второго и третьего блоков оперативной памяти, информационный вход треуниполярный является двенадцатым входом канала преобразования, второй адресный вход мультиплексора является тринадцатым входом канала преобразования, выходы всех каналов преобразования объединены и подключены к входу контроллера, второй - девятый выходы которого соединены с пятым, одиннадцатым, девятым, тринадцатым,

четвертым, десятым, восьмым и девятым входами каналов преобразования соответственно.

5

,

6

- .З

| Преобразователь последовательного кода в параллельный | 1984 |

|

SU1231613A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1988-08-23—Публикация

1987-01-13—Подача