Изобретение относится к цифровой вычислительной технике и может быть использовано при построении преобразователей в устройствах сопряжения и обмена информацией.

Целью изобретения является расширение класса решаемых задач за счет обеспечения преобразования кодов произвольной разрядности, а также повышение быстродействия преобразователя.

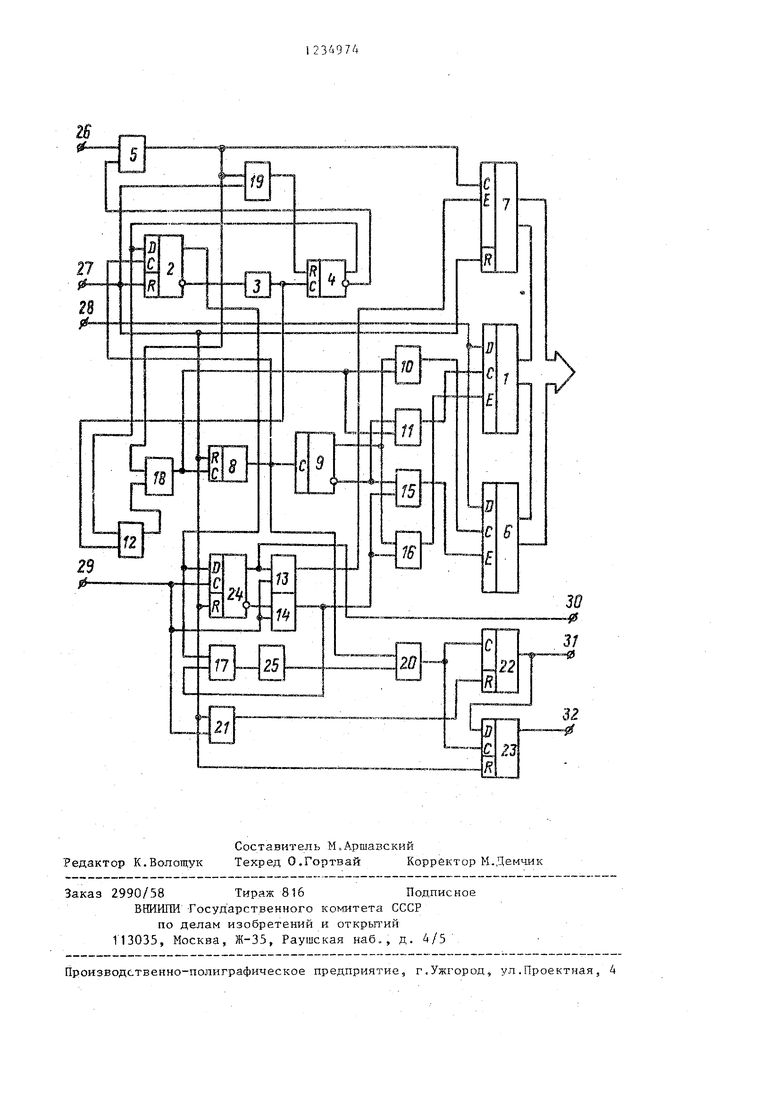

На чертеже приведена блок-схема предлагаемого преобразователя.

Преобразователь последовательного кода в параллельный содержит первый

10

- 15

20

30

35

сдвиговый регистр 1, триггер 2 управ ления, генератор импульсов 3, счетчик 4, элемент И 5, второй сдвиговый регистр 6, счетчик числа разрядов 7, деглитель частоты 8, триггер 9 записи информации, элементы И 10 - 17, элементы ИЛИ 18 - 21, триггер 22 готовности, триггер 23 неисправности, триггер 24 ввода информации, элемент За- Йержки 25, вход синхронизации преобразователя 26, установочный вход пре- образователя 27, информационный вход преобразователя 28, вход съема информации 29, выход конца сообщения 30, выход готовности 31, выход неисправности 32, Выходы одноименных разрядов сдвиговых регистров 1 и 6, а также счетчика числа разрядов 7 объединены и подключены к информационному выходу преобразователя.

Преобразователь работает следующим образом.

Ма установочный вход преобразователя 27 подается запускающий импульс, который обнуляет счетчики 4 и 7, делитель 8, триггеры 2, 22, 23 и 24, подготавливая преобразователь к приему информации. При этом на вход генератора импульсов 3 и вход элемента И 5 поступает потенциал логической :единицы с инверсных выходов триггера управления 2 и счетчика 4 соответственно. .Это обеспечивает запуск генератора 3 и открытие элемента И 5 для приема синхроимпульсов, сопровождаю- .. щих информацию. Поступающие на вход преобразователя 26 синхроимпульсы через- элемент И 5 проходят на вход счетчика числа разрядов, который считает количество бит в информационной последовательности, через элемент ИЛИ 18 на вход делителя частоты 8, коэффициент деления которого равен разрядности первого и второго

12349742

щвиговьгх регистров 1 п 6, а также la входы элементов И 10 или 11. В за- зисимости от состояния счетного триггера записи 9 синхроимпульсы с выхода элементов И 10 или 11 поступают на вход синхронизации первого или второго сдвигового регистра. Инфор- матдионные входы сдвиговых регистров 1 и 6 обьединены, но информация записывается в один из регистров. Как только на выходе делителя частоты 8 появляется импульс переноса, по заднему фронту которого переключается счетный триггер записи информации 9 и устанавливается триггер готовности 22, делитель частоты 8 обнуляется и начинает новый цикл счета, а информация будет записываться в другой сдвиговый регистр. Сигнал логической единицы с триггера готовности 22 поступает на выход преобразователя 31, сообщая потребителю о готовности преобразователя к вьвдаче параллельного кода.

Потребитель, получив сигнал готовности, подает на вход преобразователя 29 импульс информации, кото- рьш обнуляет триггер гото.вности 22 и поступает через элемент И 14 и один из элементов И 15 или 16 в за- . висимости от состояния триггера записи информации 9 на вход управления выходными ключами заполненного сдвигового регистра. При этом информация, которая запоминается в сдвиговом ре гистре, выдается на информационный выход преобразователя. Когда заполнится другой сдвиговый регистр, по заднему фронту импульса переноса делителя частоты 8 вновь устанавливается триггер готовности 22, вьфабаты- ваю111 1й готовность преобразователя к выдаче параллельного кода, и переключается счетный триггер ин- формацк и 9, который управляет поочередной записью информации в сдвиговые регистры 1 и 6. Потребит€;ль, получив сигнал о готовности, посылает на преобразователя 29 импульс 1звода информации, по которому обнуляется триггер готовности 22 и информация со второго заполненного сдвигового регистра выдается на информада- онный выход преобразователя.

40

45

50

55

Информация, поступающая на вход преобразователя,, поочередно записывается в сдвиговые регистры 1 и 6, после чего считы)зается потребителем

Информация, поступающая на вход преобразователя,, поочередно записывается в сдвиговые регистры 1 и 6, после чего считы)зается потребителем

по сигнапу готовности преобразователя Циклы записи и считывания продолжаются до прекращения входных импульсов, коней поступления которых определяет счетчик 4. На вход счетчика 4 поступают импульсы с выхода генератора 3, а с выхода элемента И 5 через элемент ИЛИ 19 на вход начальной установки счетчика 4 поступают входные синхроимпульсы преобразователя. По прекращению входных синхроимпульсов счетчик 4, отсчитав определенное чис- п6 периодов импульсо.в генератора 3, выдает управляющий сигнал логической единицы на триггер управления 2 и элемент И 12, через который импульсы генератора 3, поступающие на второй вход элемента И 12, пройдя через элемент ИЛИ t8, поступают на вход делителя частоты 8 и через один из элемен- тов И 10 или 11 на вход синхронизации соответствующего сдвигового регистра, а с инверсного выхода счетчика 4 на вход первого элемента И 5 поступает сигнал логического нуля, за крывающий элемент И 5 для приема синхроимпульсов. Выходной сигнал со счетчика 4 должен выдаваться через время, превышающее период следования синхроимпульсов, а количество отсчитываемых счетчиком 4 периодов импульсов генератора 3 должно превышать коэффициент деления делителя частоты 8. По заднему фронту импульса переноса делителя частоты 8 переключается триггер записи 9, устанавливается триггер готовности 22 и переключается триггер управления 2, так как на управляющем его входе присутствует сигнал логической единицы, поступающий со счетчика 4. При этом выключается гене ратор 3 импульсов, а конец информационной Последовательности дополняется нулями до полного слова, запоминаемый сдвиговым регистром, причем старшие разряды конца информационной последовательности окажутся в старших оазрядах сдвигового регистра.

Получив сигнал готовности, потребитель подает на вход преобразователя 29 импульс ввода, по которому последнее слово сообщения вьщается на выходную информационную шину. При этом сбрасывается триггер готовности 22, а по заднему фронту импульса 5 .ввода переключается триггер ввода информации 24, так как на его управляющем входе присутствует сигнал ло

5 10)5 2025 д

О 5

0

гической единицы, поступаюпи-П г. триггера управления 2. Сигнал с В1)1ходл триггера ввода информации 24 поступает на выход преобразователя 30, по которому потребителю сообщается о конце массива информации. Тот же импульс ввода с выхода элемента И 14 проходит через элемент И 17, так как на управляющем его входе присутствует сигнал логической единицы, поступающий с триггера управления 2, элемент задержки 25, элемент ШШ 20 и вновь устанавливает триггер готовности 22. Потребитель, получив сигнал готов- ности, вьщает на вход преобразо.рате- ля 29 импульс ввода информации, который сбрасывает триггер готовности 22, проходит через элемент И 13, так как на его упра.вляющем входе присутствует сигнал логической единицы, поступающий с триггера ввода информации 24. С выхода элемента И 13 импульс ввода, информации поступает на вход управления выходными ключами счетчика числа разрядов 7, при этом информация со счетчика вьщается на информа1Д1он- ные выходы преобразователя. Содержимое счетчика бит информации 7 указа- зывает потребителю на значащие разряды последнего принятого слова. Таким образом, сигнал на выходе преобразователя 30 указывает потребителю, что следующая информация будет поступать о количестве значащих разрядов в последнем слове.

Для приема следующей информа1щон- ной посылки необходимо подать на установочный вход преобразователя 27 импульс запуска, при этом преобразователь переходит в исходное состояние, которое позволяет принимать следующее информационное сообщение. Если потребитель, получив сигнал готовности, не подаст сигнал ввода за время записи очередного слова, на управляющий вход триггера неисправности 23 поступает сигнал логической единицы с триггера готовности 22, а после записи очередного слова сигнал с выхода делителя частоты 8, пройдя чере; элемент ИЛИ 20, поступает на вход синхронизации триггера неисправности 23, которьш установится по его заднему фронту, сообщая потребителю о нарушении порядка обмена с преобра- зователем. Если при запуске преобразователя информация и сопровождагопще ее синхроимпульсы не поступают на

входы преобразователя 26 и 28, счетчик 4, отсчитав определенное количество импульсов генератора 3, закры- нает элемент И 5 и подает сигнал ло - гпческой единицы на входы элемента И 12 и триггера управления 2 после чего импульсы генератора 3 проходят с выхода элемента И 12 и через элемент IIJDi 18 на входы элементов 10 и 11 н ка вход делителя частоты 8. При этом с вьсхода элемента И Ю или 11 в зависимости от состояния тригтера записи 9 на вход синхронизации первого 1 или второго 6 сдвигово го регистра поступают импульсы генератора 3, по KOTopbtM в соответствующий сдвиговый регистр запишется нулевая информация. По окончании записи делителем частоты 8 вырабатывается импульс переноса, который задним фрон- том устанавливает триггер управления 2 и триггер готовности 22, При этом выключается генератор 3 , а на выходе преобразователя 31 устанавли- вается потенциал логической единицы, готовности преобразовател к выдаче информации. Потребитель, получив, сигнал готовности 3 подает на вход преобразователя 29 сигнал ввода инфор ;а- ции, по которому производится считы- . ванне нулевой информа1№1и со сдвигового регистра, сбрасывается триггер готовности 22, устанавливается триггер ввода информации 24, так как на управляю1Щ-1Й вход триггера ввода 24 поступает сигнал логической единицы с триггера управления 2. Пр и -этом на вьпсоде преобразователя 30 появляется сигнал логической единицы, который сообщает потребителю о конце информации и о том, что вслед, за этим по- . следует информация о количестве значащих разрядов в последнем слове. То же импульс ввода информации проходит fc вихода элемента И 14 через эл-:-- мент И 17, так как на управляющем входе элемента И 17 присутствует потенциал логической единицы, поступаю щий с триггера управления 2, элемент задержки 25, элемент ИЛИ 20 и вновь устанавливает триггер готовности 22. Получив сигнал готовности, потребитель посылает на вход преобразовате-- ля 29 импульс ввода информации J кото рый проходит через элемент И 13, так ак триггер ввода информации установлен в единицу предыдупшм импульсом ВВОДА информации, и поступает на

вход управления выходными ключами счетчика 7. При этом на информацион- ньй выход преобразователя выдается нулевая информадая со счетчика 7, что указывает на отсутствие значащих разрядов в предыдущем слове.

Изобретение по сравнению с преобразователем 2 отличается более высокой скоростью преобразования непрерывной кодовой последовательности в п-разрядньш параллельный код, так как при использовании двух сдвиговых регистров импульс ввода информации можно подавать после получения сигнала готовности через время п-Т, где п - разрядность сдвиговых регистров S Т - период следования синхроимпульсов, что повышает в п раз ско- .рость преобразования информации.

Предлагаемое устройство позволяет преобразовывать последовательный код любой разрядности в параллелькьт .коДр что повышает универсальность преобразователя. Введение триггера готовности обеспечивает асинхронную передачу параллельного кода потребителю. Введение триггера аварии повышает достоверность преобразования информации.

Формула изобретения

Преобразователь последовательного кода в параллельный, содержащий пер- вьй сдвиговый регис гч.., триггер управления, генератор импульсов, первый элемен.т И, первый вход которого соединен с входом синхронизаи {и преобразователя, информационный вход которого соединен с информационным входом первого сдвигового регистра, а З становочный вход преобразователя соединен с нулевьм входом триггера управления, инверсный выход которого соединен с входом генератора импульсов, выход которого соединен с син- хровходом счетчика, отличающий с я тем, что, с целью расширения класса решаемых задач за счет обеспечения возможности преобразования кодов произвольной разрядности и ловытения быстродействия, в него введены второй сдвиговьй регистр, счетчик числа разрядов, делитель частоты, триггер записи информации, девять элементов И, четыре элемента ИДИ, элемент задержки, триггер готовности, триггер неисправности, триггер ввода информации, выходы триггеров являются соответственно выходом готовности, выходом неисправ- кости и выходом ввода информации преобразователя, информационные выходы которого соединены с выходами второго сдвигового регистра и выходам счетчика числа разрядов, вход син- хронизагщи которого соединен с выходом первого элемента И и первыми входами первого и второго элементов ИЛИ, вторые входы которых соединены соответственно с установочным входом преобразователя и выходом второго элемента И, первый вход которого соединен с прямым выходом счетчика и информационным входом триггера управления, прямой выход которого соединен с информационным входом триггера ввода информации и перзым входом третьего элемента И, выход которого через элемент задержки соединен с первым входом третьего элемента ИЛИ, выход которого соединен с синхровхо- дами триггера готовности и триггера неисправности, нулевой вход которого соединен с установочным входом преобразователя, входами сброса делителя частоты и триггера ввода информации и с первым входом четвертого элемента ИЛИ, второй вход которого соединен с входом съема информации преобразователя, с синхровходом триггера ввода информации и первыми входами четвертого и пятого элементов И, вторые входы которых соединены соответственно с прямым и инверсным выходами

триггера ввода информа(у1и, выходы четвертого и пятого элементов И соединены соответственно с нходом разрешения зьвдачи счетчика числа разрядов и первыми входами шестого и седьмого элементов И, выходы которых соединены соответственно с входами разреше- выдачи первого и второго сдвиговых регистров, синхровходы которых соединены соответственно с выходами восьмого и девятого элементов И, первые входы которых соединены с выходом второго элемента ИЛИ и с синхровходом делителя частоты, выход которого соединен с синхровходом триггера управления, вторым входом третьего элемента ИЛИ и синхровходом триггера записи информации, прямой выход которого соединен с вторыми входами шестого и девятого элементов И, а инверсный выход триггера записи информации соединен с вторыми входами седьмого и восьмого элементов И, выход первого элемента ИЛИ соединен с нулевым входом счетчика, инверсный вход которого соединен с вторым входом первого элемента И, выход генератора импульсов соединен с вторым входом второго элемента И, выход чету вертого элемента ИЛИ соединен с нулевым входом триггера готовности, выход которого соединен с информационным входом триггера неисправности, информационный вход второго сдвигового регистра соединен г, информационным входом преобразовагеля, выход пятого .элемента И соединен с вторым входом третьего элемента И.

Редактор К.Вояощук

Составитель М.Аршавский

Техред О.ГортвайКорректор М.Демчик

Заказ 2990/58Тираж 816Подписное

ВНИИПИ -Государственного ко1читета СССР

по делам изобретений и открьггий 113035, Москва, Ж-35, Раушская наб„, д. 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, А

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

| Устройство для ввода информации от двухпозиционных датчиков | 1985 |

|

SU1280640A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| УСТРОЙСТВО ДЛЯ СИГНАЛИЗАЦИИ СРАБАТЫВАНИЯ БЛОКОВ ЗАЩИТЫ ЭЛЕКТРОПИТАНИЯ | 1992 |

|

RU2093941C1 |

| Устройство для ввода информации | 1990 |

|

SU1786491A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2002 |

|

RU2220440C1 |

| Преобразователь кодов | 1985 |

|

SU1311034A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Преобразователь активной мощностиВ КОличЕСТВО иМпульСОВ | 1979 |

|

SU845109A1 |

Изобретение относится к области цифровой вычислительной техники и может использоваться при построении параллельно-последовательньк преобразователей и устройстве сопряжения. Целью изобретения является расширение класса решаемых задач за счет обеспечения преобразования кодов произвольной разрядности, а также пови-- шение бьютродействия преобразователя. Преобразователь содержит два сдвиговых регистра, счетчик числа разрядов, распределитель импульсов, делитель частоты, генератор импульсов, пять триггеров, элементы И, ИЛИ, элемент задержки. Преобразователь обеспечивает прием и преобразование кодов произвольной разрядности и сокращение времени преобразования за счет попеременного приема в первый и второй сдвиговые регистры. Кроме того, преобразователь дает возможность орга- 11изации асинхронной выдачи полученной информации потребителю. 1 ил. 2 tC сл ю оо со «vi 4;ib

| Преобразователь последовательного кода в параллельной | 1976 |

|

SU628485A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Преобразователь последовательного кода в параллельный | 1979 |

|

SU783789A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-05-30—Публикация

1984-05-07—Подача