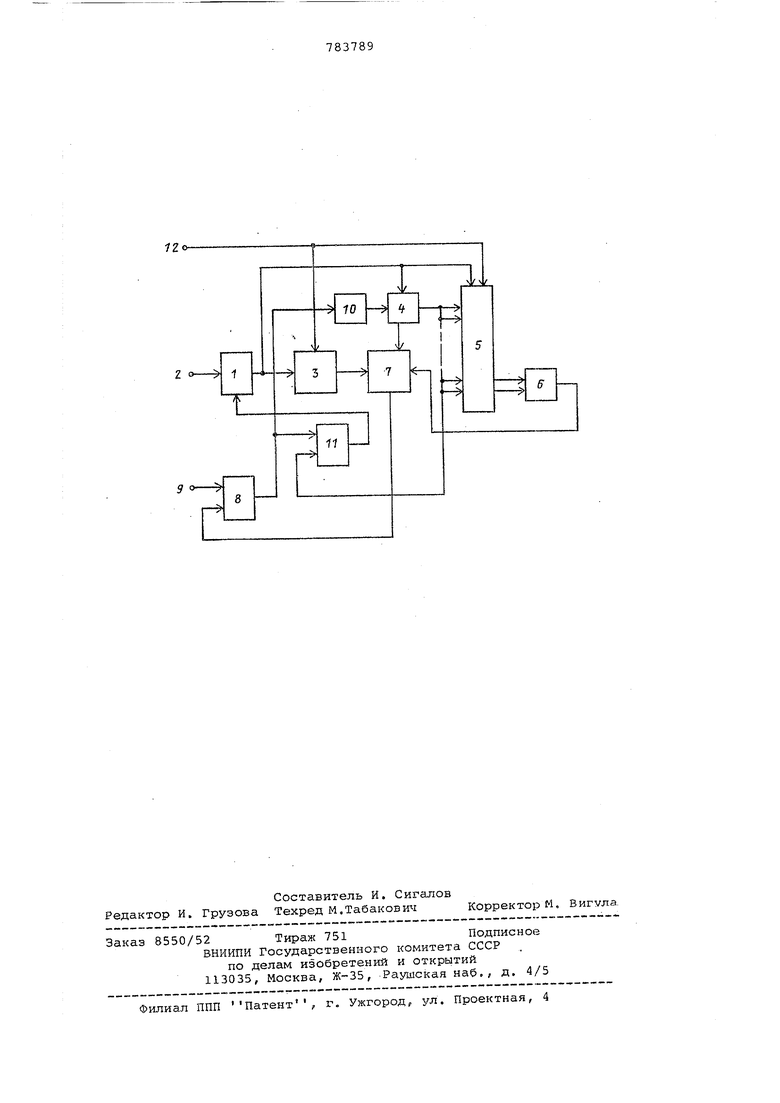

Изобретение относится к вычисли-тельной технике и может быть использовано для преобразования последовательного двоичного кода в параллельный . В вычислительных машинах, а также в системах и комплексах часто возникает необходимость передачи информации между блоками к системам. Более экономичной является передача инфориации в последовательном коде, так как для этого требуется гораздо мень lue оборудования, чем при передаче ин формации в параллельном коде. Но пос кольку , с целью повышения ,быстродейс ВИЯ, обработку информации в вычислительных устройствах ведут в параллельном коде, то для связи передающих и обрабатывающих устройств разработаны преобразователи последовательного кода в параллельный. В .частности, известен преобразователь последовательного двоичного кода в параллельный двоично-десятичный, содержащий счетчик двоичных раз рядов последовательного кода, старшие два разряда которого соединены с одним из входов дешифратора, генератор тактовых импульсов, выход КОТО РОГО соединен со входами .счетчика не совЕЛХ эквивалентов, и выходной регистр, в который, с целью повышения надежности, введены схема сравнения, счетчик повторения, блок запрещения тактового импульса младшего разряда и блок выделения младшего разряда последовательного кодарД . Это устройство отличается узкими функциональными возможностями, и в нем отсутствует контроль достоверности принимаемой информации. Наиболее близким по технической сущности к заявляемому преобразователю является преобразователь последовательного двоичного кода, в параллельный, содержащий сдвиговый регистр, принимающий последовательно передаваемые шестиразрядные слова. Прием длится до тех пор, пока слово полностью не загрузится в сдвиговый регистр. В преобразователе имеется также схема синхронизирующих импульсов, с помощью которых осуществляются в сдвиговом регистре сдвиги информации. Как только сдвиговый регистр заполнится всеми шестью разрядами слова, схема синхронизирующих импульсов выдает импульс в буферную 1память для приема информации в параллельной форме 23. Схема данного преобразователя обеспечивает преобразование последовательного потока информации в блоки параллельной выходной информации. Поток последовательной входной информации имеет большое количество знаков, каждый из которых содержит N бит цифровой информации, которой предшествует начальный бит, представ ленный одним уровнем напряжения и за которым следует по крайней мере один бит остановки, представленный другим уровнем напряжения. Преобразователь содержит сдвиговый -регистр со входным захшмом синхронизации и входным информационным зажимом, на который подается поток последователь ной входной информации. Регистр имеет N+X каскадов, где X соответствует числу начальныхи конечных битов У каждого каскада регистра есть соответствующий входной зажим. При помощи установочного входа N+X каскадов сдвигового регистра сбрасываю ся в начальное состояние. Кроме того, имеется схема обнаружения начал ных бит слова, выполненная в виде ищущего мультивибратора, управляе iый генератор и триггер управления, вход которого соединен с установочным входом преобразователя, а вЫход с управляемым генератором. К недостаткам такого преобразова теля относятся отсутствие контроля достоверности принимаемой информации, жесткая привязка к началу слова принимаемой информации, что може привести к выдаче потребителю ложной информации при наличии случайного сбоя в поступающей информации. Цель изобретения - повышение дос товерности приема информации. Для достижения поставленной цели в преобразователь последовательного кода в параллельный, содержащий сдв говый регистр, триггер управления, дешифратор, управляемый генератор, npi-гчем информационный вход преобразователя соединен с информационным входом сдвигового регистра, выходы которого подключены к входу дешифратора, установочный вход преобразо вателя соединен с нулевым входом тр гера управления, выход которого свя зан со входЬм управляемого генерато ра, введены первый и второй элементы И, блок контроля по нечетности, триггер включения и счетчик. Причем синхронизационный- вход преобразователя соединен с первым входом перво го элемента И, выход которого под лючен к синхронизационным входам блока контроля по нечетности, счетчика и сдвигового регистра. Вькод управляемого .генератора соединен со вторым синхронизационным входом счет чика, первый выход которого связан с .установочным входом сдвигового, регистра и с единичным входом триггера включения, выход триггера управления - с нулевым входом триггера. включения, выход которого соединен со вторым входом первого элемента И. Информационный вход преобразователя соединен с информационным входом блока контроля по нечетности, выход которого связан с первым входом второго элемента И, выход которого соединен со счетным входом триггера управления. Второй выход счетчика подключен к второму входу второго элемента И, третий вход которого соединен с выходом дешифратора. Схема преобразователя последовательного кода в параллельный изображена на чертеже. Она содержит первый элемент И 1, первый вход которого соединен со входом 2 синхронизации преобразователя, а выход - с синхронизационным входом блока 3 контроля по нечетности, входом счетчика 4 и входом синхронизации сдвигового регистра 5. Выходы первых двух младших разрядов регистра 5 соединены со входом дешифратора 6, выполняющего функцию обнаружения начальных бит слова, выход которого подключен к третьему входу второго элемента И 7. Выход элемента И 7 соединен со счетным входом триггера 8 управления, вход установки нуля которого соединен с установочным входом 9 преобразователя. Выход триггера 8 управления связан со входом управляемого генератора 10 и входом установки нуля триггера 11 включения. Информационный вход 12 последовательного ввода данных преобразователя соединен с информационным входом блока 3 контроля нечетности и информационным входом сдвигоз ого регистра 5. Преобразователь работает следующим образом. Запуск преобразователя осуществляется импульсом, подаваемым на вход 9. Этим импульсом на выходе триггера 8 управления устанавливается логический О, запускающий управляемый генератор 10. Управляемый.генератор 10 формирует импульсы. С етчик 4 припоступлении определенного числа ш 1пульсов управляемого генератора 10 формирует импульс, поступающий на входы установки нуля сдв-игового регистра 5, и устанавливает на его выходах логический же импульс на выходе триггера 11 включения устанавливает логическую , разрешающую прохожд.ение импульсов синхронизации со входа 2 преобразователя на вь.ход первого элемента И 1, По импульсам синхронизации, каждьй из которых соответствует определенному разряду последователвио передаваемого слова, осуществляется ввод слова младшими разрядами вперед в сдвиговый регистр 5 и выполИяется контроль принимаемого.слова блоком 3 контроля нечетности. Как только начальные биты преобразуемого слова установятся в соответству1ш-,их для них разрядах сдвигового регистра 5, дешифратор 6 обнаружения начальных бит слова выдаст на один из входов второго элемента И 7 логическую 1 , При этом на другой вход второго элемента И 7 с выхода блока 3 контроля нечетности поступит также логическая , если преобразуемое слово не было искажено при передаче. Счетчик 4 определяет отсутствие импульсов синхронизации на входе 2 синхронизации, так как конечные биты преобразуемого слова не сспровождаются импульсами синхронизации, и формирует импульс, поступающий на третий вход второго элемента И 7. С выхода элемента И 7 этот импульс подается на счетный вход триггера 8 управления и устанавливает на его выходе логическую ,. которая устанавливает на выходе триггера 11 включения логический о, запрещакхций прохождение импульсов синхронизации через первьй элемент И 1, и выключает упpaвляe ий генератор 10.

По окончании указанного процесса преобразования на выходах сдвигового регистра 5 будет нахо1;иться параллельный код преобразованного слова.

В случае обнаружения блоком 3 ошибки Б преобразуемом слове второй элемент И 7 будет закрыт (логическим с выхода блока 3 контроля нечетности) для прохождения импульса со счетчика 4. Последний, обнаружив конечные биты преобразуемого слва, выдает импульс на входы установки нуля сдвигового регистра 5 для его исходной установки, тем самым подготовив преобразователь к повторному преобразованию.

ПрИ запуске преобразователя асинхронно с поступающим на его вход словом, т.е. импульс запуска на входе 9 появляется в момент времени, когда уже часть слова была передана в нем выполняется процесс, аналогичный случаю обнаружения ошибки в преобразуемом слове, с той лишь разницей, второй элемент И 7 закрыт логическим по крайней мере от дешифратора.

Изобретение отличается высокой достоверностью принимаемой информа1 И.

Введение двух элементов И, блока контроля нечетности, триггера включения и счетчика позволило намного повысить достоверность принимаемой информации и обеспечить асинхронную

работу преобразователя по отнсялению к источнику последовательно передаваемого слова.

Высокая достоверность принимаемого слова обеспечивается блоком контроля нечетности, так как в передаваемом слове кроме начальных, конечных и информационных бит есть по крайней мере один контрольный бит, который совместно с информационными битами анализируется блоком контропя нечетности.

Формула изобретения

Преобразователь последовательного кода в параллельный, содержащий сдвиговый регистр, триггер управления, дешифратор, управляемый генератор, причем информационный вход преобразователя соединен с информационным входом сдвигового регистра, выходы которого соединены со входом дешифратора, установочный вход преобразователя соединен с нулевым входом триггера управления, выход которого соединен со входом управляемого генератора, отличающийся тем, что, с целью повышения достоверности, в него введены первый и второй элементы И, блок контроля по

нечетности, триггер включения и счетчик, причем синхронизационный вход преобразователя соединен с первым входом первого элемента И, выход которого соединен с синхронизационными входами блока контроля по нечетности, счетчика и сдвигового регистра, выход управляемого генератора соединен со вторым синхронизационным входом счетчика, первый выход которого соединен с установочным входом сдвигового регистра и с единичным входом триггера включения, выход триггера управления соединен с нулевым входом триггера включения, выход которого соединен со вторым входом

первого элемента И, информационный вход преобразователя соединен с информационным входом блока контроля по нечетности, выход которого соединен с первым входом второго элемента И, выход которого соединен со счетным входом триггера управления, второй выход счетчика соединен со вторым входом второго элемента И, трютий вход которого соединен с выходом дешифратора.

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР 562814, кл. G 06 F 5/04, 20.05.75. 2. Патент США 3946379,

кл. 340-347, опублик. 1976 (прототип).

7Zo

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь последовательного биполярного кода в параллельный униполярный код | 1989 |

|

SU1695511A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| Преобразователь последовательного кода в параллельный | 1984 |

|

SU1229968A1 |

| Преобразователь последовательного кода в параллельный | 1985 |

|

SU1290537A1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЯ | 1992 |

|

RU2045781C1 |

| УСТРОЙСТВО ДЛЯ СЧИТЫВАНИЯ ИЗОБРАЖЕНИЙ ПО БАЗОВОМУ ИНТЕГРАЛЬНОМУ МЕТОДУ (БИМ) | 1996 |

|

RU2162247C2 |

| Устройство для контроля аналоговых объектов | 1985 |

|

SU1288702A1 |

| Устройство для контроля временных диаграмм логических блоков | 1979 |

|

SU788111A1 |

| Преобразователь последовательного кода в параллельный | 1984 |

|

SU1231613A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1989 |

|

SU1667259A1 |

Авторы

Даты

1980-11-30—Публикация

1979-01-03—Подача