Изобретение относится к области вычислительной техники, предназначено для выполнения в режиме разделения во времени операции многоканального приема и преобразования самосинхронизирующихся последовательных двоичных кодов от каналов с одинаковыми или различными длинами кодов и битовыми скоростями с выдачей информации фрагментами (слогами) параллельно-последовательного кода в сопровождении сигналов синхронизации фрагмента, информационной ошибки при четном числе единиц в принятом коде, сбоя битовой синхронизации при длине принятого кода, не кратной длине фрагмента, готовности фрагмента и готовности результата и может быть использовано при построении устройств для ввода информации типа [1] и контроллеров локальной сети (КЛС) с радиальной топологией [2, с.64-69] с раздельными и/или мультиплексными линиями (каналами) связи (ЛС), например КЛС станции локальной сети (СЛС) по протоколам на основе ГОСТ 18977-79 и РТМ 1495-75, имеющих широкое применение в системах управления авиационной, судовой и прочей техники, расположенной, как правило, на подвижных объектах [2, с.57-64].

В составе СЛС можно выделить (см., например, в [2] на с.221 рис.5.9) ядро (содержит процессор или однокристальную электронную вычислительную машину (ЭВМ), схему синхронизации и начальной установки и комбинированную память (в общем случае содержит ОЗУ - оперативное запоминающее устройство, ДОЗУ - двухпортовое ОЗУ, ПЗУ - постоянное запоминающее устройство и РПЗУ - репрограммируемое ПЗУ)), КЛС (содержит устройство для ввода информации, устройство для вывода информации и устройство для управления обменом (УУО) и синхронизацией (блок связи с подсистемой) для взаимосинхронизации и управления КЛС в целом), функционально ориентированные устройства для ввода-вывода информации в процессе взаимодействия СЛС с внешними объектами (пультом оператора, смежными системами, исполнительными устройствами, датчиками событий в объектах управления и т.п.), блок питания и системную магистраль (Q-BUS, ISA, VME либо другую) для обмена информацией между составными частями СЛС под управлением ЭВМ.

Следует отметить, что существует значительное число самосинхронизирующихся кодов, которые могут быть использованы при построении разнообразных устройств для ввода информации (биимпульсный код, манчестерский код, потенциальный код 2В 1Q, избыточные коды типа 4В/5В и т.п., [3]), но в локальных сетях наиболее часто используют [4, с. 30] код RZ (ГОСТ 18977-79 и РТМ 1495-75, зарубежные стандарты ARING-429 и AR-ING-575) и манчестерский код (ГОСТ 26765.52-87, зарубежные стандарты MIL-STD-1533B и MIL-STD-1773). В этой связи все дальнейшее изложение ведется с ориентацией на код RZ, так как он пока наиболее широко используется при построении систем управления бортовой аппаратуры. Заметим также, что наибольшую помехоустойчивость обмена информацией по проводным ЛС в любой аппаратуре обеспечивает передача самосинхронизирующегося кода цифровым дифференциальным (разностным) сигналом [5, с.22-24: Линии передачи сигналов.].

Для рационального распределения функций между аппаратно-программными средствами устройство для ввода информации и устройство для вывода информации должны гибко управляться от ЭВМ и быть максимально инвариантными как к протоколам локальной сети, так и к типу системной магистрали.

В бортовой аппаратуре обмен информацией в коде RZ между СЛС, датчиками и потребителями данных производится по мультиплексной ЛС и/или раздельным ЛС самосинхронизирующимися последовательными двоичными кодами (словами) в битовом ряде длин

{n}={16 бит, 24 бит, 32 бит}, (1)

младшими разрядами вперед и старшим разрядом контроля количества единиц в младших разрядах, разделенных между собою паузами Тп длительностью

Тп=(4-40)•Т, (2)

определяемой периодом T= 1/F частоты следования F импульсов битовой синхронизации передачи сообщения, принадлежащей в общем случае множеству

{F}={12,5 кГц, 48 кГц, 100 кГц, 250 кГц, 500 кГц, 1000 кГц}. (3)

Согласно РТМ 1495-75 в бортовой аппаратуре обмен информацией может осуществляться следующими тремя способами:

- асинхронным, являющимся основным. В этом режиме датчик непрерывно циклически выдает в отдельную ЛС от одного до 16 кодов (слов) информации;

- по запросу, при котором датчик выдает в отдельную или мультиплексную ЛС требуемое количество слов информации только при получении по отдельной линии сигнала PQ запроса от потребителя - см. в [2] рис.1.26,б;

- по готовности, при котором датчик по отдельной линии выставляет всем потребителям сигнал RDY готовности о начинающейся передаче (см. в [2] рис. 1.26, в), а затем выдает в отдельную или мультиплексную ЛС требуемое количество слов информации, причем сигнал RDY должен выставляться раньше передачи и сниматься не раньше ее окончания.

В любом из способов от любого датчика j-го канала ввода информация передается по ЛС в коде RZ цифровым дифференциальным сигналом

Uj=Uaj-Ubj (4)

в сложной помеховой обстановке при значительных величинах синфазной помехи

Ucj=(Uaj+Ubj)/2. (5)

Наличие в ЛС помехи Ucj (5) искажает обе компоненты

Uaj=Ucj+Uj/2, (6)

Ubj=Ucj-Uj/2, (7)

дифференциального сигнала Uj (4) на входах ja и jb устройства (потребителя), которое характеризуется показателем помехоустойчивости

K={M(Ucj/Uj)}max, (8)

где j= 0, 1,..., А - номер датчика (канала ввода устройства), изменяющийся от 0 до А включительно;

Uaj и Ubj - соответственно первая (а) и вторая (b) компоненты сигнала Uj (4), измеряемые на входах aj и bj устройства относительно его общей шины (корпуса);

/ - здесь и далее знак арифметической операции деления;

М(Х) - оператор выделения модуля величины X, заключенной в круглые скобки, т.е. в (8) величины X=Ucj/Uj;

{Q}max - оператор выделения максимального значения величины Q, содержащейся в фигурных скобках, т.е. в (8) величины Q=M(Ucj/Uj).

Согласно ГОСТ 18977-79 (см., например, [2, с.57-63]) в коде RZ каждый бит информации передается дифференциальным сигналом Uj (4) в течение битового периода Т=Т1 + Т2 при Т1=Т2=Т/2 так, что в активной части Т1 периода битовой синхронизации в течение времени Т2 возврата к нулю и в течение паузы Тп (2) величина напряжения Uj на входах устройства (приемника) полностью описывается выражениями

Uj=(10±3) В в течение Т1 при приеме "1" кода RZ, (9)

Uj=-(10±3) В в течение Т1 при приеме "0" кода RZ, (10)

Uj=±1 В в течение Тп (2) или времени Т2 возврата к нулю. (11)

В реальных условиях передача информации в бортовой аппаратуре происходит в сложной помеховой обстановке при синфазной помехе Ucj (5), могущей превышать полезный сигнал Uj (4) в несколько раз. Это обусловило создание, в частности, специализированной микросборки АП.004 Т53.530.006 ТУ для приема и декодирования "Кода последовательного 48 кГц" по двум каналам при уровне синфазной помехи { M(Ucj)}max=15 В, т.е. при реальном показателе помехоустойчивости

Кр=15/7>2. (12)

В устройствах для ввода информации типа [1] при обмене по основному асинхроному способу каждой операции приема и преобразования сообщения должна предшествовать операция обнаружения паузы Тп (2) для подготовки устройства к выполнению очередной операции, а окончательный результат выполнения каждой операции приема и преобразования при любом способе обмена следует контролировать, например формировать сигнал информационной ошибки при четном числе единиц в принятом коде и сигнал сбоя битовой синхронизации при отклонении разрядности входного кода от выбранного ряда длин типа (1).

В этой связи создание для бортовой аппаратуры простого устройства для ввода информации по любому способу обмена от множества датчиков с разными параметрами, определенными, например, множествами типа (1) и (3) при условиях (3), (12) и гибкой управляемости от ЭВМ через УУО при максимальной независимости от протоколов локальной сети и типа системной магистрали, представляет, на наш взгляд, актуальную техническую задачу, разрешение которой позволит повысить качество разрабатываемых КЛС, в том числе и устройств типа [1] , поддерживающих в локальной сети при минимальных аппаратурных затратах высокую достоверность функционирования при обмене самосинхронизирующимися последовательными двоичными кодами.

Достоверность функционирования - свойство цифрового устройства, характеризующее способность средств контроля признать выходной результат работы правильным или ошибочным с помощью аппаратно-программных средств контроля [6, с.5], обеспечивающих его контролепригодность. Контролепригодность - свойство устройства, обуславливающее приспособленность контроля его технического состояния в процессе изготовления и эксплуатации [6, с.153]. Именно контролепригодность дает возможность получить на практике необходимую достоверность функционирования систем передачи, обработки информации и управления [7, с.12], которые в современной аппаратуре являются также станциями локальных сетей.

Основным недостатком известных устройств является узкая специализация и ограниченность их функциональных возможностей.

Известно одноканальное устройство для ввода информации [8], содержащее демодулятор, входы цифрового дифференциального сигнала кода RZ, являющиеся информационными входами демодулятора, генератор одиночных импульсов, специализированный счетчик, тактовый вход, соединенный с первыми входами формирователя и счетчика, вторые входы которых соединены с синхронизирующим выходом демодулятора, 33-разрядный регистр сдвига, информационный и синхронизирующий входы которого соединены с информационным выходом демодулятора и выходом формирователя, дешифратор адреса, выходы информационной и управляющей групп, соединенные соответственно с информационной группой выходов регистра сдвига и выходами дешифратора, стробирующий вход которого соединен с выходом младшего разряда регистра сдвига, являющимся выходом готовности результата операции устройства, входы дешифратора соединены с адресной группой выходов регистра сдвига, входы установки которого в режим преобразования и начальное состояние соединены с выходами счетчика.

По сигналам кода RZ и тактовым импульсам устройство [8] принимает информацию асинхронным способом следующим образом.

В течение каждого четвертого периода Т паузы Тп (2) счетчик с помощью тактовых импульсов частоты Fт=16/Т формирует два сигнала, переводящих регистр сдвига в начальное состояние (10...0) режима приема и преобразования. С окончанием паузы начинается режим приема и преобразования длительностью Тр= (32•Т), в течение которого формирователь вырабатывает 32 импульса битовой синхронизации, по каждому из которых в регистр сдвига принимается со сдвигом вправо очередной бит последовательного двоичного кода с выхода демодулятора. После окончания каждой последовательности из 32 импульсов битовой синхронизации регистр сдвига заполняется и выставляет через дешифратор на одном из управляющих выходов адресный сигнал готовности информации, которая снимается с информационной группы выходов регистра сдвига адресуемым получателем. После этого счетчик сбрасывает регистр сдвига в начальное состояние (10... 0), в котором он остается до поступления на него очередной последовательности из 32 импульсов битовой синхронизации.

Основным недостатком устройства [8] является ограниченность области его применения, что обусловлено как ограниченностью его функциональных возможностей (отсутствует возможность ввода входного кода в ряде длин (1) и контроля его функционирования), так и тем, что в современных КЛС функция заключительной передачи вводимой информации получателю принадлежит не устройству ввода, а осуществляется ЭВМ с помощью УУО и функционально ориентированных устройств ввода-вывода.

Известно многоканальное устройство для ввода информации [9], содержащее блоки буферной памяти, счетчик, мультиплексор, дешифратор, регистр сдвига, триггер, генератор импульсов и элементы И. Данное устройство специализировано узко, так как выполняет функцию последовательного переноса содержимого каждого из блоков буферной памяти в регистр сдвига для передачи в ЭВМ.

Из известных технических решений наиболее близким к предлагаемому является устройство для ввода информации [1], содержащее мультиплексор для адресной коммутации соответственно компонент Uaj (6) и Ubj (7) сигнала Uj (4), первый преобразователь уровня, двухканальный программируемый делитель частоты, три регистра сдвига, декодер данных, генератор импульсов, второй преобразователь уровня, пять регистров, счетчик, триггер, элемент И-НЕ, входы первых и вторых компонент цифровых дифференциальных сигналов самосинхронизирующихся кодов, являющиеся информационными входами мультиплексора, кодовый вход данных, соединенный с информационными входами второго, четвертого и пятого регистров, три входа записи информации с кодового входа данных, вход сброса готовности результата, выход готовности результата, кодовый выход ошибки, являющийся выходом третьего регистра, и информационный кодовый выход, являющийся выходом первого регистра.

Функционирование устройства [1] опишем при поступлении на входы aj и bj каждого информационного j-го канала ввода мультиплексора трехуровневого цифрового дифференциального сигнала Uj (4) кода RZ, характеристики которого во времени T1, T2 и Тп определены множеством

{(9), (10), (11)}. (13)

С учетом изложенного выше последовательно рассмотрим функционирование четырех укрупненных частей устройства [1] (регистровой памяти управляющих кодов, коммутатора, декодера и преобразователя последовательного двоичного кода в параллельный код), образованных совокупностями отдельных его составных частей.

Регистровая память управляющих кодов содержит второй, четвертый и пятый регистры для хранения кодов управления соответственно декодером данных, делителем частоты и через второй преобразователь уровней адресным выбором канала j мультиплексора и порогового напряжения детектирования "1" или "0" кода RZ канала j. В каждый из этих регистров информация заносится по отдельному импульсу записи с общего кодового входа данных от ЭВМ.

Коммутатор содержит мультиплексор (образован из двух мультиплексоров-демультиплексоров) для одновременной адресной коммутации обеих компонент Uaj (6) и Ubj (7) сигнала Uj (4), первый преобразователь уровней (образован адресуемым мультиплексором-демультиплексором с ограничительными резисторами и двумя детекторами допусковых зон [10], каждый из которых выполнен на двух компараторах (микросхеме 521СА1 с двумя ограничительными резисторами) с объединенными по ИЛИ выходами, причем выход мультиплексора-демультиплексора соединен с пороговыми входами обоих детекторов допусковых зон, выход приема "1" кода RZ является выходом первого детектора допусковой зоны, инвертирующий вход которого соединен с неинвертирующим входом второго детектора допусковой зоны и с выходом компоненты Ubj мультиплексора, выход компоненты Uaj которого соединен с неинвертирующим входом первого детектора допусковой зоны и инвертирующим входом второго детектора допусковой зоны, выход которого является выходом приема "0" кода RZ, и второй преобразователь уровней для ретрансляции адресации всех мультиплексоров-демультиплексоров от четвертого регистра и формирования группы пороговых напряжений, выходы которой соединены с сигнальными входами мультиплексора-демультиплексора первого преобразователя уровней.

В процессе функционирования устройства [1] для любого выбранного канала j первый детектор допусковой зоны при положительном (или отрицательном) уровне порогового напряжения на выходе мультиплексора первого преобразователя уровней вырабатывает единичный сигнал приема "1" кода RZ при величине Uaj (или Ubj), соответствующей величине (9), а второй детектор допусковой зоны вырабатывает единичный сигнал приема "0" кода RZ при величине Ubj (или Uaj), соответствующей величине (10). Таким образом, в устройстве [1] детектирование кода RZ производится непосредственно по сигналу Uaj (6) или Ubj (7), который содержит помеху Ucj (4). Следовательно, устройство [1] работоспособно только при ограничении

M(Uj/2)>M(Ucj), (14)

т.е. характеризуется показателем помехоустойчивости

Кп={M(Ucj/Uj)}max<0,5, (15)

который в несколько раз меньше по сравнению сo значением (12), требуемым для бортовой аппаратуры.

Декодер содержит двухканальный управляемый делитель частоты (каждый канал делителя выполнен на микросхеме типа 133 ИЕ8, представляющей собой 6-разрядный двоичный умножитель, который может работать как цифровой интегратор с последовательным переносом кода числа из регистра подынтегральной функции), второй и третий регистры сдвига, декодер данных, генератор импульсов и третий регистр. Декодер предназначен для формирования тактовых импульсов на первом выходе делителя частоты, который соединен с тактовыми входами второго и третьего регистров сдвига и первым входом элемента И-НЕ, импульсов битовой синхронизации на втором выходе делителя частоты, который соединен с тактовым входом первого регистра сдвига, счетным входом счетчика и входом записи третьего регистра, последовательного двоичного кода принимаемой информации на битовом выходе декодера данных, который соединен с информационным входом первого регистра сдвига, и кода ошибки, выход которого через третий регистр связан с кодовым выходом декодера данных.

В процессе функционирования устройства [1] работа декодера данных программируется с кодового выхода второго регистра, а каждого двоичного умножителя делителя частоты - с соответствующего 4-разрядного кодового выхода пятого регистра.

Первый (или второй) двоичный умножитель при q=1 (или q=2) по непрерывной последовательности импульсов генератора импульсов и отдельному коду qC(3:0) функционирует циклически с длительностью цикла Тц=16/f (где f - частота следования импульсов генератора тактовых импульсов, которая значительно больше частоты F, определенной множеством (3), например f/F=16) так, что в течение цикла на выходе вырабатывает количество импульсов, определенное числом

Q=qC0+(2•qC1)+(4•qC2)+(8•qC3), (16)

т.е. в течение Тц при qC(3:0)=(0000); (0001);...;(1110); (1111) делитель частоты вырабатывает на тактовом выходе (или на выходе сдвиговых импульсов битовой синхронизации) число импульсов Q=0; 1;...; 14; 15, по которым сигналы приема "1" и "0" кода RZ принимаются соответственно во второй и третий регистры сдвига (или фрагмент последовательного кода принимается в первый регистр сдвига с подсчетом числа принятых битов счетчиком), по содержимому которых и содержимому третьего регистра декодер данных вырабатывает на битовом выходе фрагмент (один или несколько бит) последовательного кода, а на кодовом выходе код ошибки при возникновении неопределенности при анализе содержимого второго и третьего регистров.

Поскольку импульсы битовой синхронизации вырабатываются вторым умножителем при q=2 согласно (16) независимо от сигналов приема "1" и "0" кода RZ, то корректная работа устройства [1] возможна при высокой стабильности генератора импульсов и управлении от ЭВМ и УУО при обмене только по неосновному способу (т.е. по готовности или по запросу) при жесткой взаимосинхронизации датчика по сигналу PQ от ЭВМ или ЭВМ по сигналу RDY от датчика.

Преобразователь последовательного двоичного кода в параллельный код содержит первый сдвиговый регистр, первый регистр, счетчик, триггер, элемент И-НЕ, информационный вход, соединенный с выходом последовательного двоичного кода декодера данных, тактовый вход, соединенный с первым входом элемента И-НЕ и выходом первого двоичного умножителя программируемого делителя частоты, вход импульсов битовой синхронизации, соединенный с тактовым входом первого регистра, счетным входом счетчика и выходом второго двоичного умножителя программируемого делителя частоты, информационный кодовый выход, связанный через первый регистр с кодовым выходом первого регистра сдвига, выход готовности результата операции, соединенный с выходом триггера и вторым входом элемента И-НЕ, и вход сброса готовности результата операции, соединенный с входами сброса первого регистра и триггера, вход установки которого соединен с входом записи первого регистра и выходом переполнения счетчика, вход сброса которого соединен с входом сброса первого регистра сдвига и выходом элемента И-НЕ.

Перед началом очередной операции преобразования преобразователь находится в исходном состоянии (режиме паузы) - первый регистр сдвига, первый регистр, счетчик и триггер сброшены в нулевые состояния. При поступлении последовательная информация передается в первый регистр сдвига по импульсам битовой синхронизации, которые подсчитываются счетчиком битов. При заполнении первого сдвигового регистра счетчик формирует сигнал переполнения, по которому содержимое первого регистра сдвига пересылается в первый регистр и устанавливается триггер, выставляющий сигнал готовности результата операции для передачи содержимого первого регистра в ЭВМ в течение времени готовности Т1г<Тп (2). По сигналу готовности через элемент И-НЕ проходят тактовые импульсы и сбрасывают первый регистр сдвига и счетчик, а ЭВМ считывает содержимое первого регистра и формирует сигнал сброса готовности для продолжения ввода информации от выбранного канала, а при смене канала ЭВМ сначала загружает в четвертый и пятый регистры новую информацию для подготовки ввода информации от требуемого канала, и при формировании сигнала запроса PQ (или при получении сигнала готовности RDY) ЭВМ через УУО формирует сигнал сброса готовности. По сигналу сброса готовности сбрасываются первый регистр и триггер, который запрещает работу элемента И-НЕ, и устройство [1] оказывается готовым к выполнению следующей операции.

Основным недостатком устройства [1] является ограниченность области его применения и аппаратурная сложность при недостаточной помехоустойчивости (из-за низкого показателя помехоустойчивости по оценке (15) и асинхронного формирования импульсов битовой синхронизации вторым двоичным умножителем программируемого делителя частоты по отношению к формированию первым (или вторым) детектором допусковой зоны [10] сигнала приема "1" (или "0") кода RZ) и ограниченности его функциональных возможностей (например, отсутствует возможность ввода входных кодов по основному асинхронному способу в ряде длин), обусловленные тем, что при построении преобразователя [1] в недостаточной степени учтена первичная информация как о способах ввода информации (основном асинхронном и неосновном - по запросу или по готовности), так и о параметрах сигналов вводимой информации, описанных, в частности, множествами (1), (3), (13)), маскируемых помехами Ucj (5) при ограничении (12).

Предлагаемым изобретением решается задача расширения области использования устройства путем повышения его помехоустойчивости (за счет как применения коммутатора с показателем помехоустойчивости (8), удовлетворяющим ограничению (12), так и формирования импульсов битовой синхронизации на основе сигналов приема "1" и "0" кода RZ) и комплексного расширения его функциональных возможностей за счет обеспечения возможности работы устройства для приема информации при любом способе обмена (асинхронном основном или неосновном по запросу или по готовности) в ряде длин кодов типа (1) и ряде битовых скоростей типа (3) с помощью обнаружения паузы с программируемым порогом, а также формирования результирующих сигналов контроля работы устройства - сигнала информационной ошибки и сигнала сбоя битовой синхронизации.

Для достижения этого технического результата в устройство для ввода информации, содержащее коммутатор, регистр, декодер, входы первой и второй компонент цифровых дифференциальных сигналов самосинхронизирующихся последовательных двоичных кодов каналов вводимой информации, являющихся информационными входами коммутатора, кодовый вход данных, связанный через регистр с адресным входом коммутатора, выходы приема "1" и "0" выбранного канала которого соединены с входами декодера, два входа записи, вход сброса готовности результата операции, тактовый вход (эквивалентен генератору импульсов), информационный кодовый выход и выход готовности результата операции, введены два элемента И, обнаружитель паузы, тактовый вход которого соединен с тактовым входом устройства, преобразователь последовательного двоичного кода в параллельно-последовательный код, выход фрагмента параллельно-последовательного кода которого соединен с информационным кодовым выходом, программируемый кодовый вход порога обнаружения паузы, соединенный с кодовым входом обнаружителя паузы, и выходы синхронизации фрагмента параллельно-последовательного кода, информационной ошибки, сбоя битовой синхронизации и готовности фрагмента, соединенные соответственно с первым, вторым, третьим и четвертым выходами преобразователя.

Пятый выход преобразователя соединен с выходом готовности результата операции, первый и второй входы записи устройства соединены соответственно с входами установки в первое и второе состояния паузы обнаружителя паузы и с входами первого элемента И, выход которого соединен с асинхронным инверсным входом записи регистра и первым входом второго элемента И, второй вход которого соединен с входом сброса готовности результата операции устройства, а выход соединен с входом сброса преобразователя, выход последовательного двоичного кода декодера соединен с информационным входом преобразователя, тактовый вход которого соединен с выходом импульсов битовой синхронизации декодера и входом записи обнаружителя паузы, который содержит два входа установки в первое и второе состояния паузы соответственно, кодовый вход, тактовый вход, вход записи, выход потенциального сигнала паузы, выход импульсного сигнала начала паузы, первый элемент НЕ, третий и четвертый элементы И, с первого по четвертый элементы ИЛИ, первый триггер, счетчик и первый элемент И-НЕ, первый вход которого соединен с тактовым входом обнаружителя, кодовый вход которого соединен с информационным параллельным входом счетчика, выходы старших разрядов которого соединены с входами первого элемента ИЛИ, выход которого соединен с первыми входами второго и третьего элементов ИЛИ.

Вход установки в первое состояние паузы обнаружителя соединен с первым входом третьего элемента И асинхронным инверсным входом сброса первого триггера, асинхронный инверсный вход установки которого соединен с входом установки во второе состояние паузы обнаружителя и связан через первый элемент НЕ с асинхронным входом сброса счетчика, вход записи обнаружителя соединен с вторым входом третьего элемента И, выход которого соединен с асинхронным инверсным входом записи счетчика, выход младшего разряда счетчика соединен с вторым входом второго элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И и вторым входом первого элемента И-НЕ, выход которого соединен с вычитающим счетным входом счетчика и вторым входом третьего элемента ИЛИ, выход которого соединен с первым входом четвертого элемента ИЛИ и тактовым входом первого триггера, информационный вход которого соединен с шиной ЛОГИЧЕСКОЙ 1.

Прямой и инверсный выходы первого триггера соединены соответственно с вторыми входами четвертого элемента И и четвертого элемента ИЛИ, выходы которых являются соответственно выходами потенциального сигнала паузы и импульсного сигнала начала паузы, которые соединены соответственно с потенциальным и импульсным управляющими входами преобразователя, который содержит входы информационный, тактовый, потенциальный управляющий, импульсный управляющий, сброса, выход фрагмента параллельно-последовательного кода, пять выходов, второй и третий элементы НЕ, пятый элемент ИЛИ, регистр сдвига с последовательно-параллельным вводом и параллельным выводом, триггеры с второго по пятый, второй, третий и четвертый элементы И-НЕ, пятый элемент И и элемент контроля по модулю два, кодовый вход которого соединен с выходом фрагмента параллельно-последовательного кода, выходы младших разрядов которого соединены с выходами старших разрядов регистра сдвига, а выход старшего разряда фрагмента соединен с информационным последовательным входом регистра сдвига и выходом второго триггера, информационный вход которого является информационным входом преобразователя, тактовый вход которого соединен с входом второго элемента НЕ и тактовыми входами второго триггера и регистра сдвига, информационный параллельный вход которого соединен с входом кода константы, у которого старший бит единица, а остальные биты нули.

Первый выход преобразователя соединен с выходом второго элемента И-НЕ и тактовым входом третьего триггера, выход которого соединен с вторым выходом преобразователя и битовым входом элемента контроля по модулю два, выход которого соединен с информационным входом третьего триггера, выход пятого элемента И соединен с асинхронными инверсными входами установки третьего и четвертого триггеров, третий выход преобразователя соединен с выходом четвертого триггера, асинхронный инверсный вход сброса которого соединен с выходом пятого элемента ИЛИ, первый вход которого соединен с выходом третьего элемента НЕ, асинхронные инверсные входы сброса регистра сдвига и установки второго триггера соединены с потенциальным управляющим входом преобразователя, импульсный управляющий вход которого соединен с вторым входом пятого элемента ИЛИ, первым входом второго элемента И-НЕ и асинхронным инверсным входом установки пятого триггера, асинхронный инверсный вход сброса которого соединен с входом сброса преобразователя и первым входом пятого элемента И, второй вход которого соединен с выходом третьего элемента И-НЕ и тактовым входом пятого триггера, информационный вход которого соединен с шиной ЛОГИЧЕСКОГО 0.

Четвертый выход преобразователя соединен с выходом нулевого младшего разряда и управляющим входом "параллельная запись/сдвиг вправо" регистра сдвига, входом третьего элемента НЕ и первым входом четвертого элемента И-НЕ, выход которого соединен с вторым входом второго элемента И-НЕ, пятый выход преобразователя соединен с выходом пятого триггера и первым входом третьего элемента И-НЕ, выход первого младшего разряда регистра сдвига соединен с вторым входом третьего элемента И-НЕ, третий вход которого соединен с вторым входом четвертого элемента И-НЕ и выходом второго элемента НЕ.

Авторам неизвестны технические решения, содержащие отличительные признаки, эквивалентные отличительным признакам (введение двух элементов И, обнаружителя паузы, преобразователя последовательного двоичного кода в параллельно-последовательный код, программируемого кодового входа порога обнаружения паузы и выходов синхронизации фрагмента параллельно-последовательного кода, информационной ошибки, сбоя битовой синхронизации и готовности фрагмента) предлагаемого устройства, которые по сравнению с прототипом [1] упрощают устройство и расширяют область его использования путем повышения его помехоустойчивости и комплексного расширения его функциональных возможностей за счет как обеспечения ввода информации любым способом (асинхронным, по готовности или по запросу) с различными длинами кодов и битовыми скоростями, например, принадлежащими множествам (1) и (3) соответственно, так и формирования результирующих сигналов контроля работы устройства (информационной ошибки и сбоя битовой синхронизации).

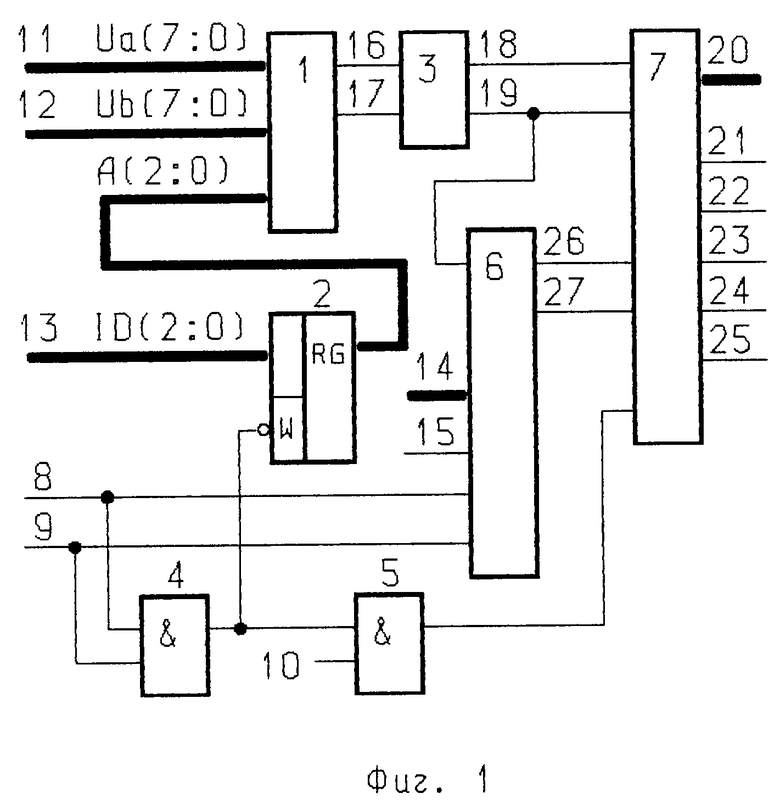

На фиг. 1-3 приведена функциональная схема устройства для ввода информации при реализации его, например, с использованием библиотеки элементов интегральных схем (ИС) серии 533 для работы с последовательными самосинхронизирующимися кодами RZ при ограничении (12) с параметрами, определенными множествами (1), (3) и (13) при длине фрагмента параллельно-последовательного кода, равной байту.

Устройство для ввода информации (фиг.1) содержит коммутатор 1, регистр 2, декодер 3, первый 4 и второй 5 элементы И, обнаружитель 6 паузы, преобразователь 7 последовательного двоичного кода в параллельно-последовательный код, первый 8 и второй 9 входы записи, соединенные соответственно с входами установки в первое и второе состояния паузы обнаружителя 6 и входами элемента 4, выход которого соединен с асинхронным инверсным входом записи регистра 2 и первым входом элемента 5, вход 10 сброса готовности результата, соединенный со вторым входом элемента 5, выход которого соединен с входом сброса преобразователя 7, входы первой 11 и второй 12 компонент цифровых дифференциальных сигналов самосинхронизирующихся последовательных двоичных кодов каналов вводимой информации, являющиеся информационными входами коммутатора 1, кодовый вход 13 данных, связанный через регистр 2 с адресным входом коммутатора 1, программируемый кодовый вход 14 порога обнаружения паузы, соединенный с кодовым входом обнаружителя 6, тактовый вход 15, соединенный с тактовым входом обнаружителя 6, выходы 16 и 17 коммутатора 1, соединенные с информационными входами декодера 3 и являющиеся соответственно выходами приема "1" и "0" самосинхронизирующегося кода канала, выбранного коммутатором 1, выход 18 последовательного двоичного кода декодера 3, соединенный с информационным входом преобразователя 7, выход 19 импульсов битовой синхронизации декодера 3, соединенный с входом записи обнаружителя 6 и тактовым входом преобразователя 7, информационный кодовый выход 20, являющийся выходом фрагмента параллельно-последовательного кода преобразователя 7, выходы синхронизации фрагмента, информационной ошибки, сбоя битовой синхронизации, готовности фрагмента и готовности результата, являющиеся соответственно первым 21, вторым 22, третьим 23, четвертым 24 и пятым 25 выходами преобразователя 7, и выходы 26 и 27 потенциального сигнала паузы и импульсного сигнала начала паузы обнаружителя 6, соединенные соответственно с потенциальным и импульсным управляющими входами преобразователя 7.

Обнаружитель 6 паузы (фиг.2) содержит входы 8 и 9 установки соответственно в первое и второе состояния паузы, кодовый вход 14, тактовый вход 15, вход 19 записи, выход 26 потенциального сигнала паузы, выход 27 импульсного сигнала начала паузы, первый элемент 28 НЕ, третий 29 и четвертый 30 элементы И, элементы ИЛИ с первого 31 по четвертый 34, первый триггер 35, счетчик 36 и первый элемент 37 И-НЕ, первый вход которого соединен с входом 15, вход 8 соединен с первым входом элемента 29 и асинхронным инверсным входом сброса триггера 35, асинхронный инверсный вход установки которого соединен с входом 9, который через элемент 28 связан с входом сброса счетчика 36, вход 19 соединен с вторым входом элемента 29, выход которого соединен с асинхронным инверсным входом записи счетчика 36, выходы старших разрядов которого соединены с входами элемента 31, выход которого соединен с первыми входами элементов 32 и 33, кодовый вход 14 соединен с информационным параллельным входом счетчика 32, выход младшего разряда которого соединен с вторым входом элемента 32, выход которого соединен с первым входом элемента 30 и вторым входом элемента 37, выход которого соединен с вычитающим счетным входом счетчика 36 и вторым входом элемента 33, выход которого соединен с первым входом элемента 34 и тактовым входом триггера 35, информационный вход которого соединен с шиной ЛОГИЧЕСКОЙ 1, прямой и инверсный выходы триггера 35 соединены соответственно со вторыми входами элементов 30 и 34, выходы которых являются выходами 26 и 27 соответственно.

Преобразователь 7 последовательного двоичного кода в параллельно-последовательный код (фиг.3) содержит информационный вход 18, тактовый вход 19, кодовый выход 20, пять выходов с первого 21 по пятый 25, потенциальный 26 и импульсный 27 управляющие входы, вход сброса, второй 38 и третий 39 элементы НЕ, пятый элемент 40 ИЛИ, байтовый регистр 41 сдвига с параллельно-последовательным вводом и параллельным выводом, триггеры с второго 42 по пятый 45, второй 46, третий 47 и четвертый 48 элементы И-НЕ, пятый 49 элемент И и элемент 50 контроля по модулю два, кодовый вход которого соединен с кодовым выходом 20, выходы младших разрядов которого соединены с выходами старших разрядов регистра 41, выход старшего разряда кодового выхода 20 соединен с информационным последовательным входом регистра 41 и выходом триггера 42, информационный вход которого соединен с входом 18, вход 19 соединен с входом элемента 38 и тактовыми входами триггера 42 и регистра 41, вход 26 соединен с асинхронными инверсными входами установки триггера 42 и сброса регистра 41, информационный параллельный вход которого соединен с входом кода константы, у которого старший бит единица, а остальные биты нули.

Выход элемента 46 соединен с тактовым входом триггера 43 и выходом 21, выход 22 соединен с выходом триггера 44 и битовым входом элемента 50, выход которого соединен с информационным входом триггера 43, выход элемента 49 соединен с асинхронными инверсными входами установки триггеров 43 и 44, выход 23 является выходом триггера 44, асинхронный инверсный вход сброса которого соединен с выходом элемента 40, первый вход которого соединен с выходом элемента 39, вход 27 соединен со вторым входом элемента 40, первым входом элемента 46 и асинхронным инверсным входом установки триггера 45, информационный вход которого соединен с шиной ЛОГИЧЕСКОГО 0, вход сброса преобразователя соединен с первым входом элемента 49 и асинхронным инверсным входом сброса триггера 45, тактовый вход которого соединен с вторым входом элемента 49 и выходом элемента 47, выход 24 соединен с входом элемента 39, входом управления "параллельная запись/сдвиг вправо" и выходом нулевого младшего разряда регистра 41 и первым входом элемента 48, выход которого соединен с вторым входом элемента 46, выход 25 соединен с выходом триггера 45 и первым входом элемента 47, выход первого младшего разряда регистра 41 соединен с вторым входом элемента 47, третий вход которого соединен с вторым входом элемента 48 и выходом элемента 38.

В качестве коммутатора 1 можно использовать, например, восьмиканальный коммутатор цифровых дифференциальных сигналов [11] с коэффициентом помехоустойчивости Kh= 5 с запасом, удовлетворяющим ограничению (12), содержащий два компаратора, два мультиплексора-демультиплексора (две микросхемы 590КН6), два аттенюатора, формирователь положительного порогового напряжения, выход которого соединен с инвертирующим входом первого компаратора, формирователь отрицательного порогового напряжения, выход которого соединен с неинвертирующим входом второго компаратора, дифференциальный усилитель, выход которого соединен с не инвертирующим и инвертирующим входами первого и второго компараторов соответственно, выходы 16 и 17 приема "1" и "0" цифрового дифференциального сигнала, являющиеся выходами первого и второго компараторов соответственно, адресный кодовый трехразрядный вход, соединенный с адресными входами первого и второго мультиплексоров-демультиплексоров, информационные выходы которых соединены соответственно с прямым и инверсным входами дифференциального усилителя, и входы 11 и 12 первых и вторых компонент цифровых дифференциальных сигналов, связанные через каналы первого и второго аттенюаторов с информационными входами первого и второго мультиплексоров-демультиплексоров соответственно.

Декодер 3 выполнен с использованием принципа декодирования кода RZ, реализованного в примере схемы дешифратора кода RZ [4, с.102, рис.2.25] и содержит элемент ИЛИ-НЕ, триггер с асинхронными прямыми входами установки и сброса, входы 16 и 17 приема "1" и "0" кода RZ, соединенные с входами элемента ИЛИ-НЕ и входами установки и сброса триггера соответственно, выход 18 последовательного двоичного кода принимаемой информации, являющийся выходом триггера, и выход 19 импульсов битовой синхронизации, являющийся выходом элемента ИЛИ-НЕ.

При реализации устройства (фиг. 1-3) с использованием библиотеки элементов серии 533 цифровые составные части устройства можно выполнить следующим образом: регистр 2 - на ИС ИЕ7 так, что выход элемента 4 соединен с асинхронным инверсным входом загрузки ИС ИЕ7, используемой в качестве регистра, через который вход 13 данных связан с адресным входом коммутатора 1, причем у ИС ИЕ7 вход сброса и счетные входы соединены с шинами ЛОГИЧЕСКОГО 0 и ЛОГИЧЕСКОЙ 1 соответственно; счетчик 36 - на двух ИС ИЕ7, образующих байтовый вычитающий счетчик с асинхронной загрузкой с параллельного информационного входа, функционирующий по фронтам импульсов, действующих на его вычитающем счетном входе, причем каждая ИС ИЕ7 представляет собой 4-рязрядный реверсивный счетчик с асинхронным входом сброса (соединен с шиной ЛОГИЧЕСКОГО 0), асинхронным инверсным входом записи кода с информационного параллельного входа и суммирующим (+1) (соединен с шиной ЛОГИЧЕСКОЙ 1) и вычитающим (-1) счетными входами, обеспечивающих функционирование по фронтам действующих на счетных входах счетчика импульсов; регистр 41 - на двух ИС ИР11А, образующих байтовый регистр с асинхронным инверсным сбросом и синхронным функционированием по фронтам импульсов на тактовом входе в режиме параллельной записи кода (10...0) константы при W=1 или в режиме приема входного последовательного кода с выхода триггера 42 младшими разрядами вперед (т.е. со сдвигом вправо) при W=0, где W - сигнал режима функционирования регистра 41 на соответствующем входе каждой ИС ИР11А, представляющей собой 4-разрядный реверсивный регистр сдвига с параллельным выходом, синхронным последовательно-параллельным вводом и асинхронным инверсным сбросом; триггеры 31, 42, 43 и 45 - на двух ИС ТМ2, причем у триггеров 42 и 43 асинхронные инверсные входы сброса соединены с шиной ЛОГИЧЕСКОЙ 1 (на фиг.3 это не показано); элемент 50 - на ИС ИП5 - девятиразрядной схеме контроля четности и нечетности; остальные цифровые составные части устройства - на комбинационных элементах соответствующих ИС, в частности триггер 44 - на двух элементах 2И-НЕ ИС ЛА3, а триггер декодера 3 - на двух элементах 2ИЛИ-НЕ ИС ЛЕ1.

Описание функционирования устройства далее осуществляется с помощью системы положений и обозначений, определенных в следующих пунктах.

1. Входные и выходные (или промежуточные переменные формируемые на выходах составных частей устройства) прямые или инверсные переменные обозначим соответственно через Xi и Yk или NXi и NYk, где i - номер входа, a k - номер выхода или номер составной части. Например, NX8, NX9, NX10 - инверсные сигналы на входах 8, 9, 10 соответственно, X15 - прямой сигнал на входе 15 устройства, NY4 и NY5 - инверсные сигналы на выходах элементов 4 и 5. Кроме того, коды на входах 13 и 14, выходе 20, выходах регистра 2 и счетчика 3 обозначим соответственно через ID(2:0), Р(7:0), G(7:0), А(2:0) и С(7:0), где ID2, Р7, G7, А2 и С7 - старшие, а ID0, Р0, G0, А0 и С0 - младшие разрядные цифры (т.е. нули или единицы) этих кодов.

Смена канала ввода устройства производится при обмене в основном асинхронном режиме по сигналу записи NY8=0 в любой момент времени, а в не основном режиме по сигналу записи NY9=0 с учетом времени появления в УУО КЛС единичного сигнала PQ запроса или RDY готовности выбираемого канала, причем по сигналу NY8=0 (или NY9=0) триггер 35 сбрасывается (или устанавливается), а в счетчик 36 записывается код С[7: 0] =Р[7:0] (или счетчик 36 сбрасывается сигналом Y28=X9=1 в состояние С[7:0]=0...0).

2. Используется модифицированный язык описания логических функций ABEL, в котором операторы И, ИЛИ, НЕ и ИСКЛЮЧАЮЩЕЕ ИЛИ имеют обозначения "&", "#", "! " и "$" соответственно. Например, элементы 4 и 5 формируют переменные NY4 и NY5 согласно выражениям

NY4=NX8 & NX9, (17)

NY5=NY4 & NX10, (18)

т. е. знак "N" в левой части любого выражения, например (18), эквивалентен знаку "!" в правой части, поскольку

Y5=(Y4 # X10). (19)

3. Под фронтом или спадом любого сигнала (прямого или инверсного) понимается смена логического значения этого сигнала из "0" в "1" или из "1" в "0" соответственно.

4. Под сбросом (или установкой), например, триггера 45 понимается переключение этого триггера в состояние "0" (или "1").

5. В процессе функционирования устройства вырабатываются прямой сигнал Y25 готовности результата операции и инверсный потенциальный сигнал NY26 паузы так, что можно выделить четыре следующих режима его работы:

РР0 ожидания (холостого хода) при

Y25 NY26=0 0, (20)

РР1 преобразования при

Y25 NY26=0 1, (21)

РР2 готовности при

Y25 NY26=1 0, (22)

РР3 готовности и преобразования при

Y25 NY26=1 1. (23)

С учетом изложенного выше опишем сначала работу составных частей устройства, а затем его функционирование в целом как конечного автомата с памятью.

Функционирование отдельных составных частей устройства заключается в следующем.

Регистр 2 по сигналу NY4 и коду ID(2:0) работает так, что по каждому сигналу NY4= 0 код ID(2:0) асинхронно загружается в регистр 2 и в виде кода А(2:0) поступает на адресный вход коммутатора 1.

Коммутатор 1 по сигналам Ua(7:0) и Ub(7:0) первой и второй компонент цифровых дифференциальных сигналов восьми входных информационных каналов кода RZ и коду адреса А(2:0) выделяет для адресуемого канала

j=А0+(А1•2)+(А2•4), (24)

ослабленную часть цифрового дифференциального сигнала Uj, описанного во времени множеством (13), и для выбранного j-го канала в установившемся режиме формирует на выходах 16 и 17 цифровые сигналы Y16 и Y17 соответственно приема "1" и "0" кода RZ согласно выражениям

Y16=1, Y17=0 при Uj=Uj (9), (25)

Y16=0, Y17=1 при Uj=Uj (10), (26)

Y16=0, Y17=0 при Uj=Uj (11). (27)

Декодер 3, содержащий триггер и элемент ИЛИ-НЕ, по цифровым сигналам Y16 и Y17 вырабатывает на выходе 18 триггера сигнал Y18 последовательного двоичного кода информации, принимаемой по каналу j (24), а на выходе 19 элемента ИЛИ-НЕ формирует инверсные импульсы NY19 битовой синхронизации согласно выражению

NY19=!(Y16#Y17), (28)

причем триггер декодера 3 по сигналу Y16=1 (или Y17=1) асинхронно устанавливается (или сбрасывается), а при (Y16#Y17)=0 этот триггер находится в состоянии, обусловленном предысторией функционирования устройства.

Элементы 4 и 5 функционируют согласно выражениям (17) и (18) соответственно.

Обнаружитель 6 (фиг.2) по сигналам NX8 и NX9 записи, тактовым импульсам Х15, сигналу NY19 (28) и коду Р(7:0) вырабатывает инверсные потенциальный NY26 сигнал паузы и импульсный NY27 сигнал начала паузы согласно выражениям

NY26=Y35&Y32=Y35&[С0#С1#...#С6#С7], (29)

NY27=NY35#NY33=NY35#[NY37#C1#C2#...#C7] (30)

с помощью прямого Y35 и инверсного МY35 сигналов триггера 35, а также сигнала Y32 и инверсных импульсов NY33 и МY37, формируемых элементами 33, 34 и 37 согласно выражениям

Y32=С0#С1#...С6#С7, (31)

NY33=N37#C1#C2#...#C7, (32)

NY 37=!(X15&Y32). (33)

В процессе функционирования обнаружитель 6 по каждому сигналу NX8=0 устанавливается в первое состояние паузы (триггер 35 сбрасывается, в счетчик загружается кодом Р[7:0] по сигналу NY29=NX8=0) при работе в основном режиме обмена, а по NX9= 0 устанавливается во второе состояние паузы (триггер 35 устанавливается, счетчик 36 по сигналу Y28=X9=1 сбрасывается). Кроме того, при NY4= 1 и Y35=0 триггер 35 по фронту импульса NY33 переключается в единичное состояние и вырабатывает сигналы Y35=1 и NY35=0. В этой связи по каждому инверсному сигналу NY29 = NX8 & NY19 =0 счетчик 36 фиксируется в состоянии С(7: 0)= Р(7:0), которое определяет порог обнаружения паузы согласно выражению

Р=Р0+(Р1•2)+(Р2•4)+...+(Р7•128), (34)

а при NY4=1, NY29=1 и Y32=1 элемент 37 формирует ровно Р (34) импульсов NY37 (33) (отсчитываются от последнего сигнала NY29=0), по фронту каждого из которых содержимое счетчика 36 уменьшается на единицу, а по импульсу Р последовательности импульсов NY37 формируется импульс NY33, который при NY35= 0 проходит на выход элемента 34 как импульс NY27, а при NY35=1 импульс NY33 фронтом устанавливает триггер 35. По окончании импульса NY33 счетчик 36 переходит в состояние С(7:0)=(0...0), элемент 32 вырабатывает сигнал Y32=0 и запрещает прохождение импульсов X15 через элемент 37. Таким образом, обнаружитель 6 вырабатывает потенциальный инверсный сигнал паузы NY26=0 при Y35= 0 или при Y32=0 и инверсный импульсный сигнал NY27 начала паузы при Y35=1 по импульсу NY33, который формируется по импульсу NY37 при С(7:0)=(0...01) и NY26=1. В этой связи после установки по сигналу NY8=0 в первое состояние паузы обнаружитель 6 выйдет из этого состояния (выставит сигнал NY26=1) точно по началу импульса NY19= 0 битовой синхронизации младшего бита очередного n-разрядного кода (n принадлежит множеству (1)) j-го канала. Выбор частоты f тактовых импульсов X15 и программируемого кода Р(7:0), соответствующего каждому элементу F множества (3), обеспечивает многоканальный прием устройством информации при обмене как основным асинхронным способом, так и неосновным (по запросу или по готовности). Смена канала при обмене асинхронным способом может производиться по сигналу NX8=0 в любой момент времени, а при обмене неосновным способом должна производиться по сигналу NX9=0 с учетом времени появления в УУО КЛС единичного сигнала PQ или RDY соответствующего j-го канала. Выбор порога Р (34) для обнаружения паузы в зависимости от битовой скорости F=1/T и тактовой частоты f импульсов X15 на входе 15 при любом обмене следует проводить из условия

(T•1,5)≥P/f>T, (35)

которое трансформируется в формулу

Р=ent(f/F)+C, (36)

где ent - оператор выделения целой части числа (f/F);

С - целое число, не меньшее "1", выбираемое с учетом выполнения ограничения (35).

По формуле (36) для выбранной частоты, например f=3 МГц, при С=1 получаем множество порогов

{Р}={241, 64, 31, 13, 7, 4}, (37)

каждый элемент которого определен элементом множества (3) и определяет программируемый код Р(7:0) на основе (34).

Если для всех каналов устройства частота F, принадлежащая множеству (3), одинакова, то на кодовый вход 14 подключается соответствующий постоянный код Р(7: 0), в противном случае в составе УУО КЛС должен содержаться регистр памяти кода Р(7:0), загружаемый программно от ЭВМ при смене частоты F.

Преобразователь 7 (фиг.3) по сигналу Y18 последовательного двоичного кода, инверсным импульсам NY19 (28) битовой синхронизации, инверсному потенциальному сигналу NY26 (29) паузы, инверсному импульсному сигналу NY27 (30) начала паузы и инверсному сигналу сброса NY5 (18) вырабатывает фрагменты G(7: 0) параллельно-последовательного кода принимаемой информации, импульсы Y21 синхронизации фрагмента G(7:0), сигнал Y22 информационной ошибки при четном числе единиц в принятом коде, сигнал Y23 сбоя битовой синхронизации при длине принятого кода, не кратной байту, сигнал Y24 готовности фрагмента G(7: 0) и сигнал Y25 готовности результата операции. В процессе функционирования преобразователя 7 (как и всего устройства) можно выделить четыре режима работы, которые определены выражениями (20)-(23).

В исходном режиме РР0 (20) триггеры 43 и 44 установлены, триггер 45 сброшен, сигналом NY26=0 регистр 41 сброшен, а триггер 42 установлен. Установка преобразователя 7 в исходное состояние осуществляется по сигналу NY5= NY4= (NX8# NX9)= 0 в любом режиме либо по сигналу NY5=NX10=0 при переходе из режима РР2 (22) в режим РР0 (20).

Переход из режима РР0 в режим РР1 отмечается появлением сигнала NY26=1, последовательности из П импульсов NY19 битовой синхронизации и сигнала Y18 последовательного двоичного кода, длина которого должна принадлежать ряду (1), т. е. для корректного функционирования устройства число П также должно принадлежать ряду (1). По фронту каждого импульса NY19 триггер 42 устанавливается в состояние

G7=Y18 (в момент фронта NY19), (38)

а содержимое регистра 41 при Y24=0 сдвигается вправо с приемом в старший разряд G6 бита G7 (в момент фронта NY19), а при Y24=1 старший разряд G6 регистра 41 устанавливается, а младшие разряды сбрасываются, т.е. G(6:0)= (1000000), Y24= 0. Следовательно, например, при П=32 после окончания 8-го, 16-го, 24-го, 32-го импульса NY19 регистр 41 выставит сигнал Y24 готовности 0-го, 1-го, 2-го, 3-го фрагмента параллельно-последовательного кода

G(7:0)=D(7:0), D(15:8), D(23:16), D(31:24), (39)

а затем сформирует импульс

Y21=(Y19&Y24)#Y27 (40)

синхронизации фрагмента (39) по 9-му, 17-му, 25-му импульсам NY19 и импульсу NY27. По фронту каждого импульса Y21 триггер 43 устанавливается в состояние

Y22=Y50 (в момент фронта Y21), (41)

определяемое сигналом

Y50=(G7$G6$G5$G4$G3$G2$G1$G0)$Y22, (42)

который формирует элемент 50 согласно принципам контроля по модулю два [5, с.67-77: "2.2. Схемы контроля"], например, принятого кода D(31:0), содержащего четыре фрагмента параллельно-последовательного кода (39). По каждому импульсу NY27= 0 триггер 45 устанавливается и выставляет сигнал Y25=1 готовности результата, а элемент 40 только при NY39=!Y24=0 формирует импульс NY40= (! Y24)# NY27=0 сброса триггера 44. В этой связи в режиме РР2 (22) или РР3 (23) сигналы Y22 и Y23 вырабатываются так, что при (Y22#Y23)=0 сбоев не обнаружено, при Y22=1 обнаружена информационная ошибка (четное число единиц в принятом коде, например коде D(31:0)), при Y23=1 обнаружен сбой битовой синхронизации, т.е. определено, что в закончившейся операции преобразования число импульсов NY19 не кратно восьми.

По окончании импульса NY27 обнаружитель 6 выставляет сигнал NY26=0 паузы и устройство переходит в режим РР2 (22), в котором по сигналу Y25=1 прерывает ЭВМ для сообщения о завершении очередной операции преобразования. В процессе выполнения прерывающей программы ЭВМ может сформировать сигнал NX10=0 сброса готовности результата, который через элемент 5 сбрасывает триггер 45, а через элементы 5 и 49 устанавливает триггеры 43 и 44. Если ЭВМ сигнал NX10 не формирует, то с поступлением на выбранный канал j устройства информационного сигнала Uj кода RZ декодер 3 формирует очередную последовательность П импульсов NY19 битовой синхронизации. По первому импульсу этой последовательности устройство переходит в режим РР3 (23), а по восьмому импульсу NY19 элемент 47 формирует импульс

NY47=!(Y19&G0&Y25), (43)

который через элемент 49 устанавливает триггеры 43 и 44 и непосредственно фронтом сбрасывает триггер 45, переключая тем самым устройство в режим РР1 (21).

Функционирование устройства как конечного автомата с памятью состоит в чередовании режимов его работы, например РР0, РР1, РР2, РР3, РР1 и т.п., так, что: переход в РР0 может быть осуществлен из любого режима по сигналу NY4=(NX8#NX9)=0 записи или из режима РР2 по сигналу NX10=0 сброса готовности результата; переход в РР1 - из РР0 непосредственно по первому импульсу NY19 последовательности П импульсов битовой синхронизации, а также из режима РР3 по сигналу NX10=0 или окончании импульса NY47; переход в РР2 - из РР3 по окончании импульса NY27; переход в РР3 - из режима РР1 в течение действия импульса NY27 либо из режима РР2 непосредственно по первому импульсу NY19 последовательности П импульсов битовой синхронизации.

Наличие на выходах устройства сигналов Y21 синхронизации и Y24 готовности каждого фрагмента G(7:0) параллельно-последовательного кода (его запись при n= 32 дана в (39)) и Y25 готовности результата обеспечивает множество вариантов передачи в ЭВМ через УУO результата операции

{D((n-l):0), Y22, Y23}, (44)

где n - принадлежит множеству (1).

Опишем два возможных варианта ввода результата (44) по импульсам Y21 синхронизации и Y24 готовности фрагмента.

В первом случае в УУО по фронту каждого импульса Y21 текущий фрагмент G(7: 0) загружается в регистр типа ИР23 и вызывает прерывание ЭВМ первого типа. При выполнении первой прерывающей программы ЭВМ в своей внутренней оперативной памяти формирует код D((n-1):0). По окончании каждой операции устройство выставляет сигнал Y25=1, вызывающий прерывание ЭВМ второго типа. При выполнении второй прерывающей программы ЭВМ считывает оставшуюся часть { Y22, Y23} результата (44), формирует сигнал NX10=0 сброса результата, затем при (Y22# Y23)= 0 пересылает информационную часть кода D((n-1):0) абоненту (приемнику), а при (Y22#Y23)=1 результат (44) игнорируется, поскольку обнаружена информационная ошибка при Y22=1 или/и сбой битовой синхронизации при Y23=1.

Во втором случае УУО по каждому сигналу Y24=1 записывает каждый фрагмент G(7: 0) в свою ячейку оперативной памяти (ОЗУ или ДОЗУ, либо аппаратный стек или регистр). По окончании каждой операции устройство выставляет сигнал Y25= 1 прерывания ЭВМ, которая выполняет прерывающую программу, аналогичную второй прерывающей программе, описанной для первого случая.

Из описания видно, что предлагаемое устройство благодаря его существенным признакам проще прототипа [1] и по сравнению с ним имеет более широкую область использования, так как обладает требуемой помехоустойчивостью при расширенных функциональных возможностях. В этой связи данное устройство можно использовать при построении бортовых аппаратно простых КЛС, поддерживающих с высокой достоверностью в локальной сети с радиальной топологией многоканальный обмен самосинхронизирующимися последовательными двоичными кодами с различными длинами и скоростями, принадлежащими, например, рядам (1) и (3) соответственно.

Литература

1. А.с. 1786491, G 06 F 13/00, СССР. Устройство для ввода информации. Д. Ю. Гусев и Ю.В. Крюков. Опубл. 07.01.1993. Бюл. 1 (Прототип).

2. Организация последовательных мультиплексных каналов систем автоматического управления. С.Т. Хвощ, В.В. Дорошенко, Ленингр. Отделение, 1989. - 271 с.

3. "2.2. Методы передачи дискретных данных на физическом уровне" - с. 132-149 в книге: Компьютерные сети. Принципы, технологии, протоколы. В.Г. Олифер, Н.А. Олифер - СПб. Питер. 2001. - 672 с.

4. Ю.В. Новиков, Д.Г. Карпенко. Аппаратура локальных сетей: функции, выбор, разработка. Под общей редакцией Ю.В. Новикова. М.: Издательство ЭКОМ, 1998. - 288 с.

5. Угрюмов Е. П. Цифровая схемотехника. СПб.: БХВ - Петербург, 2001. - 528 с.

6. Щербаков Н.С. Достоверность работы цифровых устройств. - М.: Машиностроение, 1989. - 224 с.

7. Контроль функционирования больших систем. Г.П. Шибанов, Е.А. Артеменко, А. А. Матешкин, Н. И. Циклинский. Под ред. заслуженного изобретателя РСФСР д.т.н. Г.П. Шибанова. М.: Машиностроение, 1977, 360 с.

8. А.с. 1068927, G 06 F 3/04, Устройство для ввода информации. Л.П. Горохов, Р.Ю. Хальфан и В.А. Генина. Опубл. 23.01.1984. Бюл. 3.

9. А.с. 1081637, G 06 F 3/00, СССР. Устройство для ввода информации. В. М. Задорина и А.В. Кочетков. Опубл. 22.03.1984. Бюл. 11.

10. Детектор допусковой зоны для сигнала Uc, - с.229, рис. 5.8 д в книге: Шило В.Л. Линейные интегральные схемы в радиоэлектронной аппаратуре. 2-е изд., перераб. и доп. М.: Советское радио, 1979. 368 с.

11. Заявка 2000127331/09(028924), Н 03 К 17/76, G 06 F 13/00, G 06 F 3/00. Коммутатор цифровых дифференциальных сигналов от 30.10.2000. Авторы Киселев Е.Ф., Зуев А.И., RU. Решение ФИПС о выдаче патента на изобретение от 14.01.2002.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2207614C1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 2001 |

|

RU2202121C2 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ КОД | 2001 |

|

RU2188502C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО ДВОИЧНОГО КОДА В ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ КОД | 2001 |

|

RU2220502C2 |

| КОММУТАТОР ЦИФРОВЫХ ДИФФЕРЕНЦИАЛЬНЫХ СИГНАЛОВ | 2000 |

|

RU2190927C2 |

| ДЕКОДЕР ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА КОДА RZ | 2005 |

|

RU2291560C1 |

| ДЕКОДЕР ТРЕХУРОВНЕВОГО КОДИРОВАННОГО СИГНАЛА | 2007 |

|

RU2333600C1 |

| КОММУТАТОР ЦИФРОВЫХ ДИФФЕРЕНЦИАЛЬНЫХ СИГНАЛОВ | 2003 |

|

RU2257005C1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА, ПРЕОБРАЗОВАНИЯ И СИНХРОНИЗАЦИИ ЦИФРОВОГО ДИФФЕРЕНЦИАЛЬНОГО СИГНАЛА | 2004 |

|

RU2279182C1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО КОДА В ПОСЛЕДОВАТЕЛЬНЫЙ | 2000 |

|

RU2187887C2 |

Устройство для ввода информации относится к области вычислительной техники и предназначено для выполнения в режиме разделения во времени операции многоканального приема и преобразования самосинхронизирующихся последовательных двоичных кодов от каналов с одинаковыми или различными длинами и битовыми скоростями. Техническим результатом является расширение области использования устройства путем повышения его помехоустойчивости и комплексного расширения его функциональных возможностей для приема информации по любому способу обмена с фиксированными или различными длинами и обнаружением информационной ошибки и сбоя битовой синхронизации. Устройство содержит коммутатор, регистр, декодер, входы первой и второй компонент цифровых дифференциальных сигналов последовательных самосинхронизирующихся двоичных кодов, кодовый вход данных, информационный кодовый выход, два входа записи, тактовый вход, вход сброса готовности результата операции и выход готовности результата операции, элементы И, обнаружитель паузы, преобразователь последовательного двоичного кода в параллельно-последовательный код. 3 ил.

Устройство для ввода информации, содержащее коммутатор, регистр, декодер, входы первой и второй компонент цифровых дифференциальных сигналов самосинхронизирующихся последовательных двоичных кодов каналов вводимой информации, являющихся информационными входами коммутатора, кодовый вход данных, связанный через регистр с адресным входом коммутатора, выходы приема "1" и "0" самосинхронизирующегося кода выбранного канала которого соединены с входами декодера, два входа записи, вход сброса готовности результата операции, тактовый вход, информационный кодовый выход и выход готовности результата операции, отличающееся тем, что оно дополнительно содержит два элемента И, обнаружитель паузы, тактовый вход которого соединен с тактовым входом устройства, преобразователь последовательного двоичного кода в параллельно-последовательный код, выход фрагмента параллельно-последовательного кода которого соединен с информационным кодовым выходом, программируемый кодовый вход порога обнаружения паузы, соединенный с кодовым входом обнаружителя паузы, и выходы синхронизации фрагмента параллельно-последовательного кода, информационной ошибки, сбоя битовой синхронизации и готовности фрагмента, соединенные соответственно с первым, вторым, третьим и четвертым выходами преобразователя, пятый выход которого соединен с выходом готовности результата операции, первый и второй входы записи устройства соединены соответственно с входами установки в первое и второе состояния паузы обнаружителя и входами первого элемента И, выход которого соединен с асинхронным инверсным входом записи регистра и первым входом второго элемента И, второй вход которого соединен с входом сброса готовности результата операции устройства, а выход соединен с входом сброса преобразователя, выход последовательного кода декодера соединен с информационным входом преобразователя, тактовый вход которого соединен с выходом импульсов битовой синхронизации декодера и входом записи обнаружителя паузы, который содержит два входа установки в первое и второе состояния паузы соответственно, кодовый вход, тактовый вход, вход записи, выходы потенциального сигнала паузы и импульсного сигнала начала паузы, первый элемент НЕ, третий и четвертый элементы И, с первого по четвертый элементы ИЛИ, первый триггер, счетчик и первый элемент И-НЕ, первый вход которого соединен с тактовым входом обнаружителя, кодовый вход которого соединен с информационным параллельным входом счетчика, выходы старших разрядов которого соединены с входами первого элемента ИЛИ, выход которого соединен с первыми входами второго и третьего элементов ИЛИ, вход установки в первое состояние паузы обнаружителя соединен с первым входом третьего элемента И и асинхронным инверсным входом сброса первого триггера, асинхронный инверсный вход установки которого соединен с входом установки во второе состояние паузы обнаружителя и связан через первый элемент НЕ с входом сброса счетчика, вход записи обнаружителя соединен с вторым входом третьего элемента И, выход которого соединен с асинхронным инверсным входом записи счетчика, выход младшего разряда счетчика соединен с вторым входом второго элемента ИЛИ, выход которого соединен с первым входом четвертого элемента И и вторым входом первого элемента И-НЕ, выход которого соединен с вычитающим счетным входом счетчика и вторым входом третьего элемента ИЛИ, выход которого соединен с первым входом четвертого элемента ИЛИ и тактовым входом первого триггера, информационный вход которого соединен с шиной ЛОГИЧЕСКОЙ 1, прямой и инверсный выходы первого триггера соединены соответственно с вторыми входами четвертого элемента И и четвертого элемента ИЛИ, выходы которых являются соответственно выходами потенциального сигнала паузы и импульсного сигнала начала паузы обнаружителя, которые соединены соответственно с потенциальным и импульсным управляющими входами преобразователя, который содержит входы информационный, тактовый, потенциальный управляющий, импульсный управляющий, сброса, выход фрагмента параллельно-последовательного кода, пять выходов, второй и третий элементы НЕ, пятый элемент ИЛИ, регистр сдвига с последовательно-параллельным вводом и параллельным выводом, триггеры с второго по пятый, второй, третий и четвертый элементы И-НЕ, пятый элемент И и элемент контроля по модулю два, кодовый вход которого соединен с выходом фрагмента параллельно-последовательного кода, выходы младших разрядов которого соединены с выходами старших разрядов регистра сдвига, а выход старшего разряда фрагмента соединен с информационным последовательным входом регистра сдвига и выходом второго триггера, информационный вход которого является информационным входом преобразователя, тактовый вход которого соединен с входом второго элемента НЕ и тактовыми входами второго триггера и регистра сдвига, информационный параллельный вход которого соединен с входом кода константы, у которого старший бит единица, а остальные биты нули, первый выход преобразователя соединен с выходом второго элемента И-НЕ и тактовым входом третьего триггера, выход которого соединен с вторым выходом преобразователя и битовым входом элемента контроля по модулю два, выход которого соединен с информационным входом третьего триггера, выход пятого элемента И соединен с асинхронными инверсными входами установки третьего и четвертого триггеров, третий выход преобразователя соединен с выходом четвертого триггера, асинхронный инверсный вход сброса которого соединен с выходом пятого элемента ИЛИ, первый вход которого соединен с выходом третьего элемента НЕ, асинхронные инверсные входы сброса регистра сдвига и установки второго триггера соединены с потенциальным управляющим входом преобразователя, импульсный управляющий вход преобразователя соединен с вторым входом пятого элемента ИЛИ, первым входом второго элемента И-НЕ и асинхронным инверсным входом установки пятого триггера, асинхронный инверсный вход сброса которого соединен с входом сброса преобразователя и первым входом пятого элемента И, второй вход которого соединен с выходом третьего элемента И-НЕ и тактовым входом пятого триггера, информационный вход которого соединен с шиной ЛОГИЧЕСКОГО 0, четвертый выход преобразователя соединен с выходом нулевого младшего разряда и управляющим входом "Параллельная запись/сдвиг вправо" регистра сдвига, входом третьего элемента НЕ и первым входом четвертого элемента И-НЕ, выход которого соединен с вторым входом второго элемента И-НЕ, пятый выход преобразователя соединен с выходом пятого триггера и первым входом третьего элемента И-НЕ, выход первого младшего разряда регистра сдвига соединен с вторым входом третьего элемента И-НЕ, третий вход которого соединен с вторым входом четвертого элемента И-НЕ и выходом второго элемента НЕ.

| Устройство для ввода информации | 1990 |

|

SU1786491A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 1999 |

|

RU2159952C1 |

| УСТРОЙСТВО ВВОДА-ВЫВОДА ИНФОРМАЦИИ ДЛЯ СИСТЕМЫ ЦИФРОВОГО УПРАВЛЕНИЯ | 1993 |

|

RU2042183C1 |

| Устройство для ввода информации | 1982 |

|

SU1068927A1 |

| Устройство для ввода информации | 1982 |

|

SU1081637A1 |

| US 3787820 А, 20.01.1974. | |||

Авторы

Даты

2003-12-27—Публикация

2002-04-29—Подача