1

определяется его максим.значение. Длительность циклов анализа амплитуды входного сигнала намного меньше длительности элементарной посылки. При появлении на входе интегратора 1 низкого уровня О (стартовая посылка) на выходе RS-триггера 20 появляется низкий уровень преобразованной телеграфной посьшки. При появлении на входе интегратора 1

23А977

высокого уровня (токовая посыпка) RS-триггер 20 переходит в новое состояние, соответствующее высокому уровню преобразованной посылки (токовой посылки) входного сигнала. Цель достигается введением ПБЗ, PC 8 и 16, МБ 9 и 17, компараторов кодов 10 и 18, D-триггера 11, элементов И 12, 13, 14 и 15, элемента ИЛИ 19 и RS-триггера 20. 1 з.п.ф-лы, 1 ил.

«

Изобретение относится к электросвязи и может использоваться для регенерации телеграфных посылок в системах телеграфной связи.

Целью изобретения является повы- шение точности и помехоустойчивости регенерации телеграфных: посылок.

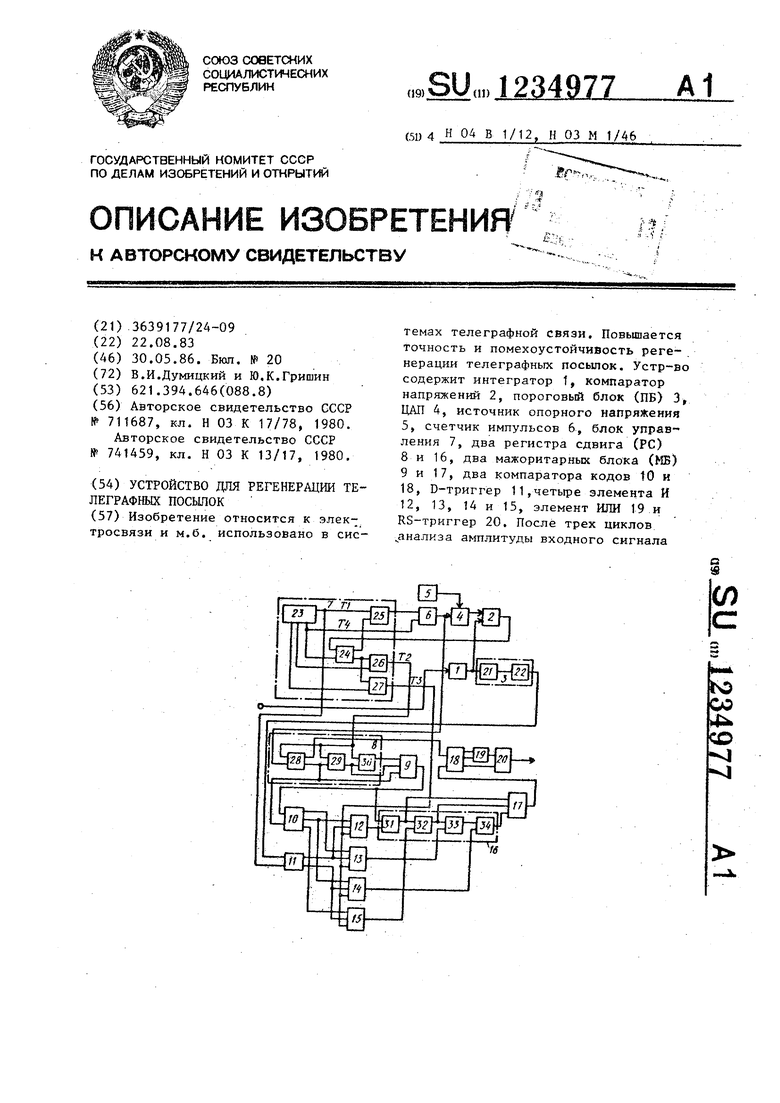

На чертеже представлена структурная электрическая схема устройства для регенерации телеграфных посыпок

Устройство для регенерации телеграфных посылок содержит интегратор 1, компаратор 2 напряжений, порого- вьй блок 3, цифроаналоговый преобразователь (ЦАП) 4, источник опорного напряжения 5, счетчик 6 импульсов, блок управления 7, первый регистр 8 сдвига, первый мажоритарный блок 9, второй компаратор 10 кодов, 1)-триг- гер 11, первый, второй, третий, чет- вертый элементы И 12 - 15, второй ре гнстр 16 сдвига, второй мажоритарный блок 17, первый компаратор 18 кодов, элемент ИЛИ 19, RS-триггер 20.

Пороговьй блок 3 содержит дели- тель напряжения 21 и пороговый элемент 22.

Блок управления 7 содержит формирователь 23 тактовых импульсов, RS-триггер 24, первый, второй и тре- тий элементы И 25 - 27

Первый регистр 8 сдвига содержит первьй, второй и третий разряды 28 - 30.

Второй регистр 16 сдвига содержи первый, второй, третий и четвертый разряды 31 - 34.

Устройство для регенерации телеграфных посылок работает следукнцим образом.

При входном сигнале с низким уровнем (Ug 0), поступающим на вход устройства для регенерации телеграфных посыпок, напряжение на выходе интегратора 1 (и) равно выходному напряжению ЦАП 4 (U, ), на выходе компаратора 2 высокий уровень сигнала, который запрещает подачу тактовых импульсов Т1 (высокой частоты) с первого тактового выхода блока управления 7 на счетньш вход счетчика 6. При U| и импульсом Т4 с четвертого тактового выхода блока .управления 7 счетчик 6 устанавливается, в начальное состояние. На выходах счетчика 6 устанавливается кодовая комбинация 00000, которая переписывается в первьй регистр 8 тактовыми импульсами 12, поступающими со второго тактового выхода блока управления 7.

Б первьй разряд 28 первого регистра 8 (один раз за цикл работы ДАЛ 4) записывается информация (число) со счетчика 6 полностью, а во второй и третий разряды 29 и 30 первого регистра 8 записывается число, деленное на два. При этом используются тактовь1е импульсы Т2.

Тактовые импульсы Т1 подаются на счетный вход D-триггера 11, которьш управляется по D-входу пороговым блоком 3, вход которого подключен к выходу интегратора 1. Поэтому на выходе порогового блока 3 будет сигнал О. На прямом выходе D-триггера 11 будет также сигнал О.

Блок управления 7 вьщает тактовые импульсы, которые формируют цикл работы устройства для регенерации

телеграфных посьшок; тактовые импульсы Т1 поступают на вход счетчика 6 только с разрешения компонента 2, а начало счета ЦАП 4 происходит по тактовым импульсам Т4.

Если на входе интег-ратора 1 появился нарастающий фронт сигнала

и

0, тогда на его выходе появляется задержанное плавно нарастающее напряжение, И как только разность напряжений на первом и втором входах компаратора 2 достигла порога срабатывания (и„„р) Uj и„, на его выходе появляется уровень О, который поступает на вход блока управле- ния 7 (на RS-триггер 24). При появлении тактового импульса Т4 RS-триггер 24 разрешает подачу тактовых импульсов Т1 через первый элемент И 25 на счетный вход счетчика 6. Последний начинает счет и на его вькоде появляется двоичная информация, которая преобразуется ЦАП 4 в аналоговый сигнал и подается на первьй

вход компаратора 2, Как только напря жение Uj на первом входе компаратора 2 станет равным напряжению U на его втором входе, на выходе компаратора 2 появится высокий уровень (сигнал 1), который, поступив на вход блока управления 7, запретит подачу тактовых импульсов Т1 на счетчик 6, При этом на выходе счетчика 6-появится кодовая комбинация, соответствующая уровню аналогового сигнала на входе устройства для регенерации телеграфных посьшок,

Тактовым импульсом Т2 происходит перезапись двоичной информации со

счетчика 6 в первый разряд 28 перво- гося максимального значения.

го регистра 8, Пусть, например, в первьй разряд была записана кодовая комбинация 00011. При этом D-триггер 11 остался в прежнем положении. Напряжение на втором входе компаратора 2 продолжает плавно нарастать, и при Ц и на его выходе появляется уровень О, разрешающий подачу тактовых импульсов Т1 на счетчик 6 после появления тактового импульса Т4, Данный процесс продлится до момента времени, при котором будет выполняться условие Uj и , Пусть это будет соответствовать кодовой комбиВысокий уровень Г со второго компаратора 10 поступает на первые входы первого и третьего элементов И 12 и 14, но полное разрешение при- 5 ходит только на первый элемент И 12, на третьем входе которого присутствует высокий уровень 1 с прямого выхода D-триггера 11. Тактовый импульс ТЗ из блока управления 7 через первый элемент li 12 поступает на первый разряд 31 второго регистра 16 и записывает в него с выхода первого мажоритарного блока 9 среднее значение текущего кода 1100. Если

нации 01010, До получения этой комби-55входной сигнал будет постоянным,

нации на выходе порогового блока 3то при последующих циклах анализа

появляется высокий уровень напряжения,кодовая комбинация с первого разряда|

поступающий на D-вход D-триггера 11,31 второго регистра 16 не перепишет

10

5

349774

который по тактовому импульсу Т1 переходит в состояние 1 (на его прямом выходе уровень 1). При появлении тактового импульса Т2 происходит перезапись кодовой комбинации со счетчика 6 в первьй разряд 28, а предьщущий поделенньй код поступает во второй разряд 29. Таким образом, в первом, втором и третьем разрядах 28 - 30 первого регистра 8 записаны следующие комбинации: 0101, .0001, 0000,

Полученные кодовые комбинации параллельно поступают на мажоритарный блок 9, где они сравниваются, В результате на выходе мажоритарного блока 9 появляется кодовая комбинация 0001. Одновременно на второй компаратор tO поступают кодовые комбинации с первого разряда 28 первого регистра 8 (код А) и с первого мажоритарного блока 9 (код В), В результате сравнения значений поступающих кодов на втором выходе (А В) второго

20

компаратора 10 появляется высокий уровень t, поскольку код А (0101) превышает код В (0001),

. После трех описанных циклов анализа амплитуды входного сигнала в первом, втором и третьем разрядах 28-30 первого регистра 8 запишутся следующие кодовые комбинация: 1100, 1100, 0101. Тогда на выходе первого мажоритарного блока 9 будет коловая комбинация НОО и на первом выходе () второго компаратора 10 появится высокий уровень 1, что соответствует равенству кодов А и В, Это означает, что входной сигнал достиг в данный момент времени установившеВысокий уровень Г со второго компаратора 10 поступает на первые входы первого и третьего элементов И 12 и 14, но полное разрешение при- ходит только на первый элемент И 12, на третьем входе которого присутствует высокий уровень 1 с прямого выхода D-триггера 11. Тактовый импульс ТЗ из блока управления 7 через первый элемент li 12 поступает на первый разряд 31 второго регистра 16 и записывает в него с выхода первого мажоритарного блока 9 среднее значение текущего кода 1100. Если

входной сигнал будет постоянным,

я во второй, третий и четвертый азряды 32-3 i,

При появлении на входе интегратора 1 низкого уровня О (стартовая посылка) на выходе интегратора 1 напряжение плавно начинает снижаться до нулевого значения. При записи тактовым импульсом Т2 в первый разряд 28 кодовой комбинахдаи 01110 в первом.) втором и третьем разрядах 28-30 первого регистра 8 записываются следующие кодовые комбинации: 0111, 1100, 110Q, На третьем выходе (А В) второго компаратора 10 появляется высокий уровень 1, которьй поступает на первый вход четвертого элемента И 15, на третьем входе которого присутствует сигнал с низким уровгшм О. Следовательно, в этом цикле тактовый импульс ТЗ через четвертый элемент И 15 на тактовьй вход второго разряда 32 не попадает.

При переходе в одном из последующих циклов анализа амп-литуды входного сигнала D-триггера 11 в состояние О (на его инверсном выходе уровень 1) сигнал с инверсного выхода D-триггера 11 поступает на третий вход четвертого элемента И 15 Тактовый импульс проходит через четвертый элемент И 15 и переписывает кодовую комбинапд110 из первого разряда 31 во второй разряд 32. Далее происходит сравнение кодовых комбинаций, записанных в первом и втором разрядах 31 и 32, во втором мазко-- ритарном блоке 17, При этом кодовые комбинации в первом и втором разрядах 31 и 32 второго регистра 16 составляют 1100, 1100, в то время как в третьем и четвертом разрядах 33 н 34 могут быть записаны произвольные кодовые комбинации. На выходе второго мажоритарного блока 17 будет значение кода 1100, которое поступает на пер- вьй компаратор IS, на которьй также поступает текуцщй код с первого разряда 28 первого регистра 8 0001. При этом на первом выходе первого компаратора 18 появляется высокий уровень 1 (так как код 1100 превышает код 0001), который через элемент ИЛИ 19 поступает на RS-триггер 20, На выходе RS-триггера 20 появляется низкий уровень преобразованной телеграфной посьшки.

Длительность циклов анализа ампли- туды входного сигнала намного мень

0

0

0

5

0

5

ше длительности элеметттарной гюсьш- ки. Поэтому при анализе бестоковой посьшки в первом регистре 8 в определенное время устанавливаются одинаковые коды, но перезаписи мажоритарного значения кода из второго разряда 32 в третий разряд 33 не будет. Но при появлении на входе интегратора 1 высокого уровня (токовая посылка) на его выходе появляется плавно нарастающее напряжение. Снова срабатывает пороговый блок 3, и на прямом выходе Ь-триггера 11 появляется высокий уровень напряжения, которьй поступает на третьи входы первого и второго элементов И 12 и 13,

При записи в этот момент в первом, втором и третьем разрядах 28-30 первого регистра 8 кодовых комбинаций 0111, 0101,0000 соответственно на выходе первого мажоритарного блока 9 имеется кодовая комбинация 0101, а на втором выходе второго компаратора 10 - сигнал 1, которы поступает на первый вход второго элемента И 13, Через него проходит такто- зьй импульс ТЗ и перезаписывает код I100 из второго разряда 32 в третий разряд 33. Далее второй мажоритар- ньй блок 17 производит одновременное сравнение кодов первого, второго и четвертого разрядов 31, 32 и 34, В результате на выходе вторе. о мажоритарного блока 17 формируется код 1100, При поя7-, 1знни на втором выходе первого комг.гйратора 18 высокого уровня 1, RS-тригггр 20 лереходит в новое состояние, соответствующее высокому уровню преобразованной ПОСЫЛКЕ- : (токовой посыпки) входного сигнала.

Запись кодовой комбинации 1100 в четвертьй разряд 34 второго регистра 16 происходит при последующем появлении бестоковой посьшки, когда хотя бы в первом и втором разрядах

28и 29 (втором и третьем разрядах

29и 30) первого регистра 8 будут равные кодовые комбинацииj соответст- ву1о.цие уровню О.

«Формула изобретения

1 о Устройство для регенерации телеграфных посыпок, содержащее последовательно соединенные блок управления, счетчик импульсов, цифроана- логовьй преобразователь и компаратор

напряжений, a также интегратор и источник опорного напряжения, выход которого подсоединен к опорному входу цифроаналогоного преобразователя выход интегратора подсоединен к вто- poNry входу компаратора напряжений, выход которого подсоединен к входу блока управления, причем вход интегратора является входом устройства, отличаюгдееся тем, что, с целью повьшения точности и помехоустойчивости регенерации телеграфных посылок, в него введены последовательно соединенные первый регистр сдвига, первый мажоритарньй блок, второй регистр сдвига, второй мажо- ритарньй блок, первый компаратор кодов, элемент ИЛИ-и RS-триггер, последовательно соединенные порого- вый блок и D-триггер, последовательно соединенные второй компаратор кодов и первый элемент И, а также второй, третий и четвертьпЧ элементы И, при этом первые входы вто- porOj третьего и четвертого элементов И подключены соотзетственно к второму, первому и третьему выходам второго компаратора кодов, первьгй тактовый выход блока управления год- соединен к счетному входу D-триггера второй тактовый выход блока управления подсоединен к тактовьпч входам первого, второго и третьего разрядов первого регистра сдвига, третий тактовый выход блока управления подсоединен к вторым входам первого, второго, третьего и четвертого элементов И, четвертьй тактовый выход блока управления подсоединен к управляющему входу счетчика импульсов выход которого подсоединен к информационному входу первого регистра сдвига, выход интегратора подсоединен к входу порогового блока, первый первого разряда первого регистра сдвига подсоединен к второму входу первого компаратора кодов, второй выход первого разряда первого регистра сдвига подсоединен к первому входу второго компаратора кодов и второму входу первого мажоритарного блока, третий вход которого под- ключен к выходу второго разряда первого регистра сдвига, выход первого

ВНИКНИ Заказ 2990/58 Тираж 624

ПроизБ.-полигр. пр-тне г. Ужгород, ул. Проектная, 4

Q 5 20 25 jg

5

0

0

мажоритарного блока подсоединен к второму в ходу второго компаратора кодов, инверсный выход D-триггера подсоединен к третьим входам третьего и четвертого элементов И, прямой выход D-триггера подсоединен к третьим входам первого и второго элементов И, выходы первого, второго, третьего- и четвертого элементов И подсоединены к тактовым входам соответственно первого, третьего, четвертого и второго разрядов второго регистра сдвига; выходы первого и второго разрядов второго регистра сдвига подсоединены соответственно к второму и третьему входам второго мажоритарного блока, а третий выход первого компаратора кодоз подсоединен к R- входу RS - триггера причем выход RS -тригера является выходом устройства.

2. Устройство по п. t, о т л и чающееся тем, что блок управления выполнен в виде последовательно соединенных формирователя тактовых импульсов и первого элемента И, последовательно соединенных RS-триггера и второго элемента И, а также третьего элемента И, второй вход второго элемента И подключен к втором выходу формирователя тактовых импульсов, третий выход ко -орого подсоединен к первому входу третьего элемента И, второй вход которого подключен к инверсном выходу RS-триггера, четвертый выход формирователя тактовых импульсов подсоединен к S-входу RS-триггера, прямой выход которого подсоединен к второму входу первого элемента И, причем R-вход RS-триггера является входом блока управления, первый выход формирователя тактовых импульсов является первым тактовым выходом блока,- управления, выходы второго и третьего элементов И являются соответственно вторым и третьим тактовыми выходами блока управления, четвертый выход формирователя тактовых импульсов является четвертым тактовым выходом блока управления, а выход первого элемента И является управлякщим выходом блока управления.

Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для регенерации телеграфных посылок | 1985 |

|

SU1338080A2 |

| Устройство для приема биимпульсных сигналов | 1987 |

|

SU1471315A1 |

| Устройство для преобразования телеграфного кода в видеокод | 1985 |

|

SU1314461A1 |

| Устройство для приема трехкратно повторяемых команд управления | 1986 |

|

SU1385309A1 |

| Накопитель телеграфных кодовых комбинаций | 1974 |

|

SU557504A1 |

| ВОЛОКОННО-ОПТИЧЕСКАЯ СИСТЕМА С БЕЗОПАСНОЙ ПЕРЕДАЧЕЙ ИНФОРМАЦИИ | 1995 |

|

RU2100906C1 |

| ОПТОЭЛЕКТРОННОЕ УСТРОЙСТВО ДЛЯ ПЕРЕДАЧИ ДИСКРЕТНЫХ СИГНАЛОВ В ЛИНИЮ СВЯЗИ | 2006 |

|

RU2313914C1 |

| Электрочасовая система | 1984 |

|

SU1190352A1 |

| Цифровой веберметр | 1986 |

|

SU1368832A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА КОМАНД ТЕЛЕУПРАВЛЕНИЯ | 1991 |

|

RU2023309C1 |

Изобретение относится к электросвязи и м.б. использовано в системах телеграфной связи. Повышается точность и помехоустойчивость реге- , нерации телеграфных посыпок. Устр-во содержит интегратор t, компаратор напряжений 2, пороговый блок (ПБ) 3 ЦАП 4, источник опорного напряжения 5, счетчик импульсов 6, блок управления 7, два регистра сдвига (PC) 8и 16, два мажоритарных блока (МБ) 9и 17, два компаратора кодов 10 и 18, D-триггер 11,четьфе элемента И 12, 13, 14 и 15, элемент ИЛИ 19 и RS-триггер 20. После трех циклов анализа амплитуды входного сигнала л с KD со Uib СО vl

| Способ восстановления хромовой кислоты, в частности для получения хромовых квасцов | 1921 |

|

SU7A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Способ аналого-цифрового преобразования и устройство для его осуществления | 1978 |

|

SU741459A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1986-05-30—Публикация

1983-08-22—Подача