1

Изобретение относится к электросвязи и может использоваться в телеграфных системах связи.

Известен накопитель телеграфных кодовых комбинаций, содержащий последователь но соединенные логические элементы ввода комбинаций и блоки памяти, логические элементы вывода комбинаций, счетчики записи и считывания, а тактовую шину, подключенную к блокам памяти, при этом блоки памяти и блок управления выполнены на триггерах с раздельными входами, схемах совпадения.

Перезапись кодовых комбинаций с од- ной ступени накопления на другую свободную ступень осуществляется схемой, состоящей из схем совпадения и служебного триггера, посредством двух тактовых пос.ледовательностей iJ

Однако известный накопитель содержит больщое количество элементов, в частности статических триггеров, что обуславливает его низкую надежность.

Цель изобретения - повышение надежности за счет уменьшения количества элементов накопителя.

Для этого в накопитель телеграфных комбинаций, содержащий последовательно соединенные логические элементы ввода комбинаций и блоки памяти, логические элементы вывода комбинашки, счетчики записи и считывания, а также тактовую шину, подключенную к блокам памяти, введены элементы И, ИЛИ, НЕ, а блок памяти выполнен на регистрах сдвига, ко входам которых подключены соответственно Входы логических элементов вывода комбинаций, выходы регистров сдвига подключены к соответствующим входам, логических элементов ввода комбинаций, ко входу счетчика записи через элемент ИЛИ подключены тактовая шина и шина импульсов ввода кодовых комбинаций, а выходь соответствующих разрядов счетчика записи соединены с входами первого элемента И,

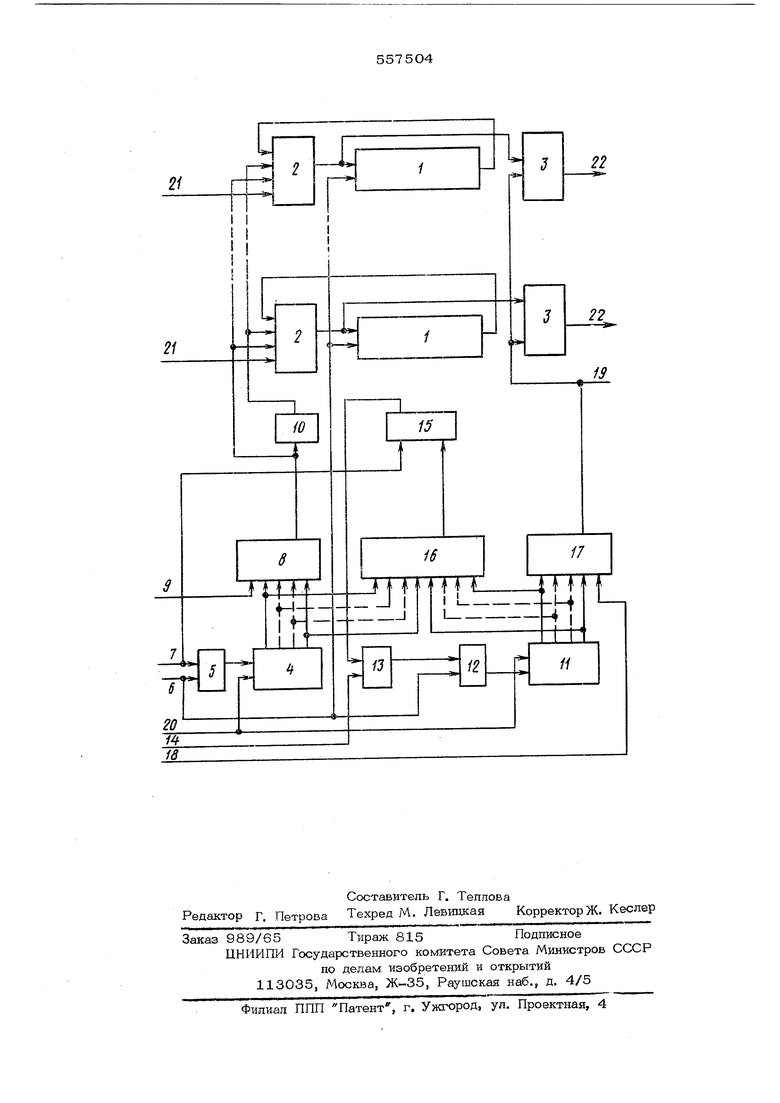

дополнительный вход которого соединен с шиной разрэщаниязаписи, авыход соединен непосредственно через элемент НЕ, ссответственно, со вторыми и третьими входами логических зпементов ввода ком- бтшахяй, вход счетчика считывания соецинеь через элемент ИЛИ с тактовой i-jrtjioft я выходом второго элемента И, один вход которого соединен с шиной вывода коцсг;Ых комбинаций, а второй вход соединен с выходом ipnrrepa, причем один вход триггера подключен к шине имлуль- сов ввода кодовых комбинахшй, а другойк выходу третьего элемента И, ко входам которого подключены соответствующие вы- .хо.аь счетчиков записи и считывания, вхоцы че1вертого элемента И подключены к вызсодам счетчика считывания и шине разрешения считывания, а выход подключе к дополнительным входам ло1 ичес;ких эяе- ме.ктов вывода кодовых комбинаций и шине CHJIXpOliMnynbCOB, Т-зкой накопитель выполняется на укруп иеннкх стандартных логических схемах, что дозволяет упростить его, улучшить об емно-васовые показатели, повысить надеж ыость и ум.еньшить число связей между отцельными его элементами. На чертеже изображена блок-схема пре лагаемого накопителя. Накопитель телеграфных кодовых комбинаций содержит блок памяти, выполненный 1;а регистрах 1 сдвига, ко входам которых подключены выходы логических &jiei fGHTOB 2 ввода комбинаций и входы ло гических элементов 3 вывода комбинаций, выходы регистров 1 подключены к соотве ствующим, входам логических элементов 2 счетчи ;: записи 4, ко входу которого чере элемент ИЛИ 5 подключена тактовая шина н шина 7 импульсов ввода кодовых комби ций, а выходы соответствующих разрядов счетчика записи 4 соединены со входами эпем.ента И 8, дополнительный вход которого соединен с шиной 9 разрешения записи, а выход которого соединен непосред ственно и через элемент НЕ 10 со вторыми и третьими входами логических .элементов 2, счетчик считывания 11, вход к торого соедш{ен через элемент ИЛИ 12 с тактовой шиной 6 и выходом второго эяемента И 13, один вход которого соединен с шиной 14 вывода кодовых комбинадий, а второй вход - с выходом, триггера 15, пр№1ем один вход триггера подключен к шине 7, а другой - к выходу третьего эл мента И 16, ко входам, которого подключены соответствующие выходы счетчиков 4 и 11, к выходам последнего подключены также входы четвертого эдеме.нта И 17J один вход которого подключен к шине 18разрешения считывания, а выход под кпючен к дополнительным входам логических ачементов 3 и шине 19 синхроимпульсов. К тактовой шине 6 подключены соответствуюшие входы регистров 1, соотгзетствующие входы счетчиков 4,11 соединены с шиной 20 начальной установки, входы логических элементов 2-е входными кодовыми шинами 21, выходы логических элементов 3 - с выходными кодовыми шинами 22. Предложенный накопитель работает следующим образом. В начальный момент им.пульсом, поданным по шине 20 происходит установка счетчиков 4 и 11 в нулевое состояние. На шину 6 подается тактовая последовательность. При этом счетчики 4 и 11 находятся в од шаковых (нулевых) фазовых состояниях. На выходе третьего элемента И 16 периодически появляется импульс, который вг лючает триггер 15, с выхода которого поступает запрет на второй элемент И 13. На кодовые шины 21 поступает кодовая комбинация , которую необ.ходим.о записать. После этого на шину 9 подается сигнал разрешения записи. В моменты времени, когда счетчик 4 находится в нулевом состоянии, на выходе элемента И 8 и на выходе элемента НЕ 10 появляются импупьсы, разрещающие запись кодовых комбинаций, посаупающих по шинам 21 в регистры 1 через логические элементы 2, и запрещающие прохождение хранящихся кодовых комбинаций с выходов регистров 1. По окончании сигнала разрешения записи на шину 7 поступает импульс ввода кодовых комбинаций, который смещает фазовое состояние счетчика 4 на единицу влево и сбрасывает триггер 15, с выхода которого поступает разрешение на элемент И 13. Процесс ввода кодовой комбинации закончен. Записашгая кодовая комбинация циркулирует в регистрах 1, Накопитель готов к приему следующей кодовой комбинации, ввод которой происходит аналогично. Работа накопителя в режиме выводе происходит следующим образом. па щину 18 nocTjaiaeT сигнал разреще.ния считывания. На выходе четвертого элемента И 17 появляются импульсы в моменты време.ни, соотве1х:твующие .нулевому состоянию счетчика 11. Импульсы с выхода элемента И 13 разрешают прохожде.ние первой кодовой комбинации через элементы 3 на выходные кодовые шины 22. По окончании сигнала разрешения считывания на шину 14 поступает импульс вывода кодовых комбинаций. Этот импульс смещает фазовое состояние счетчика 11 на

единицу влево и поступает на элемент ИЛИ 12 лишь при наличии разрешения с триггера 15, поступающего на вход второго элемента И 13. Это происходит лишь в том случае, когда счетчики 4 и Ц находятся в разных фазовых состояниях, т.е., когда накопитель не пуст. Схема готова к выводу следующей кодовой комбинации. Ввод и вывод может .происходить одновременно и с разными частотами.

Формула изобретения

Накопитель телеграфных кодовых комбинаций, содержащий последовательно соединенные логические элементы ввода комбинаций и блоки памяти, логические элементы вьюода комбинаций, счетчики записи и считывания, а также тактовую шину, подключенную к блокам памяти, отличающийся тем, 4TOj с целью повышения надежности за счет уменьшения количества элементов накопителя, в него введены элементы, И, ИЛИ, НЕ, а блок памяти выполнен на регистрах сдвига, ко входам которых подключены соответственно входы логических элементов вьшода комбинаций, выходы регистров сдвига подключены к еоотвествующим входам логических элементов ввода комбинаций, ко входу счетчика

записи через элемент ИЛИ подключены тактовая шина и щина импульсов ввода кодовых комбинаций, а выходы соответствующих разрядов счетчика записи соединены

с входами первого элемента И, дополнительный вход которого соединен с шиной разрешения записи, а выход которого соединен непосредственно и через элемент НЕ, соответственно , со вторыми и тре-

тьими входами логических элементов ввода комбинаций, вход счетчика считывания соединен через элемент ИЛИ с тактовой щиной и выходом, второго элемента И, один вход которого соединен с шиной

вывода кодовых комбинаций, а второй вход соединен с выходом триггера, причем один вход триггера подключен к шине импульсов ввода кодовых комби.наций, а другой - к выходу третьего эпемента И, ко входам которого подключены соответствующие выходы счетчиков записи и считывания, входы четвертого элемента И подключены к выходам счетчика считьшания и шине разрешения считывания;

а выход подключен к дополнительным входам логических элементов вывода кодовых комбинаций и шине синхроимпульсов.

Источники информанин, принятые во внимание при экспертизе :

1. Авт. свид. № 285040, И О4 В13/Са, приор. 05.05.69.

| название | год | авторы | номер документа |

|---|---|---|---|

| Буферное запоминающее устройство | 1977 |

|

SU720507A1 |

| Устройство управления для памяти на цилиндрических магнитных доменах | 1984 |

|

SU1265855A1 |

| Буферное запоминающее устройство | 1974 |

|

SU493805A1 |

| Устройство управления для доменной памяти | 1982 |

|

SU1075311A1 |

| Запоминающее устройство для телеграфного аппарата | 1986 |

|

SU1377911A1 |

| Устройство для регистрации телеграфных посылок | 1983 |

|

SU1234977A1 |

| Устройство приема и передачи дискретных сигналов | 1979 |

|

SU856031A1 |

| Электронное синхронное телеграфное устройство | 1978 |

|

SU860331A2 |

| Устройство для передачи и приема дискретных сигналов | 1981 |

|

SU1016848A1 |

| Устройство для централизованного контроля и оперативного управления | 1977 |

|

SU633029A1 |

Авторы

Даты

1977-05-05—Публикация

1974-06-21—Подача