Изобретение относитея к вычислительной технике и предназначено для использования в качестве системы программного управления группой металлообрабатывающих, раскладывающих жгуты и прочих станков.

Цель изобретения - повышение быстродействия системы и сокращение числа программ.

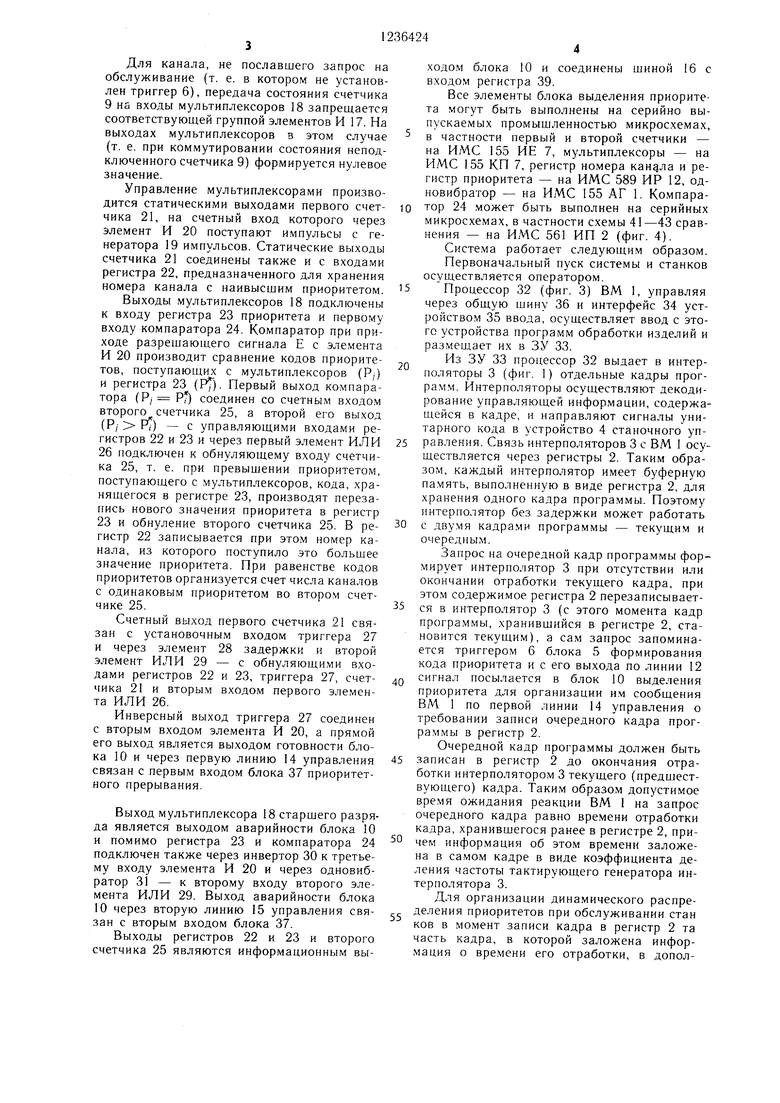

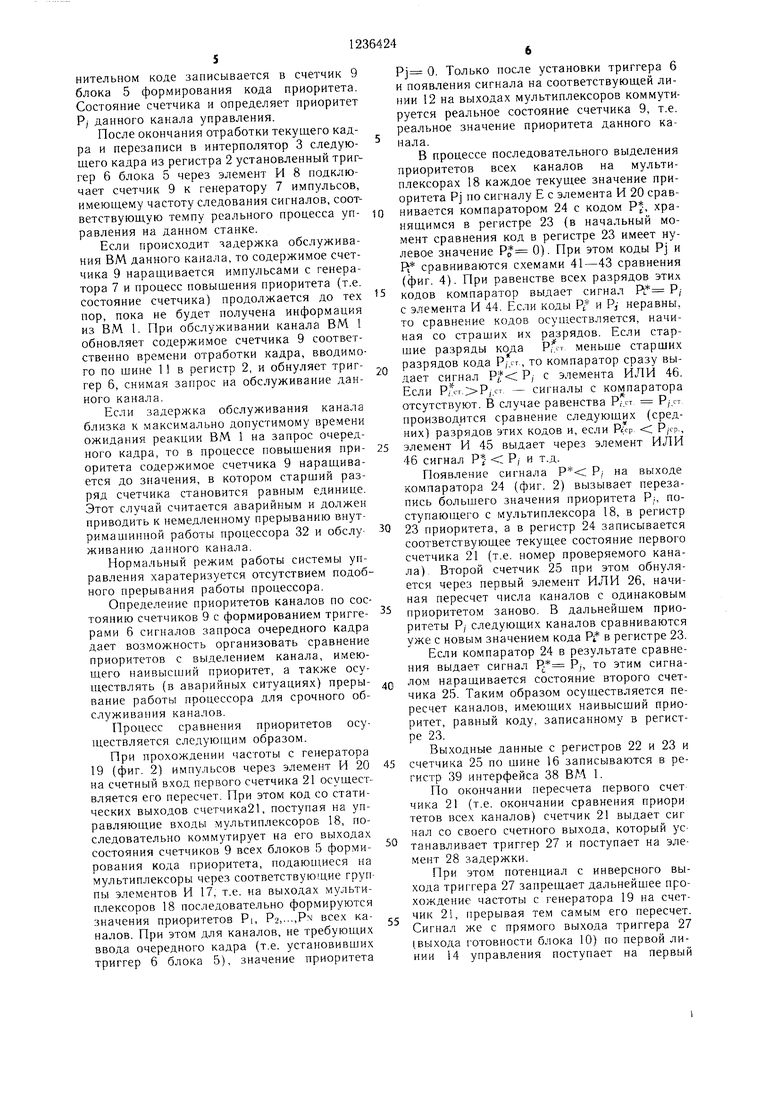

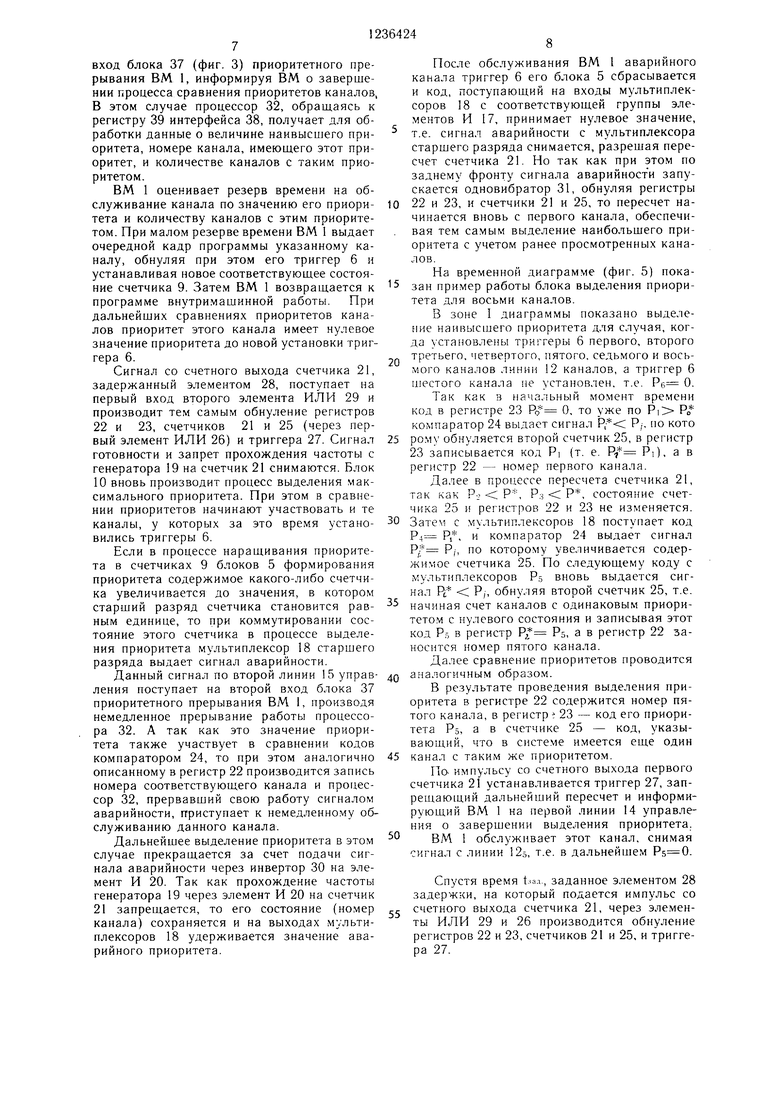

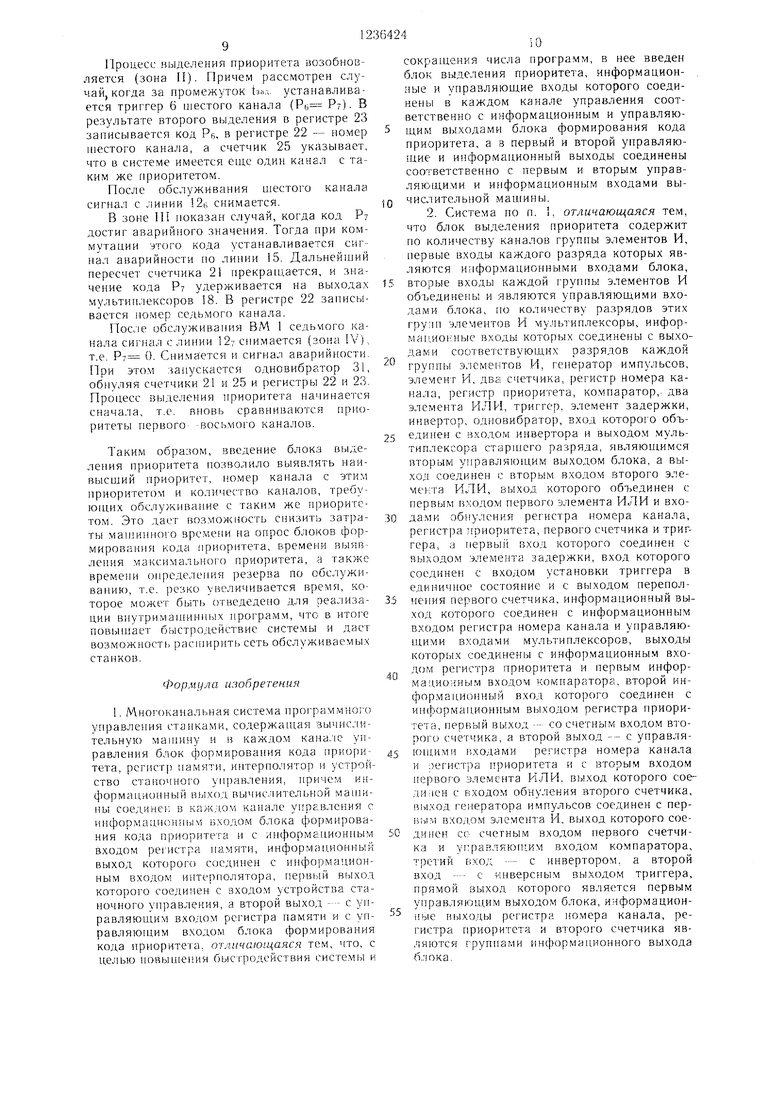

На фиг. представлена структурная схема многоканальной системы программного управления станками; на фиг. 2 - схема блока выделения приоритета; на фиг. 3 - функциональная схема вычислительной машины; на фиг. 4 - схема компаратора; на фиг. 5 - временная диаграмма работы блока выделения приоритета.

выходом -- с вторым входом регистра 2 памяти и установочным входом триггера 6 блока 5 формирования кода приоритета. Установка триггера 6 соответствует запросу на обслуживание данного канала. Блок 5

содержит также генератор 7 импульсов, через элемент И 8 подключенный к счетному входу счетчика 9. Второй вход элемента И 8 соединен с выходом триггера 6, связанного также линией 12 с соответствующим

10 входом разрешения приема информации блока 10 выделения приоритета. Статические выходы счетчиков 9 соединены шинами 13 с соответствующими информационными входами блока 10 выделения приоритета. Информационный выход блока 10 подключен

Многоканальная система программного щиной 16 к ВМ 1 (входам регистра 39 ин30

35

управления станками (фиг. 1) содержит вычислительную машину (ВМ) 1, регистр 2 па- .мяти, интерполятор 3, устройство 4 станочного управления, блок 5 формирования кода приоритета, содержащий триггер 6, генератор 7 импульсов, элемент И 8, счетчик 9, блок 10 выделения приоритета, информационную щину 11, линию 2 управления разрешением приема информации в блок выделения приоритета (12| - для первого канала, 12 - для N-ro канала), информа- 25 ционные шины 13 состояния счетчиков (13i - первого канала, 13 - N-ro канала), первую 14 и вторую 15 линии управления, информационную шину 16 блока выделения приоритета.

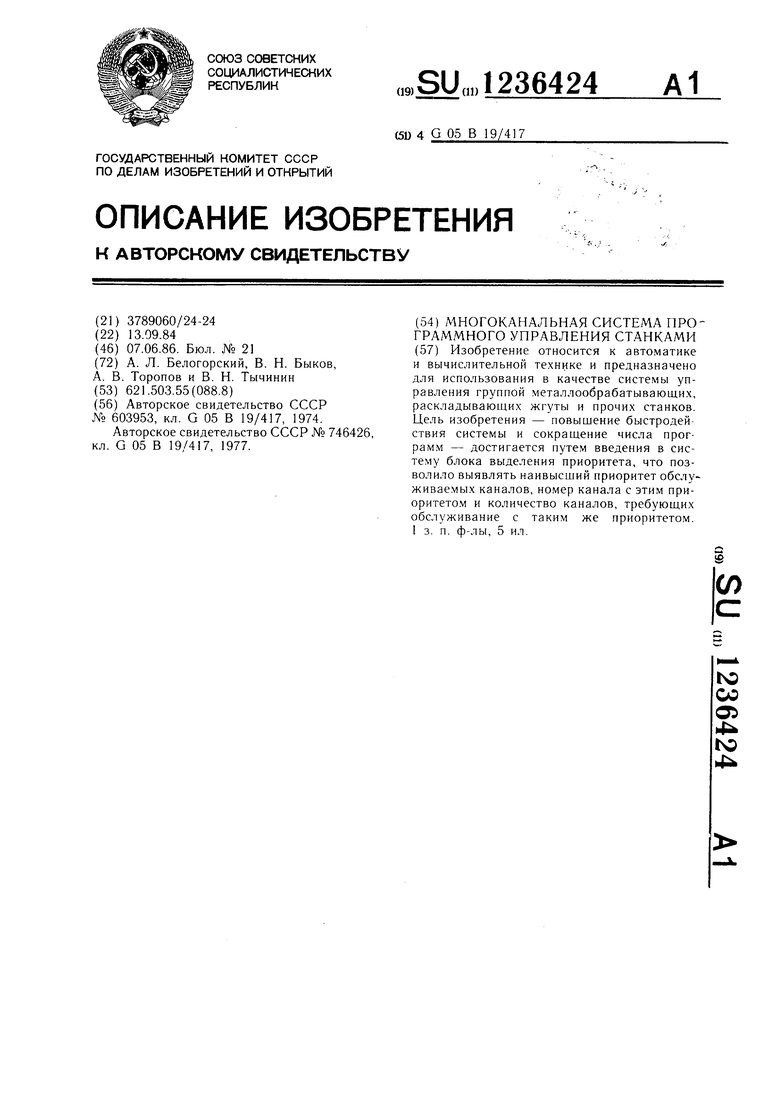

Блок 0 выделения приоритета (фиг. 2) содержит группы элементов И 17, мультиплексоры 18, генератор 19 импульсов, элемент И 20, первый счетчик 21, регистр 22 номера канала, регистр 23 приоритета, компаратор 24, второй счетчик 25, первый элемент ИЛИ 26, триггер 27, элемент 28 задержки, второй элемент ИЛИ 29, инвертор 30, одновибратор 31.

Вычислительная маошна (фиг. 3) содержит процессор 32, запоминающее устройство (ЗУ) 33, интерфейс 34 (устройство связи) с устройствами 35 ввода - вывода; общую шину 36 ВМ, блок 37 приоритетного прерывания, интерфейс 38 с внеишими каналами 11 и 16, содержащий регистры 39 и 40.

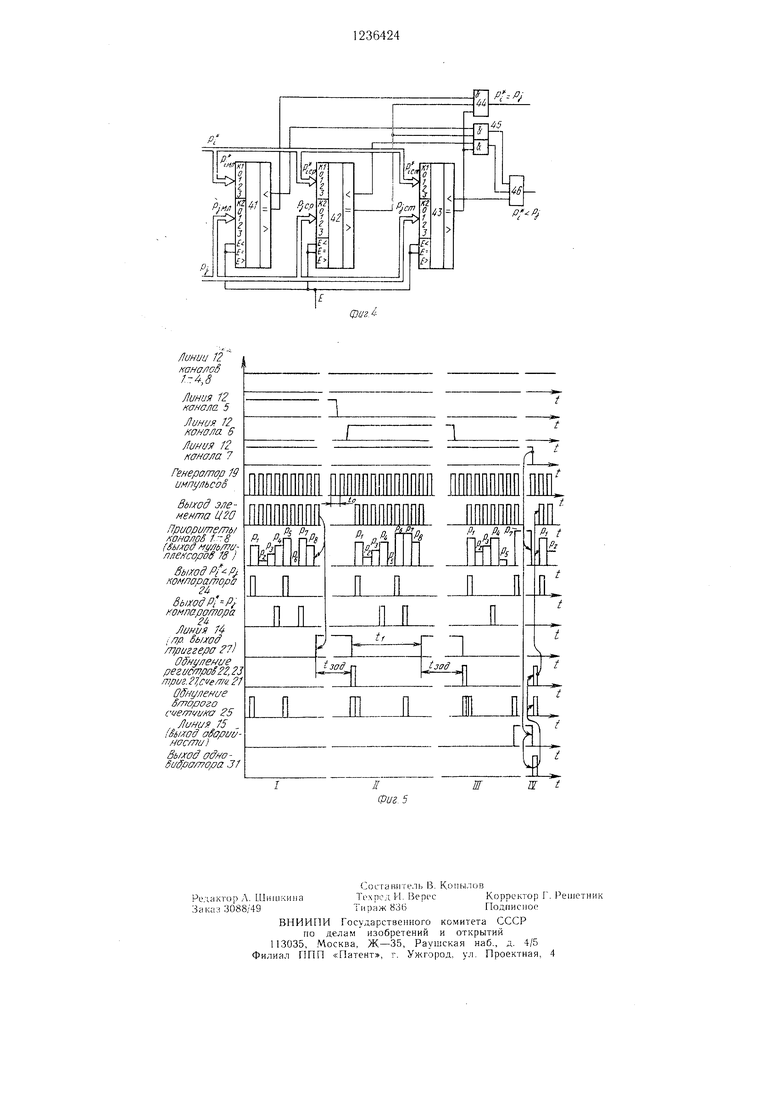

Компаратор 24 (фиг. 4) имеет схемы 41-- 43 сравнения, элементы И 44 и 45, элемент ИЛИ 46 (приведен пример для 12- разрядных кодов).

Информационный выход ВМ 1 (фиг. 1), т. е. выход регистра 40 интерфейса 38 (фиг. 3), через информационную шину 11 подключен к первым входам регистров 2 памяти, к установочным входам счетчиков 9 и к обнуляющим входам триггеров 6 всех каналов системы.

Выходы каждого регистра 2 соединены с входами интерполятора 3 этого же канала, связанного первым выходом со своим устройством 4 станочного управления, а вторым

терфейса 38).

Выход готовности и выход аварийности блока 10 выделения приоритета соединены соответственно первой 14 и второй 15 линия- 2Q ми управления с управляющими входами ВМ 1 (первым и вторым входами блока 37 приоритетного прерывания).

Для упрощ,ения блока 10 предлагаемой системы счетчик 9 блоков 5 формирования кода приоритета выполнен не вычитающим (как в известном устройстве), а суммирующим. Такое решение на выявление приоритета каналов совершенно не сказывается, только ВМ производит оценку значения приоритета, исхотя из того, что наивысшему приоритету соответствует максимальное заполнение счетчика 9, а не его нулевое состояние.

Все элементы данной системы могут быть выполнены на серийно выпускаемых промышленностью микросхемах (ИМС), например ИМС 155 и 589 серии, в частности регистры 2, 39 и 40 -- на ИМС 589 ИР 12; блок 37 приоритетного прерывания - на ИМС 589 ИК 15; счетчик 9 - на ИМС 155 ИЕ 7.

Блок 10 выделения приоритета служит для выделения наивысшего приоритета, определения номера канала и количества каналов с этим приоритетом.

Блок 10 содержит по количеству каналов группы элементов И 17 (фиг. 2), первые входы которых являются информационными входами блока 10 и связаны шинами 13 с выходами счетчиков 9. Вторые входы элементов в каждой группе объединены и являются входами разрешения приема информации в блок 10. Эти входы соединяются с выходом соответствующих триггеров 6 блоков 5.

40

45

50

35

Выходы групп элементов И 17 подключены к входам мультиплексоров 18, причем одноименные разряды этих групп собираются на отдельных мультиплексорах. Таким образом мультиплексоры 18 в зависимости от кода на своих управляюп.1их входах коммутируют на своих выходах состояние Р/ того или иного счетчика 9 блоков 5.

выходом -- с вторым входом регистра 2 памяти и установочным входом триггера 6 блока 5 формирования кода приоритета. Установка триггера 6 соответствует запросу на обслуживание данного канала. Блок 5

содержит также генератор 7 импульсов, через элемент И 8 подключенный к счетному входу счетчика 9. Второй вход элемента И 8 соединен с выходом триггера 6, связанного также линией 12 с соответствующим

0 входом разрешения приема информации блока 10 выделения приоритета. Статические выходы счетчиков 9 соединены шинами 13 с соответствующими информационными входами блока 10 выделения приоритета. Информационный выход блока 10 подключен

щиной 16 к ВМ 1 (входам регистра 39 ин щиной 16 к ВМ 1 (входам регистра 39 ин0

5

5

терфейса 38).

Выход готовности и выход аварийности блока 10 выделения приоритета соединены соответственно первой 14 и второй 15 линия- Q ми управления с управляющими входами ВМ 1 (первым и вторым входами блока 37 приоритетного прерывания).

Для упрощ,ения блока 10 предлагаемой системы счетчик 9 блоков 5 формирования кода приоритета выполнен не вычитающим (как в известном устройстве), а суммирующим. Такое решение на выявление приоритета каналов совершенно не сказывается, только ВМ производит оценку значения приоритета, исхотя из того, что наивысшему приоритету соответствует максимальное заполнение счетчика 9, а не его нулевое состояние.

Все элементы данной системы могут быть выполнены на серийно выпускаемых промышленностью микросхемах (ИМС), например ИМС 155 и 589 серии, в частности регистры 2, 39 и 40 -- на ИМС 589 ИР 12; блок 37 приоритетного прерывания - на ИМС 589 ИК 15; счетчик 9 - на ИМС 155 ИЕ 7.

Блок 10 выделения приоритета служит для выделения наивысшего приоритета, определения номера канала и количества каналов с этим приоритетом.

Блок 10 содержит по количеству каналов группы элементов И 17 (фиг. 2), первые входы которых являются информационными входами блока 10 и связаны шинами 13 с выходами счетчиков 9. Вторые входы элементов в каждой группе объединены и являются входами разрешения приема информации в блок 10. Эти входы соединяются с выходом соответствующих триггеров 6 блоков 5.

0

5

0

Выходы групп элементов И 17 подключены к входам мультиплексоров 18, причем одноименные разряды этих групп собираются на отдельных мультиплексорах. Таким образом мультиплексоры 18 в зависимости от кода на своих управляюп.1их входах коммутируют на своих выходах состояние Р/ того или иного счетчика 9 блоков 5.

Для канала, не пославшего запрос на обслуживание {т. е. в котором не установлен триггер 6), передача состояния счетчика

9на входы мультиплексоров 18 запрещается соответствующей группой элементов И 17. На выходах мультиплексоров в этом случае (т. е. при коммутировании состояния неподключенного счетчика 9) формируется нулевое значение.

Управление мультиплексорами производится статическими выходами первого счетчика 21, на счетный вход которого через элемент И 20 поступают импульсы с генератора 19 импульсов. Статические выходы счетчика 21 соединены также и с входами регистра 22, предназначенного для хранения номера канала с наивысшим приоритетом.

Выходы мультиплексоров 18 подключены к входу регистра 23 приоритета и первому входу компаратора 24. Компаратор при приходе разрешающего сигнала Е с элемента И 20 производит сравнение кодов приоритетов, поступающих с мультиплексоров (Р/) и регистра 23 (Pf). Первый выход компаратора (Р/ Pf) соединен со счетным входом второго счетчика 25, а второй его выход (Р/ Pi) - с управляющими входами регистров 22 и 23 и через первый элемент ИЛИ 26 подключен к обнуляющему входу счетчика 25, т. е. при превышении приоритетом, поступающего с мультиплексоров, кода, хранящегося в регистре 23, производят перезапись нового значения приоритета в регистр 23 и обнуление второго счетчика 25. В регистр 22 записывается при этом номер канала, из которого поступило это большее значение приоритета. При равенстве кодов приоритетов организуется счет числа каналов с одинаковым приоритетом во втором счетчике 25.

Счетный выход первого счетчика 21 связан с установочным входом триггера 27 и через эле.мент 28 задержки и второй элемент ИЛИ 29 - с обнуляющими входами регистров 22 и 23, триггера 27, счетчика 21 и вторым входом первого элемента ИЛИ 26.

Инверсный выход триггера 27 соединен с вторым входом элемента И 20, а прямой его выход является выходом готовности блока 10 и через первую линию 14 управления связан с первым входом блока 37 приоритетного прерывания.

Выход мультиплексора 18 старшего разряда является выходом аварийности блока 10 и помимо регистра 23 и компаратора 24 подключен также через инвертор 30 к третьему входу элемента И 20 и через одновиб- ратор 31 - к второму входу второго элемента ИЛИ 29. Выход аварийности блока

10через вторую линию 15 управления связан с вторым входом блока 37.

Выходы регистров 22 и 23 и второго счетчика 25 являются информационным вы0

5

0

5

0

0

5

0

5

ХОДОМ блока 10 и соединены шиной 16 с входом регистра 39.

Все элементы блока выделения приоритета могут быть выполнены на серийно выпускаемых промышленностью микросхемах, в частности первый и второй счетчики - на ИМС 155 ИЕ 7, мультиплексоры - на ИМС 155 КП 7, регистр номера канала и регистр приоритета - на ИМС 589 ИР 12, од- новибратор - на ИМС 155 АГ 1. Компаратор 24 может быть выполнен на серийных микросхемах, в частности схемы 41-43 сравнения - на ИМС 561 ИП 2 (фиг. 4).

Система работает следующим образом.

Первоначальный пуск системы и станков осуществляется оператором.

Процессор 32 (фиг. 3) ВМ 1, управляя через общую шину 36 и интерфейс 34 устройством 35 ввода, осуществляет ввод с этого устройства программ обработки изделий и размещает их в ЗУ 33.

Из ЗУ 33 процессор 32 выдает в интерполяторы 3 (фиг. 1) отдельные кадры программ. Интерполяторы осуществляют декодирование управляющей информации, содержащейся в кадре, и направляют сигналы унитарного кода в устройство 4 станочного управления. Связь интерполяторов 3 с ВМ 1 осуществляется через регистры 2. Таким образом, каждый интерполятор имеет буферную память, выполненную в виде регистра 2, для хранения одного кадра программы. Поэтому интерполятор без задержки может работать с двумя кадра.ми программы - текущим и очередным.

Запрос на очередной кадр программы формирует интерполятор 3 при отсутствии или окончании отработки текущего кадра, при это.м содержимое регистра 2 перезаписывается в интерполятор 3 (с этого момента кадр программы, хранившийся в регистре 2, становится текущим), а сам запрос запоминается триггером 6 блока 5 формирования кода приоритета и с его выхода по линии 12 сигнал посылается в блок 10 выделения приоритета для организации им сообщения ВМ 1 по первой линии 14 управления о требовании записи очередного кадра программы в регистр 2.

Очередной кадр программы должен быть записан в регистр 2 до окончания отработки интерполятором 3 текущего (предшествующего) кадра. Таким образом допустимое время ожидания реакции ВМ 1 на запрос очередного кадра равно времени отработки кадра, хранившегося ранее в регистре 2, причем информация об этом времени заложена в са.мом кадре в виде коэффициента деления частоты тактирующего генератора интерполятора 3.

Для организации динамического распределения приоритетов при обслуживании стан ков в момент записи кадра в регистр 2 та часть кадра, в которой заложена информация о времени его отработки, в допол15

нительном коде записывается в счетчик 9 блока 5 формирования кода приоритета. Состояние счетчика и определяет приоритет Р,- данного канала управления.

После окончания отработки текущего кадра и перезаписи в интерполятор 3 следую- щего кадра из регистра 2 установленный триггер 6 блока 5 через эле.здент И 8 подключает счетчик 9 к генератору 7 импульсов, имеющему частоту следования сигналов, соответствующую темпу реального процесса уп- ю равления на данном станке.

Если происходит задержка обслуживания ВМ данного канала, то содержимое счетчика 9 наращивается импульсами с генератора 7 и процесс повыщения приоритета (т.е. состояние счетчика) продолжается до тех пор, пока не будет получена информация из ВМ 1. При обслуживании канала ВМ 1 обновляет содержимое счетчика 9 соответственно времени отработки кадра, вводимого по шине 11 в регистр 2, и обнуляет триг- -,„ гер 6, снимая запрос на обслуживание данного канала.

Если задержка обслуживания канала близка к максимально допустимому времени ожидания реакции ВМ 1 на запрос очередного кадра, то в процессе повышения при- 25 оритета содержимое счетчика 9 наращивается до значения, в котором старший разряд счетчика становится равным единице. Этот случай считается аварийным и должен приводить к немедленному прерыванию внут- римашинной работы процессора 32 и обслу- ЭО живанию да1шого канала.

Нормальный режим работы системы управления харатеризуется отсутствием подобного прерывания работы процессора.

Определение приоритетов каналов но сосPj 0. Только после установки триггера 6 и появления сигнала на соответствующей линии 12 на выходах мультиплексоров коммути руется реальное состояние счетчика 9, т.е. реальное значение приоритета данного канала.

В процессе последовательного выделения приоритетов всех каналов на мультиплексорах 18 каждое текущее значение приоритета Pj по сигналу Е с элемента И 20 сравнивается компаратором 24 с кодом Р:, хранящимся в регистре 23 (в начальный момент сравнения код в регистре 23 имеет нулевое значение Р 0). При этом коды Pj и R сравниваются схемами 41-43 сравнения (фиг. 4). При равенстве всех разрядов этих кодов компаратор выдает сигнал PL Р/ с элемента И 44. Если коды Pf и PJ неравны, то сравнение кодов осуществляется, начиная со страших их разрядов. Если старшие разряды меньше старших разрядов кода Р/,ст,, то компаратор сразу выдает сигнал Р;. Р/ с элемента ИЛИ 46. Если P,T.Pj,cT, - сигналы с компаратора отсутствуют. В случае равенства : Р,-,ст производится сравнение следующих (средних) разрядов этих кодов и, если РЛ-р, ; Р,тр., элемент И 45 выдает через элемент ИЛИ 46 сигнал Р ; Р, и т.д.

Появ.аение сигнала Р/ на выходе компаратора 24 (фиг. 2) вызывает перезапись большего значения приоритета Р;, поступающего с мультиплексора 18, в регистр 23 приоритета, а в регистр 24 записывается соответствующее текущее состояние первого счетчика 21 (т.е. номер проверяемого канала). Второй счетчик 25 при этом обнуляется через первый элемент ИЛИ 26, начиная пересчет числа каналов с одинаковым

тоянию счетчиков 9 с формированием тригге- приоритетом заново. В дальнейщем приорами 6 сигналов запроса очередного кадраритеты Р/ следующих каналов сравниваются дает возможность организовать сравнениеуже с новым значением кода Pi в регистре 23. приоритетов с выделением канала, имею-Если компаратор 24 в результате сравне- щего нaивыcцJИЙ приоритет, а также осу-ния выдает сигнал 1 PJ, то этим сигна- ществлять (в аварийных ситуациях) преры- Q лом наращивается состояние второго счетвание работы процессора для срочного обслуживания каналов.

Процесс сравнения приоритетов осуществляется следующим образом.

При прохождении частоты с генератора 19 (фиг. 2) импульсов через элемент И 20 на счетный вход первого счетчика 21 осуществляется его пересчет. При этом код со статических выходов счетчика21, поступая на управляющие входы мультиплексоров 18, последовательно коммутирует на его выходах состояния счетчиков 9 всех блоков 5 формирования кода приоритета, подающиеся на мультиплексоры через соответствующие группы элементов И 17, т.е. на выходах мультиплексоров 18 последовательно формируются значения приоритетов PI, P2,..., всех каналов. При этом для каналов, не требующих ввода очередного кадра (т.е. установивщих триггер 6 блока 5), значение приоритета

чика 25. Таким образом осуществляется пересчет каналов, имеющих наивысший приоритет, равный коду, записанному в регистре 23.

Выходные данные с регистров 22 и 23 и

45 счетчика 25 по шине 16 записываются в регистр 39 интерфейса 38 ВМ 1.

По окончании пересчета первого счет чика 21 (т.е. окончании сравнения приори тетов всех каналов) счетчик 2 выдает сиг нал со своего счетного выхода, который ус танавливает триггер 27 и поступает на элемент 28 задержки.

При этом потенциал с инверсного выхода триггера 27 запрещает дальнейшее прохождение частоты с генератора 19 на счетд, чик 21, прерывая тем самым его пересчет. Сигнал же с прямого выхода триггера 27 (выхода готовности блока 10) по первой линии 14 управления поступает на первый

5

„

5 О

Pj 0. Только после установки триггера 6 и появления сигнала на соответствующей линии 12 на выходах мультиплексоров коммутируется реальное состояние счетчика 9, т.е. реальное значение приоритета данного канала.

В процессе последовательного выделения приоритетов всех каналов на мультиплексорах 18 каждое текущее значение приоритета Pj по сигналу Е с элемента И 20 сравнивается компаратором 24 с кодом Р:, хранящимся в регистре 23 (в начальный момент сравнения код в регистре 23 имеет нулевое значение Р 0). При этом коды Pj и R сравниваются схемами 41-43 сравнения (фиг. 4). При равенстве всех разрядов этих кодов компаратор выдает сигнал PL Р/ с элемента И 44. Если коды Pf и PJ неравны, то сравнение кодов осуществляется, начиная со страших их разрядов. Если старшие разряды меньше старших разрядов кода Р/,ст,, то компаратор сразу выдает сигнал Р;. Р/ с элемента ИЛИ 46. Если P,T.Pj,cT, - сигналы с компаратора отсутствуют. В случае равенства : Р,-,ст производится сравнение следующих (средних) разрядов этих кодов и, если РЛ-р, ; Р,тр., элемент И 45 выдает через элемент ИЛИ 46 сигнал Р ; Р, и т.д.

Появ.аение сигнала Р/ на выходе компаратора 24 (фиг. 2) вызывает перезапись большего значения приоритета Р;, поступающего с мультиплексора 18, в регистр 23 приоритета, а в регистр 24 записывается соответствующее текущее состояние первого счетчика 21 (т.е. номер проверяемого канала). Второй счетчик 25 при этом обнуляется через первый элемент ИЛИ 26, начиная пересчет числа каналов с одинаковым

приоритетом заново. В дальнейщем приоритеты Р/ следующих каналов сравниваются уже с новым значением кода Pi в регистре 23. Если компаратор 24 в результате сравне- ния выдает сигнал 1 PJ, то этим сигна- Q лом наращивается состояние второго счетприоритетом заново. В дальнейщем приоритеты Р/ следующих каналов сравниваются уже с новым значением кода Pi в регистре 23. Если компаратор 24 в результате сравне- ния выдает сигнал 1 PJ, то этим сигна- лом наращивается состояние второго счетчика 25. Таким образом осуществляется пересчет каналов, имеющих наивысший приоритет, равный коду, записанному в регистре 23.

Выходные данные с регистров 22 и 23 и

счетчика 25 по шине 16 записываются в регистр 39 интерфейса 38 ВМ 1.

По окончании пересчета первого счет чика 21 (т.е. окончании сравнения приори тетов всех каналов) счетчик 2 выдает сиг нал со своего счетного выхода, который устанавливает триггер 27 и поступает на элемент 28 задержки.

При этом потенциал с инверсного выхода триггера 27 запрещает дальнейшее прохождение частоты с генератора 19 на счетчик 21, прерывая тем самым его пересчет. Сигнал же с прямого выхода триггера 27 (выхода готовности блока 10) по первой линии 14 управления поступает на первый

вход блока 37 (фиг. 3) приоритетного прерывания ВМ 1, информируя ВМ о завершении процесса сравнения приоритетов каналов, В этом случае процессор 32, обращаясь к регистру 39 интерфейса 38, получает для обработки данные о величине наивысшего при- оритета, номере канала, имеющего этот приоритет, и количестве каналов с таким приоритетом.

ВМ 1 оценивает резерв времени на обслуживание канала по значению его приори- 10 тета и количеству каналов с этим приоритетом. При малом резерве времени ВМ 1 выдает очередной кадр программы указанному каналу, обнуляя при этом его триггер 6 и устанавливая новое соответствующее состояПосле обслуживания ВМ 1 аварийного канала триггер 6 его блока 5 сбрасывается и код, поступающий на входы мультиплексоров 18 с соответствующей группы элементов И 17, принимает нулевое значение, т.е. сигнал аварийности с мультиплексора старшего разряда снимается, разрешая пересчет счетчика 21. Но так как при этом по заднему фронту сигнала аварийност и запускается одновибратор 31, обнуляя регистры 22 и 23, и счетчики 21 и 25, то пересчет начинается вновь с первого канала, обеспечивая тем самым выделение наибольшего приоритета с учетом ранее просмотренных каналов.

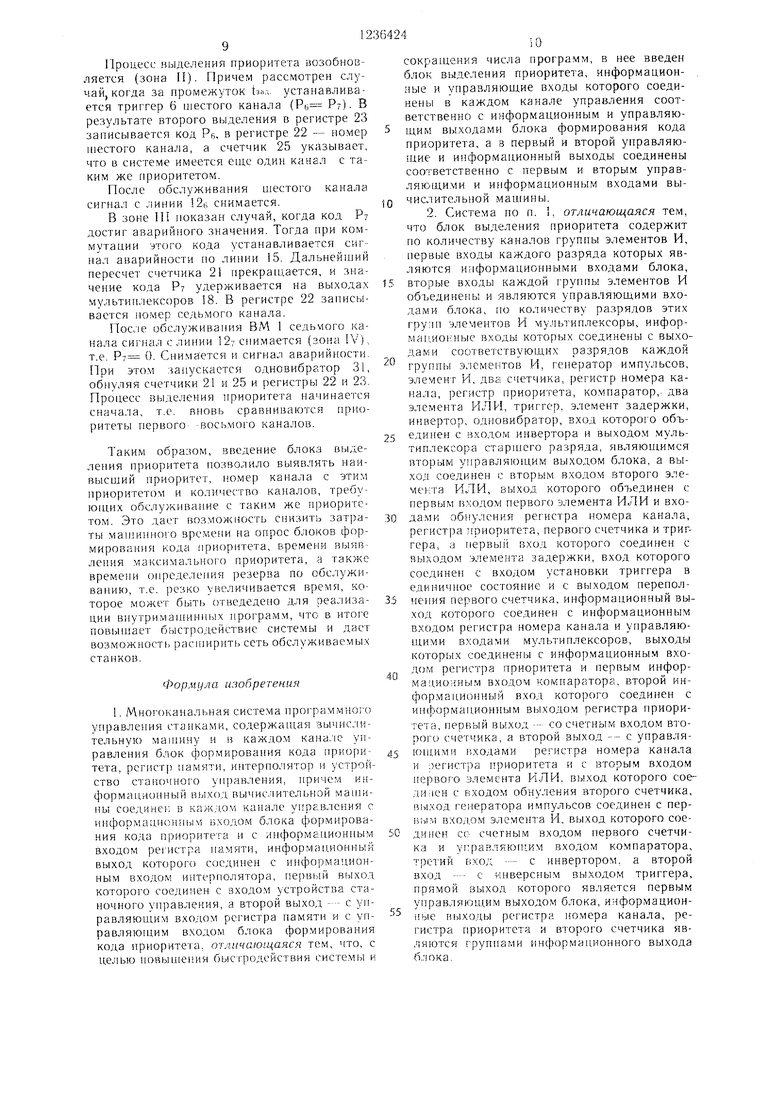

На временной диаграмме (фиг. 5) покание счетчика 9. Затем ВМ 1 возвращается к зан пример работы блока выделения приоритета для восьми каналов.

В зоне I диаграммы показано выделе- fine наивысшего приоритета для случая, когда установлены триггеры 6 первого, второго 2Q третьего, четрзертого, пятого, седьмого и восьмого каналов линии 12 каналов, а триггер 6 шестого канала не установлен, т.е. Рб 0.

Так как в начальный момент времени код в регистре 23 Rj О, то уже по Р: Ро компаратор 24 выдает сигнал ,- Р/. по кото

программе внутримащинной работы. При дальнейщих сравнениях приоритетов каналов приоритет этого канала имеет нулевое значение приоритета до новой установки триггера 6.

Сигнал со счетного выхода счетчика 21, задержанньЕЙ элементом 28, поступает на первый вход второго элемента ИЛИ 29 и производит тем самым обнуление регистров 22 и 23, счетчиков 21 и 25 (через первый элемент ИЛИ 26) и триггера 27. Сигнал 23 рому обнуляется второй счетчик 25, в регистр готовности и запрет прохождения частоты с23 записывается код P| (т. е. Р, PI), а в

генератора 19 на счетчик 21 снимаются. Блокрегистр 22 - номер первого канала.

Далее в процессе пересчета счетчика 21,

10 вновь производит процесс выделения максимального приоритета. При этом в сравнении приоритетов начинают участвовать и те

так как Р- , РЗ Р, состояние счетчика 25 и регистров 22 и 23 не изменяется.

каналы, у которых за это время устано- 30 Затем с мультиплексоров 18 поступает код вились триггеры 6.Р4- Р,, и компаратор 24 выдает сигнал

Если в процессе наращивания приоритета в счетчиках 9 6vTOKOB 5 формирования приоритета содержимое какого-либо счетчика увеличивается до значения, в котором старший разряд счетчика становится равным единице, то при коммутировании состояние этого счетчика в процессе выделения приоритета мультиплексор 18 старшего разряда выдает сигнал аварийности.

Данный сигнал по второй линии 15 управ- о аналогичным образом, ления поступает на второй вход блока 37В результате проведения выделения при35

Р, Р,, по которому увеличивается содержимое счетчика 25. По следующему коду с мультиплексоров PS вновь выдается сигнал Pt PI, обнуляя второй счетчик 25, т.е. начиная счет каналов с одинаковым приоритетом с нулевого состояния и записывая этот код PS в регистр Р Ра, а в регистр 22 заносится номер пятого канала.

Далее сравнение приоритетов проводится

приоритетного прерывания ВМ 1, производя немедленное прерывание работы процессора 32. А так как это значение приоритета также участвует в сравнении кодов компаратором 24, то при этом аналогично 45 описанному в регистр 22 производится запись номера соответствующего канала и процессор 32, прервавщий свою работу сигналом аварийности, п риступает к немедленному обслуживанию данного канала.

Дальнейшее выделение приоритета в этом случае прекращается за счет подачи сигнала аварийности через инвертор 30 на элемент И 20. Так как прохождение частоты

50

оритета в регистре 22 содержится номер пятого канала, в регистр t 23 - код его приоритета РЗ, а в счетчике 25 - код, указывающий, что в системе имеется еще один канал с таким же приоритетом.

По импульсу со счетного выхода первого счетчика 21 устанавливается триггер 27, запрещающий дальнейший пересчет и информирующий ВМ 1 на первой линии 14 управления о завершении выделения приоритета.

ВМ 1 обслуживает этот канал, снимая сигнал с линии 12.,, т.е. в дальнейшем .

Спустя время 1,ад., заданное элементом 28 зад.ержки, на который подается импульс со

21 запрещается, то его состояние (номер с счетного выхода счетчика 21, через элемен- канала) сохраняется и на выходах мульти-ты ИЛИ 29 и 26 производится обнуление

генератора 19 через элемент И 20 на счетчик

плексоров 18 удерживается значение аварийного приоритета.

регистров 22 и 23, счетчиков 21 и 25, и триггера 27.

После обслуживания ВМ 1 аварийного канала триггер 6 его блока 5 сбрасывается и код, поступающий на входы мультиплексоров 18 с соответствующей группы элементов И 17, принимает нулевое значение, т.е. сигнал аварийности с мультиплексора старшего разряда снимается, разрешая пересчет счетчика 21. Но так как при этом по заднему фронту сигнала аварийност и запускается одновибратор 31, обнуляя регистры 22 и 23, и счетчики 21 и 25, то пересчет начинается вновь с первого канала, обеспечивая тем самым выделение наибольшего приоритета с учетом ранее просмотренных каналов.

На временной диаграмме (фиг. 5) показан пример работы блока выделения приоритета для восьми каналов.

так как Р- , РЗ Р, состояние счетЗатем с мультиплексоров 18 поступает код Р4- Р,, и компаратор 24 выдает сигнал

Р, Р,, по которому увеличивается содержимое счетчика 25. По следующему коду с мультиплексоров PS вновь выдается сигнал Pt PI, обнуляя второй счетчик 25, т.е. начиная счет каналов с одинаковым приоритетом с нулевого состояния и записывая этот код PS в регистр Р Ра, а в регистр 22 заносится номер пятого канала.

Далее сравнение приоритетов проводится

аналогичным образом, В результате проведения выделения при

оритета в регистре 22 содержится номер пятого канала, в регистр t 23 - код его приоритета РЗ, а в счетчике 25 - код, указывающий, что в системе имеется еще один канал с таким же приоритетом.

По импульсу со счетного выхода первого счетчика 21 устанавливается триггер 27, запрещающий дальнейший пересчет и информирующий ВМ 1 на первой линии 14 управления о завершении выделения приоритета.

ВМ 1 обслуживает этот канал, снимая сигнал с линии 12.,, т.е. в дальнейшем .

регистров 22 и 23, счетчиков 21 и 25, и триггера 27.

Процесс выделения приоритета возобновляется (зона II). Причем рассмотрен случай когда за промежуток 1зад. устанавливается триггер 6 шестого канала (Рб Рт). В результате второго выделения в регистре 23 записывается код Рб, в регистре 22 - номер шестого канала, а счетчик 25 указывает, что в системе имеется еще один канал с таким же приоритетом.

После обслуживания шестого канала сигнал с линии 12б снимается.

В зоне 111 показан случай, когда код Р достиг аварийного значения. Тогда при коммутации этого кода устанавливается сигнал аварийности но линии 5. ДальнеЙ1ний пересчет счетчика 21 прекращается, и значение кода РТ удерживается на выхода.х мультиплексоров 18. В регистре 22 запись)- вается номер седьмого канала.

После обслуживания ВМ 1 седьмого канала сигнал с линии 127 снимается (зона IV)-, т.е. Р7 0. Снимается и сигнал аварийности. При этом запускается одновибратор 31, обнуляя счетчики 21 и 25 и регистры 22 и 23. Процесс выделения приоритета начинается сначала, т.е. вновь сравниваются приоритеты первого вось.мого каналов.

Таким образом, зведение блока выделения приоритета позволило выявлять наивысший приоритет, номер капала с этим приоритетом и количество каналов, требующих обслуживание с таким же приоритетом. Это дает возможность снизить затраты ма1пипно1 о на огфос блоков формирования кода приоритета, времени выявления .максимального приоритета, а также времени определения резерва по обслуживанию, т.е. резко увеличивается время, которое может быть отведедено для реа;1иза- ции внутримаП1ИНПЫХ программ, что в итоге повышает быстродействие системы и дает возможность расширить сеть обслуживаемы.х станков.

Формула изобретения

1. Многоканаль |ая система пр01 раммногс) управления станками, содержан1.ая зычис.- тельную ма1нину и в каждом кана.ле управления блок формирования кода приоритета, perncTf) памяти, иптерполятор и устройство ста1- очного управления, нричем информационный вы.ход вЕ)1числительной машины соел, в кажд.ом канале унревлепия с ипформац.ионпым ьходо.м блока формирования кода приоритета и с ипформапионпым входом решстра памяти, информационный выход которого соединен с информационным входом интерполятора, пе)вый выход которого соединен с зходо.м устройства станочного управления, а второй выход - - с управляющим входом регистра памяти и с управляющим входом блока фор.мирования кода приоритета, отличающаяся тем, что, с целью новыше1 ия быстродействия системы и

сокр.ашения числа программ, в нее введен блок выделения приоритета, информационные и управляющие входы которого соединены в каждом канале управления соответственно с информационным и управляющим выходами блока формирования кода приоритета, а в первый и второй управляю- па,ие и информационный выходы соединены соответственно с первым и вторым управляющими и ипформационным входами вычислительной машины.

2. Система по п. I, отличающаяся тем, что блок выделения приоритета содержит но количеству каналов группы элементов И, первые входы каждого разряда которых являются информационными входами блока,

5 вторые входы каждой группы элементов И объединены и являются управляюш,ими входами блока, по количеству разрядов этих групп элемент(зв И мультиплексоры, инфор- мацион:ные входы которых соединены с выходами соответствующих разрядов каждой группы элеме1-1тов И, генератор импульсов, элемент И, два счетчика, регистр номера капала, регистр приоритета, компаратор,, два элемента ИЛИ, триггер, элемент задержки, и вертор, одновибратор, вход которог о объ--; единен с вхо.аом инвертора и выходом мультиплексора старшего разряда, являюпщмся вторым управляющим выходом блока, а выход соединен с вторым входом второго эле- ме)гга ИЛИ, выход которого объединен с первым входом первого элемента ИЛИ и вхо0 обнуления регистра номера канала, регистра ггриоритета, первого счетчика и триг- гера, а первый вход которого соединен с выходом элемента задержки, вход которого соединен с входом установки триггера в единичное состояние и с выходом перепол:5 непия первого счетчика, информационный выход которого соединен с информационным входом регистра номера канала и унравляю- щими входами мультиплексоров, выходы которых соединены с информационным вхо,. дом регистра приоритета и первым инфор- ма:1,ионным входом компаратора, второй информационный вход которого соединен с ин(Ьормап,ионным выходом регистра приоритета, первый выход -- со счетным входом вто- ) счетчика, а второй выход -- с управля5 юпшми входар,1и регистра номера канала и ;)егистра приоритета и с вторым входом nepiBoro элемента ИЛИ, выход которого соединен с входом обнуления второго счетчика, выход генератора импульсов соединен с пер- вхол,ом элемента И, выход которого сое0 дипен со счетным входом первого счетчика и угравлякзп им входом компаратора, третий ;ход - с инвертором, а второй вход --- с инверсным выходом триггера, прямой выход которого является первым управляюш,им выходом блока, информационные выходы регистра но.мера канала, регистра приоритета и второго счетчика являются группами информационного выхода б.лока.

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство программного управления | 1984 |

|

SU1246055A1 |

| УСТРОЙСТВО ОБРАБОТКИ АНАЛОГОВЫХ СИГНАЛОВ С ПРИМЕНЕНИЕМ ЦИФРОВОЙ ФИЛЬТРАЦИИ | 2021 |

|

RU2777306C1 |

| МНОГОКАНАЛЬНЫЙ ИСТОЧНИК ЭЛЕКТРОПИТАНИЯ С ЗАЩИТОЙ | 1990 |

|

RU2011258C1 |

| Устройство для программного управления электроприводом | 1985 |

|

SU1260919A1 |

| Способ локальной радиотелефонной связи и система для его осуществления | 1991 |

|

SU1831767A3 |

| Многоканальное устройство для ввода аналоговых данных | 1985 |

|

SU1273911A1 |

| Многоканальная система программного управления станками | 1977 |

|

SU746426A1 |

| Устройство для чтения микрофиш с автоматической установкой кадра | 1987 |

|

SU1425588A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ПАКЕТНОЙ ИНФОРМАЦИИ ПО РАДИОКАНАЛУ | 1999 |

|

RU2168282C1 |

| Устройство для программного управления | 1985 |

|

SU1249482A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для использования в качестве системы управления группой металлообрабатывающи.х, раскладываюш,их жгуты и прочих станков. Цель изобретения - повышение быстродействия системы и сокращение числа программ - достигается путем введения в систему блока выделения приоритета, что позволило выявлять наивысший приоритет обслуживаемых каналов, номер канала с этим приоритетом и количество каналов, требуюш,их обслуживание с таким же приоритетом. 1 3. п. ф-лы, 5 ил. IND со О5 4; to N

32

,36

/.

Линии 12

кана/ о8

,3

Линия 12 канала 5

Линия 12 канала. 6

Линия 12 / анала 7

Генератор 19

UM/ll/flbCoS

Вд/тд элемента Ц 20

Приорите/пь/ t 8 () у/111/тга- / /

SbixodPi Pj. комлараторо

BbixodPt Pf компаратора г .

Линия / /,7/я 6b/j(oa , /триггера /7/

OffHt//7eHue pezi/cmpoS22,23 mpu3.27,cve/m.21

OffHi/fieHue

SfnOfJOSO

cvefrrvufoy 25 Линия 75 . I aiMffff aSapm- насти)

Зь/лод St/ffpamopa J/

| Система программного управления станками | 1974 |

|

SU603953A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Многоканальная система программного управления станками | 1977 |

|

SU746426A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

Авторы

Даты

1986-06-07—Публикация

1984-09-13—Подача