17 приращения координаты, С выходов схем 13 и 14 сигналы через логический .блок 15- поступают для управления на реверсивный счетчик 16, служащий

Изобретение относится к системам с цифровым программным управлением и предназначено для управления приводами антенных устройств и радиотелескопов ,

Цель изобретения - упрощение экс- плуатадии и повышение оперативности управления.

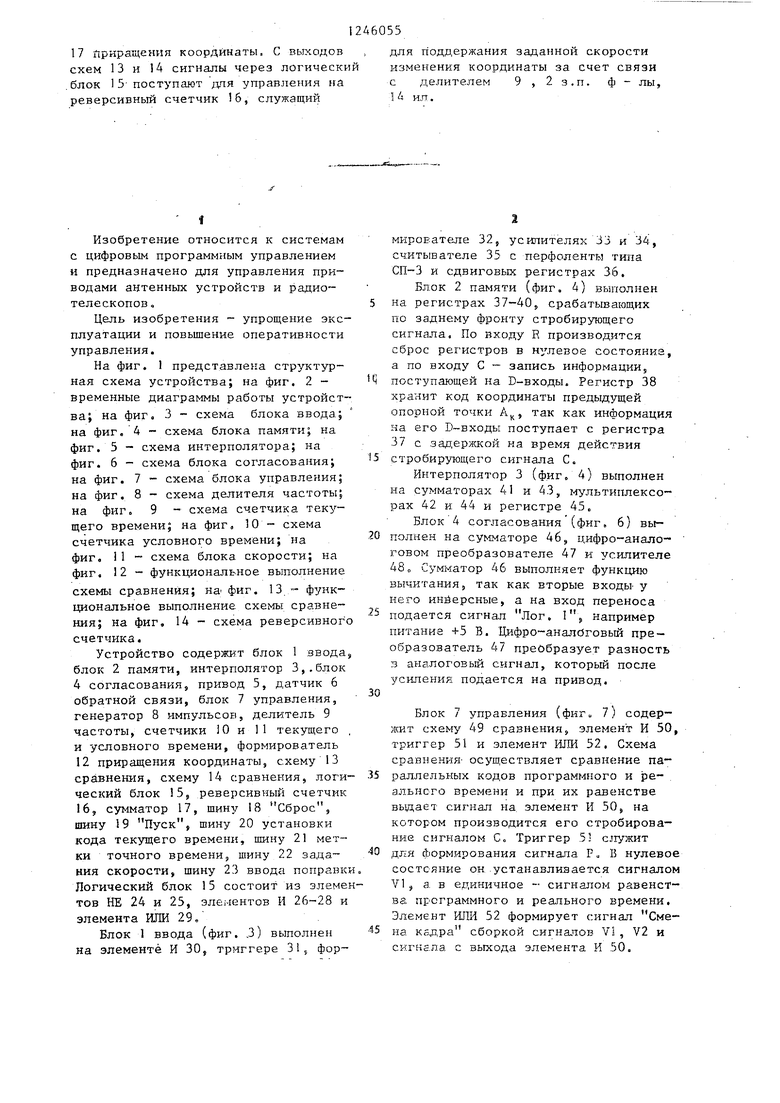

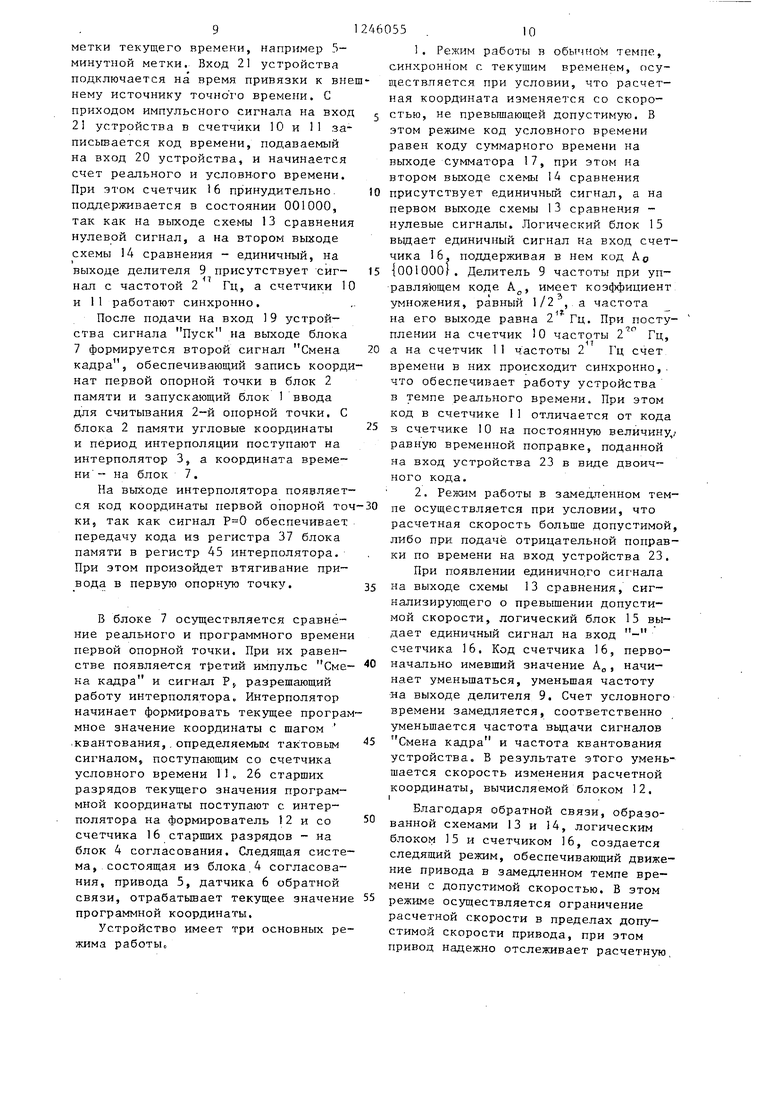

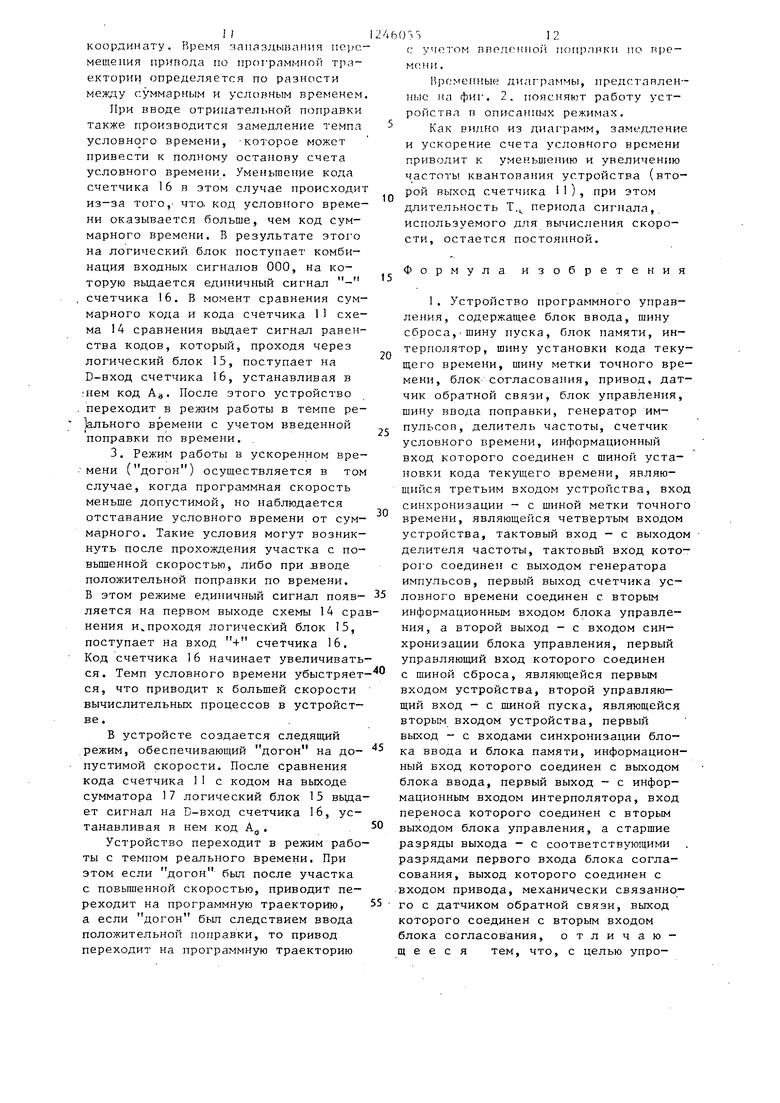

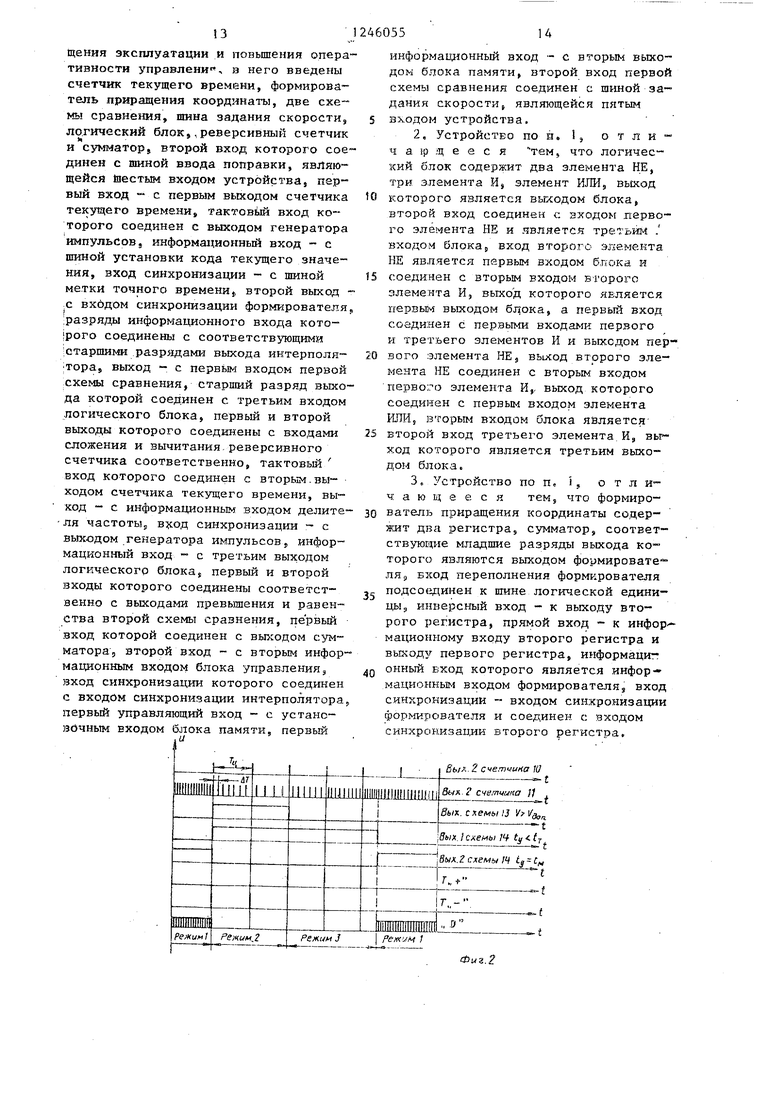

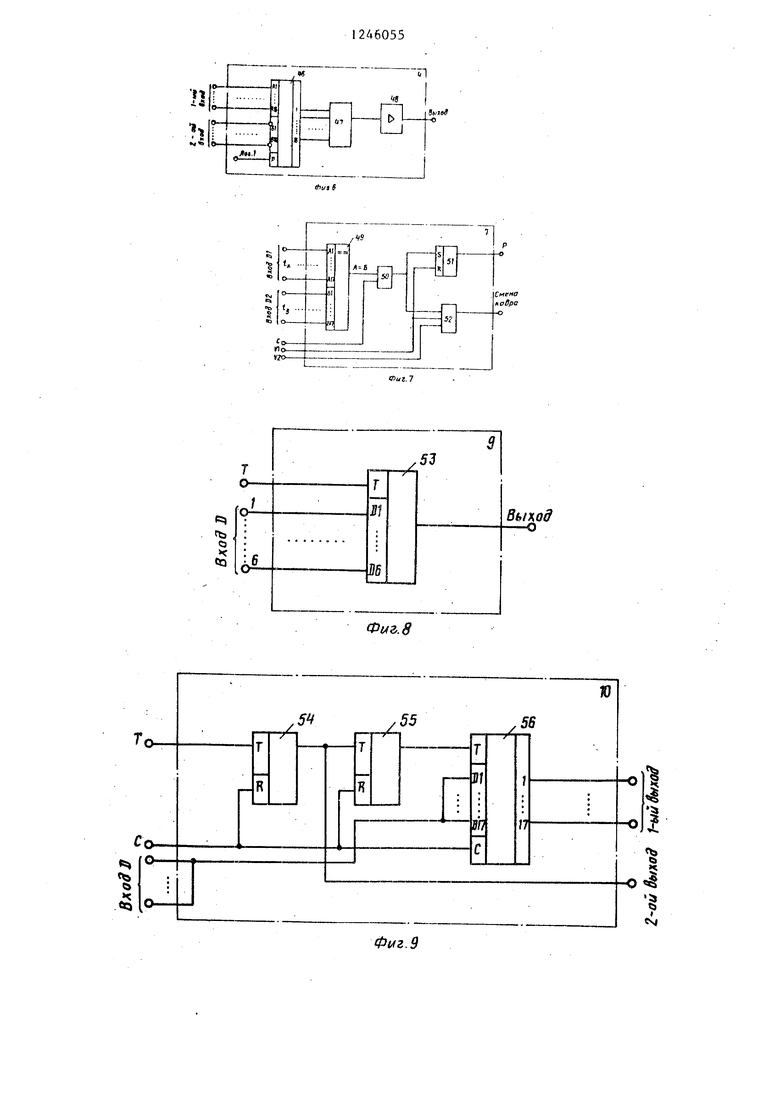

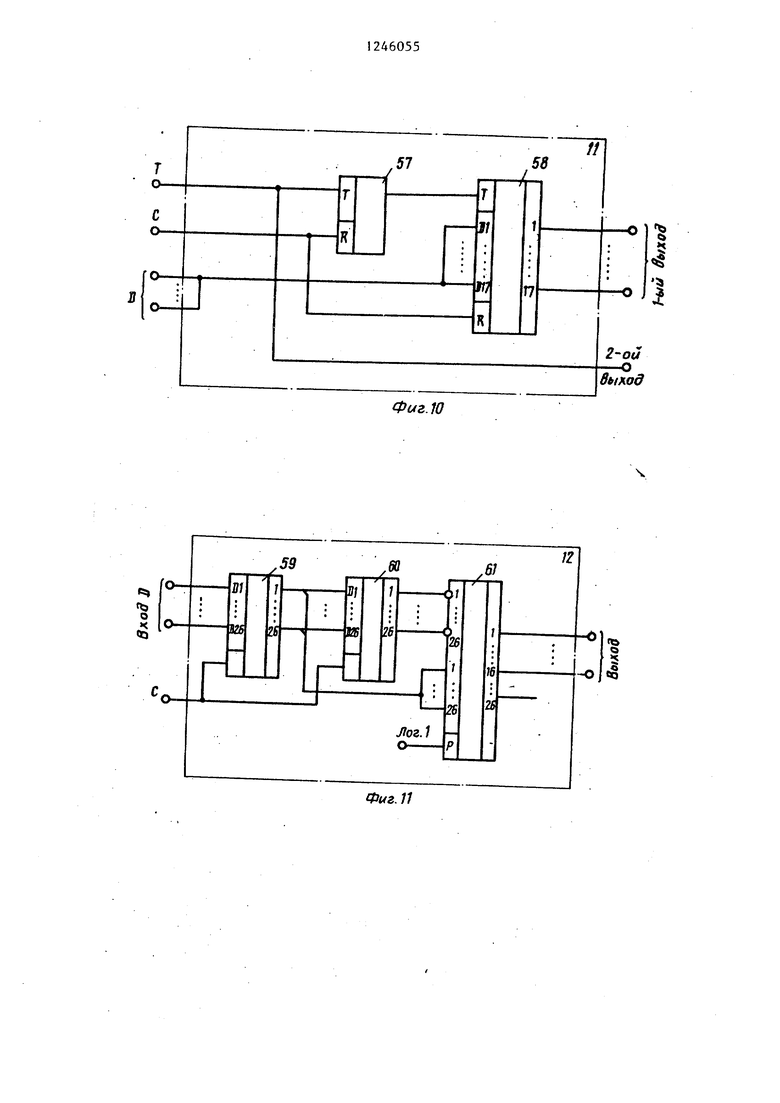

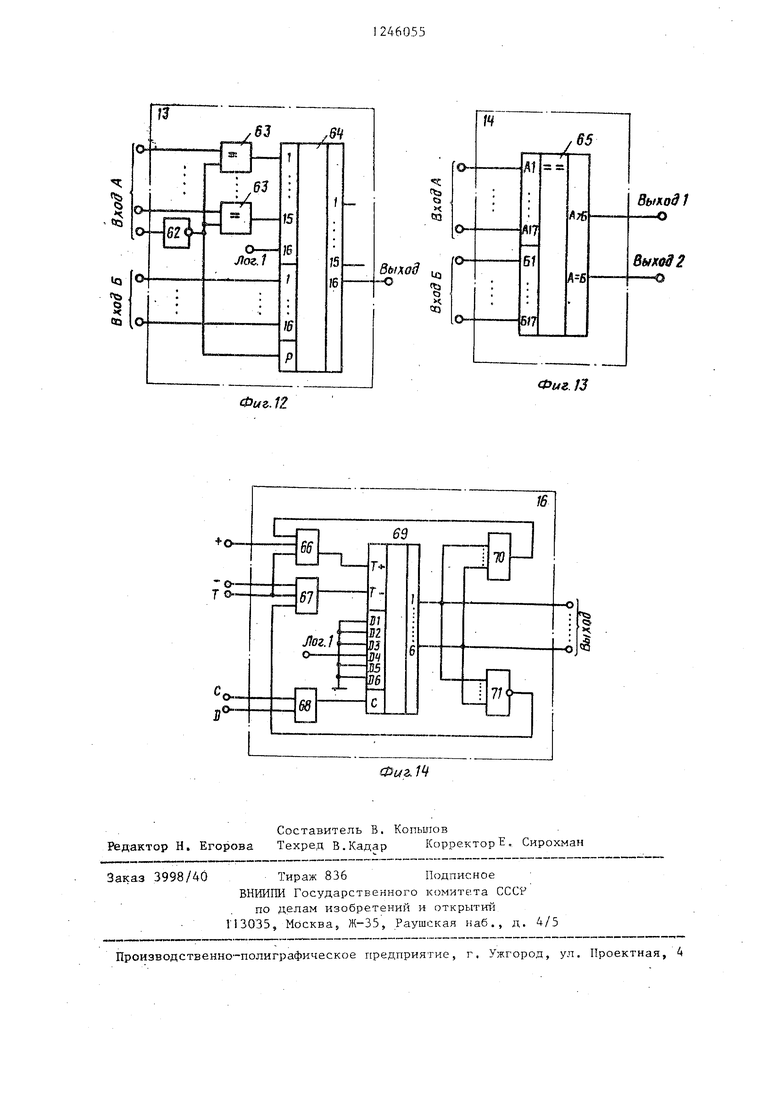

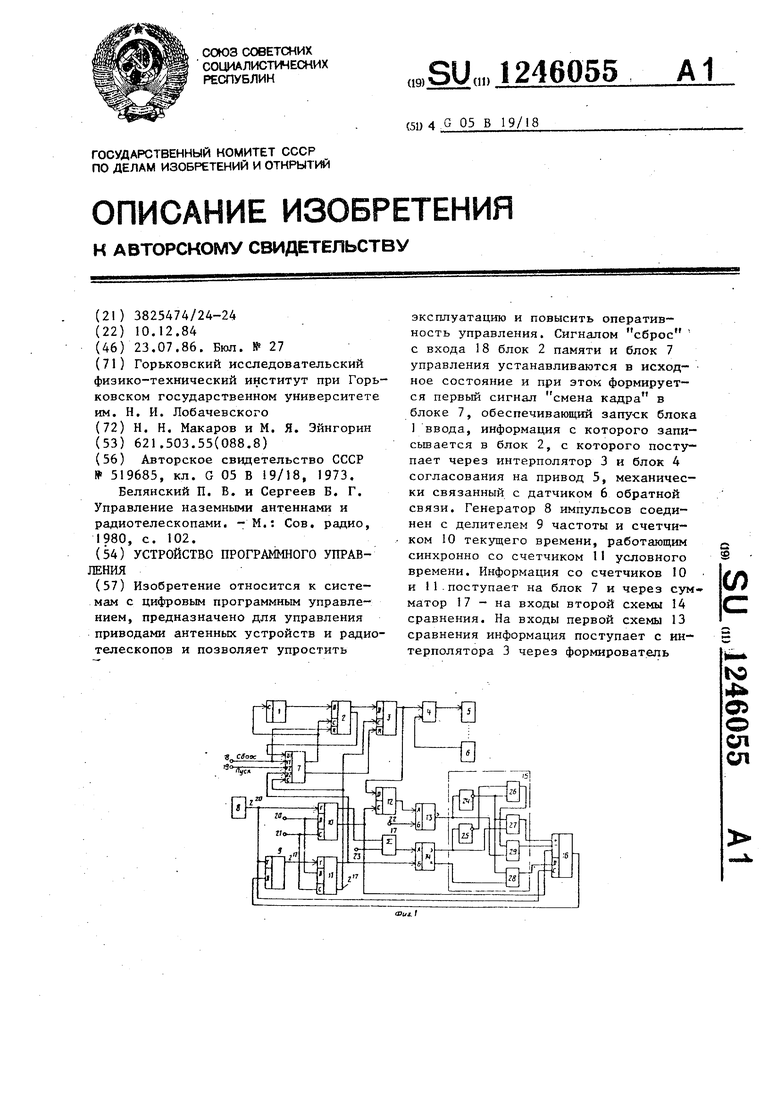

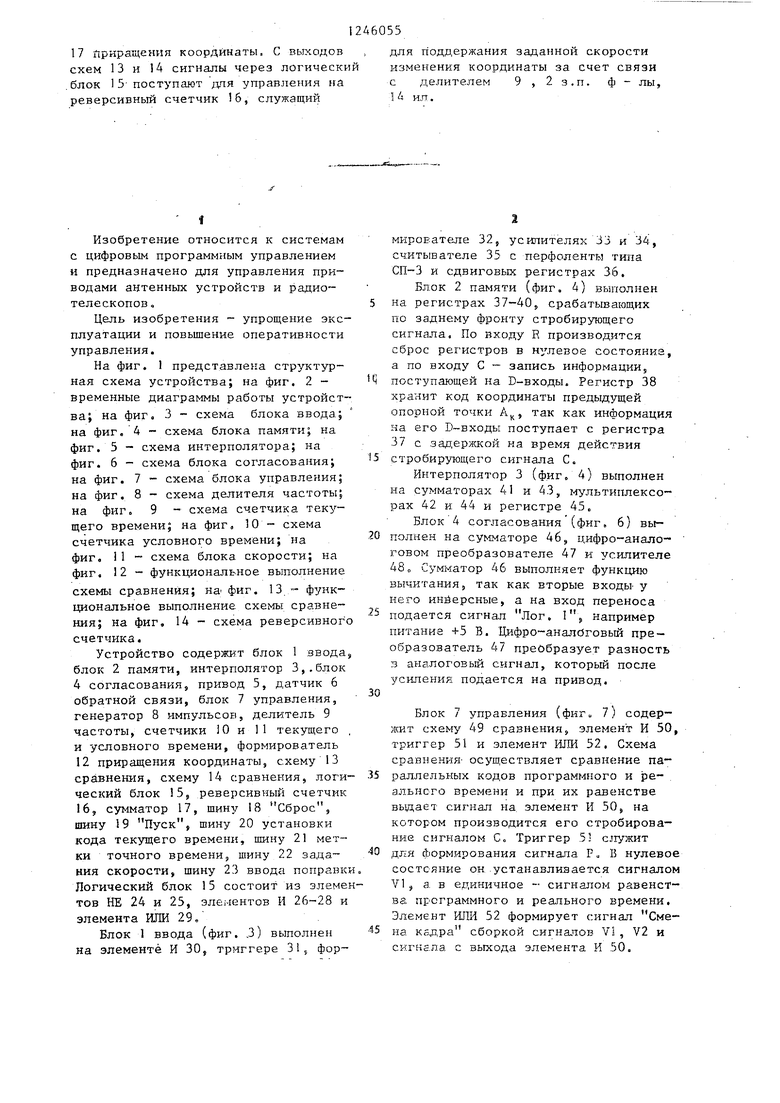

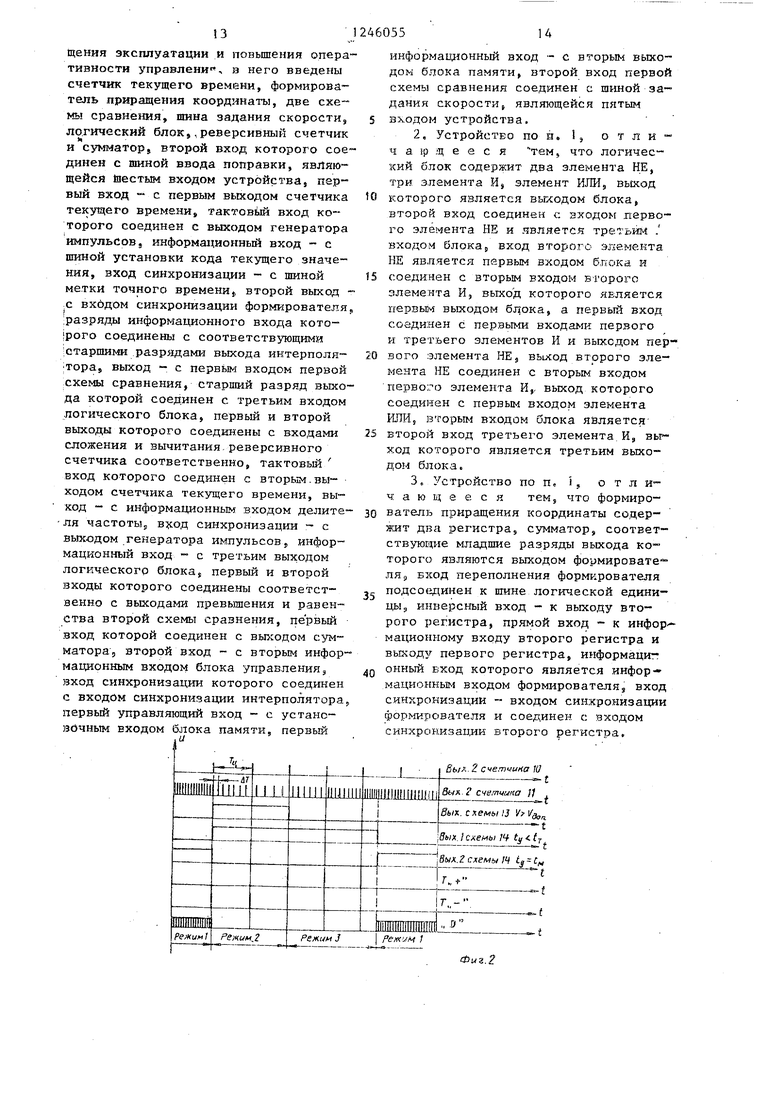

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - временные диаграммы работы устройства; на фиг. 3 - схема блока ввода; на фиг, 4 - схема блока памяти; на фиг. 5 - схема интерполятора; на фиг. 6 - схема блока согласования; на фиг. 7 - схема блока управления; на фиг. 8 - схема делителя частоты; на фиг. 9 - схема счетчика текущего времени; на фиг, 10 - схема счетчика условного времени; на фиг, И схема блока скорости; на фиг. 12 - функциональное выполнение схемы сравнения; на фиг. 13 - функциональное выполнение схемы: сравнения; на фиг, 14 - схема реверсивног счетчика.

Устройство содержит блок 1 ввода блок 2 памяти, интерполятор 3,,блок 4 согласования, привод 5, датчик 6 обратной связи, блок 7 управления, генератор 8 импульсов, делитель 9 частоты, счетчики 10 и 11 текущего и условного времени, формирователь 12 приращения координаты, схему 13 сравнения, схему 14 сравнения, логический блок 15, реверсивный счетчик 16, сумматор 17, ШИНЛ7 18 Сброс, шину 19 Пуск, шину 20 установки кода текущего времени, шину 21 метки точного времени, шину 22 задания скорости, шину 23 ввода поправк Логический блок 15 состоит из элеметов НЕ 24 и 25, элементов И 26-28 и эпемента ИЛИ 29.

Блок 1 ввода (фиг. ,3) выполнен на элементе И 30, триггере 31, фордля поддержания заданной скорости изменения координаты за счет связи с делителем 9 , 2 з.п. ф - лы,

ил.

I

мирователе 32, усилителях 33 и 34, считывателе 35 с перфоленты типа СП-3 и сдвиговых регистрах 36.

Блок 2 памяти (фиг. 4) выпо.пнен

на регистрах 37-40, срабатывающих по задн€;му фронту стробирующего сигнала. По входу R производится сброс ре;гистров в нулевое состояние, а по входу С - запись информации,

поступающей на D-входы. Регистр 38 хранит код координаты предыдущей опорной точки AJ,, так как информация на его Г -входы поступает с регистра 37 с зал;ержкой на время действия

стробирующего сигнала С.

Интерполятор 3 (фиг. 4) выполнен на сумматорах 41 и 43, мультиплексорах 42 и 44 и регистре 45,

Блок 4 согласования (фнг. 6) выполнея на сумматоре 46, цифро-анало- говом преобразователе 47 и усилителе 48,, Сумм:атор 46 выполняет функцию вычитания, так как вторые входы- у него инйерсные, а на вход переноса

подается сигнал Лог. 1, например питание +5 В. Цифро-аналбговый преобразователь 47 преобразует разность 3 аналоговьй сигнал, который после усиления подается на привод.

Блок 7 управления (фигв 7) содер- лент схему 49 сравнения, элемент И 50, триггер 51 и элемент ИЛИ 52. Схема сравнения осуш;ествляет сравнение па-

раллельных кодов программного и ре- альнсго времени и при их равенстве вьвдает сигнал на, элемент И 50, на котором производится его стробирова- ние сигналом С. Триггер 51 cjr/жит

для формирования сигнала Р. В нулевое состояние он устанавливается сигналом VI, а в единичное - сигналом равенства программного и реального времени. Элемент ИЛИ 52 формирует сигнал Смена кадра сборкой сигналов VI , V2 и сигка.ла с выхода элемента И 50.

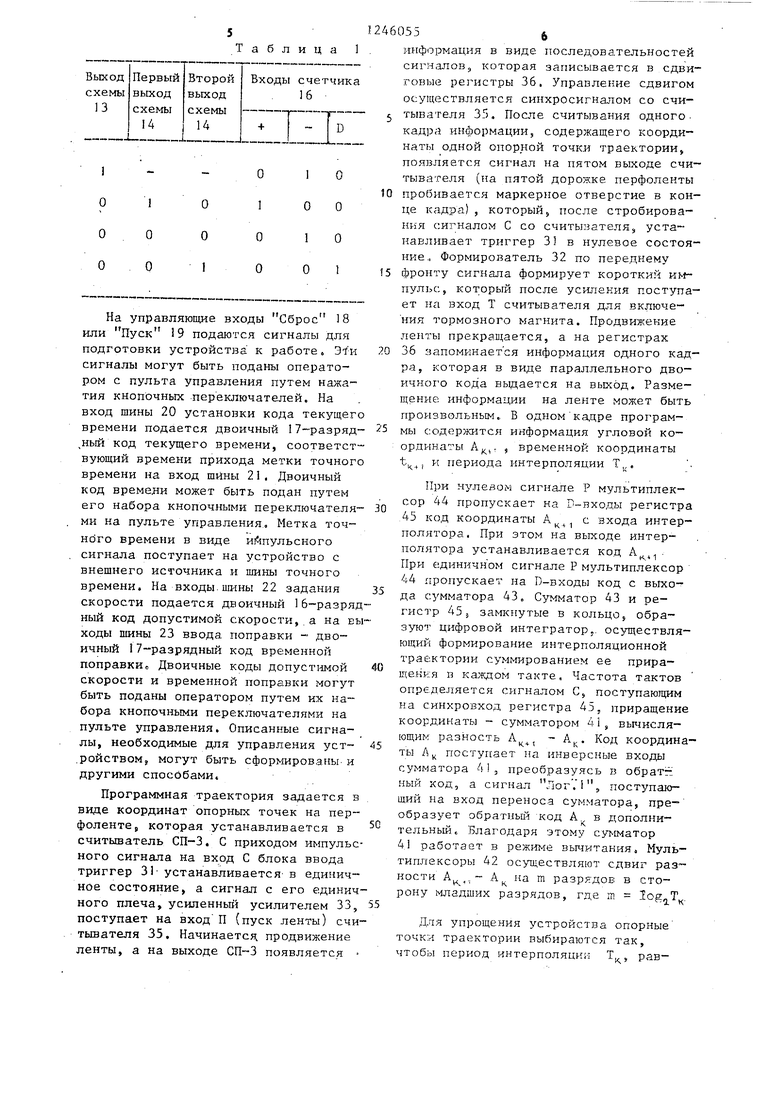

Делитель 9 частоты (фиг. 10) выполнен на счётчике 53 с переменным коэффицигентом деления:. На вход Т поступает частота с тактового генератора, равная (2 Гц, а на выходе формируется импульсный сигнал с частотой

, где А - двоичный шеf

стиразр ядный код управления, поступающий на D-вход. Делитель 9 может быть выполнен на одной микросхеме К155ИЕ8. При поступлении на D-вход кода А 001000 на выходе делителя будет сигнал частотой 2 Гц.

Счетчик 10 текущего времени (фиг. 9) выполнен на двоичных счетчиках 54-56. Счетчик 54 имеет десять двоичных разрядов, с его выхода снимается сигнал с частотой 2 Гц Счетчик -55 имеет также десять разрядов, с его выхода снимается сигнал с частотой 1 Гц. Счетчик 56 имеет 17 разрядов и выполнен с обратной связью, обеспечивающей счет до 24 часов . При подаче на вход С метки точного времени производится зануление счетчиков 54, 55 и установка в счет- чик 56 кода, поданного на входы D1- D17.

Счетчик I1 условного времени (фиг, 10) выполнен на семнадцатираз- рядных двоичных счетчиках 57 и 58. Счетчик 58 выполнен с обратной связью и осуществляет счет времени до 24 часов. При поступлении на вход с метки точного времени счетчик 57 за- нуляется, а в счетчик 58 записываетс код времени, подаваемый на входы D1- D17.

Формирователь 12 приращения координаты (фиг. 11) выполнен на регистрах 59 и 60, срабатывающих по заднем фронту стробирующего сигнала, и сумматоре 61. На вход С поступает сигнал с частотой 2 ° Гц, который запи- сьтает в регистры 59 и 60 два соседних значения расчетной координаты. Сумматор 61 выполняет вычитание из расчетной координаты, записанной в регистр -59, ее предыдущего значения, записанного в регистр 60. На выход формирователя 12 с сумматора 61 выдаются шестнадцать младших разрядов кода, который равен скорости изменения расчетной координаты.

Схема 13 сравнения (фиг. 12) выполнена на инверторе 62, группе из 15 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 63 и

сумматоре 64. Схема сравнения осуществляет сравнение модулей скоростей. Если код скорости, поступающий по входу А, имеет отрицательный знак 5 (старший разряд равен 1), то он на сумматор поступает без изменений. .Если код скорости по входу А имеет положительный знак, то на выходе инвертора 62 устанавливается единичный

0 сигнал, поступающий на вход переноса сумматора и на -вторые входы элементов ИСКЛЮЧАЩЕЕ ИЛИ 63, Входной код скорости, проходя через элементы 63, инвертируется, а сумматор осуществляет

5 вьгчитанде из кода, поступающего по входу Б, Если код, поступающий по входу А, больше кода скорости, поступающего по входу Б, то код разности отрицательный, а старший разряд раз0 ности на выходе сумматора единичный. Схема 14 сравнения (фиг. 13) выполняет операцию сравнения двух 16- разрядных кодов и может быть выполнена на цифровом компараторе 65.,

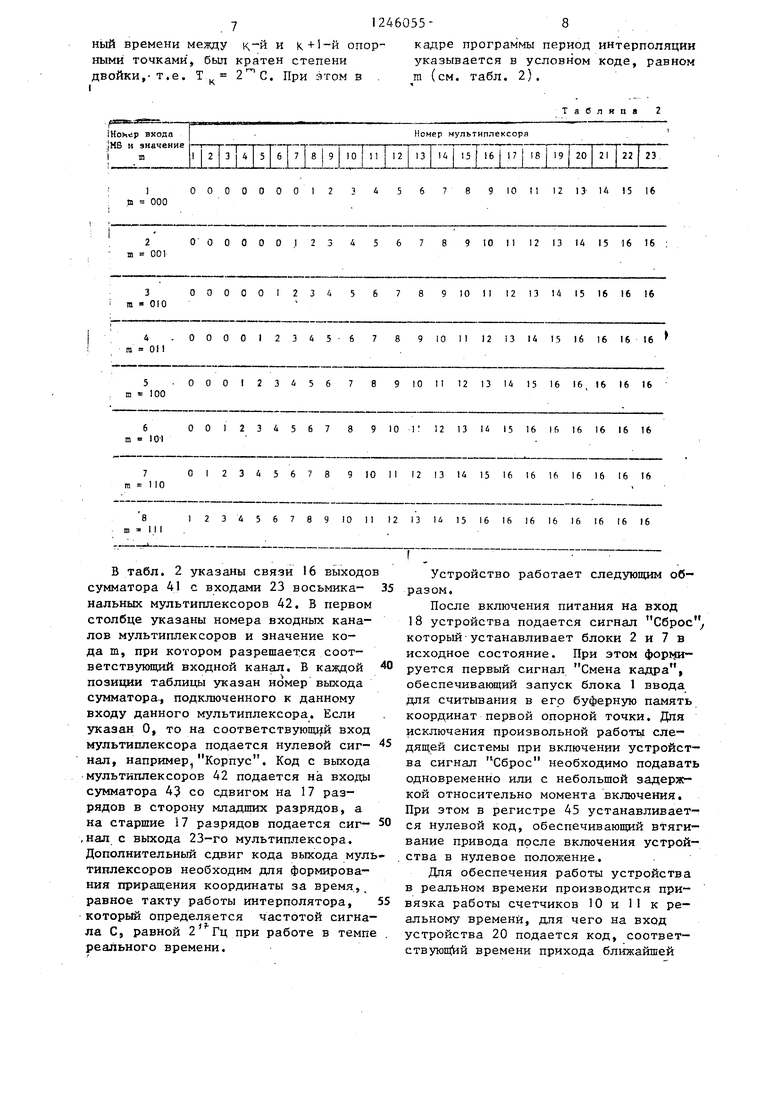

5 Счетчик 16 (фиг. 14) является реверсивным. Элементы И 66 и 67 коммутируют счетный импульс в канал - или счетчика 69 в зависимости от наличия сигналов управления +

Q или Если указанные сигналы от- . сутствуют, то счетчик 69 не считает Счетчик 69 имеет 6 разрядов. На входы D6-D1 поступает код 001000 путем подачи на них постоянных уровней сигналов,

Элемент И 68 осуществляет строби- рование сигнала по входу D тактовым сигналом С, При появлении сигнала D счетчик 69 принудительно устанавлиQ вается в состояние 001000. При поступлении сигналов счет + или счет - счетчик от состояния 001000 считает в сторону увеличения или уменьшения кода, но при достижении им со5 стояний 000000 или 111111 его работа прекращается. Элементы ИЛИ 70 и И-НЕ 71 обеспечивают запрет счета в соответствующих направлениях при переполнении счетчика,

Q Генератор 8 (фиг. I) обеспечивает формирование высокостабильного тактового сигнала с .частотой 2 Гц..

Логический блок I5 управляет 5 счетчиком 16.

Логические элементы 24-28 обеспечивают работу блока в соответствии с табл„ 1 .

Таблица 1 ,

На управляющие входы Сброс 8 или Пуск 19 подаются сигналы для подготовки устройства к работе. Эч и сигналы могут быть поданы оператором с пульта управления путем нажа тин кнопочных переключателей. На вход шины 20 установки кода текущего времени подается двоичный 17-разряд- ,ный код текущего времени, соответствующий времени прихода метки точного времени на вход шины 21, Двоичный код времеди может быть подан путем его набора кнопочными переключателями на пульте управления.. Метка точного времени в виде импульсного сигнала поступает на устройство с внешнего источника и шины точного времени. На входы, ип-сны 22 задания скорости подается двоичный 16-разряд ный код допустимой скорости,,а на вы ходы щины 23 ввода поправки - двоичный I 7-разрядный код временной поправки Двоичные коды допустимой скорости и временной поправки могут быть поданы оператором путем их набора кнопочными переключателями на пульте управления. Описанные сигна

лы, необходимые для управления уст- .ройством, могут быть сформированы- и другими способами.

Программная траектория задается в виде координат опорных точек на перфоленте, которая устанавливается в считыватель СП-3. С приходом импульсного сигнала на вход С блока ввода триггер устанавливается в единичное состояние, а сигнал с его единичного плеча, усиленны усилителем 33, поступает на вход П (пуск ленты) считывателя 35, Начинается продвижение ленты, а на выходе СП-3 появляется

460556

информация в виде последовательностей сигналов, которая записывается в сдви- :говые регистры 36, Управление сдвигом осуществляется синхросигналом со счи- 5 тывателя ЗГ). После считывания одного- кадра информации, содержащего координаты одной опорной точки траектории, появляется сигнал на пятом выходе считывателя (на пятой дорожке перфоленты

10 пробивается маркерное отверстие в конце кадра), который, после стробирова- нкя сигналом С со считывателя, устанавливает триггер 31 в нулевое состояние,, Формирователь 32 по переднему

15 фронту сигнала формирует короткий импульс, который после усиления поступает на вход Т считывателя для включения тормозного магнита. Продвижение лепты прекращается, а на регистрах

30 36 запоминается информация одного кад ра, которая в виде параллельного двоичного кода выдается на выход. Размещение информации на ленте может быть произвольным., В одном ка,цре програм2 5 мы сюдержится информация угловой координаты А,, , временной координаты t. и периода интерполяции Т„,

При нулевом сигнале Р мультиплексор 4А пропускает на D-входы регистра 45 код координаты А, с входа интерполятора. При этом на выходе интерполятора устанавливается код А . При единичнЪм сигнале Р мультиплексор 44 пропускает на D-БХОДЫ код с выхо- да сумматора 43. Сумматор 43 и регистр 45J замкнутые в кольцо, образуют цифровой интегратору, осуществляющий формирование интерполяционной траектории суммированием ее прира- ще.кк:я в каждом такте. Частота тактов определяется сигналом С, поступающим на синхровход регистра 45, приращение координаты - сумматором 41, вычисля

ющим разность А,,, - А... Код координаK, 1 Г

ты Л поступает на инверсные входы сумматора 41 , преобразуясь в обратг ный код, а сигнал Лог.,, поступающий на вход переноса сумматора, пре образует обратньш код А в дополни- тельньшс Благодаря этому сумматор 41 работает в режиме вычитания. Мультиплексоры 42 осуществляют сдвиг разности А,., .А. на m разрядов в сторону младших разрядов, где m log,.

Для упрощения устройства опорные точки траектории выбираются так, чтоб1э1 период интерполяции- Т,, рав-

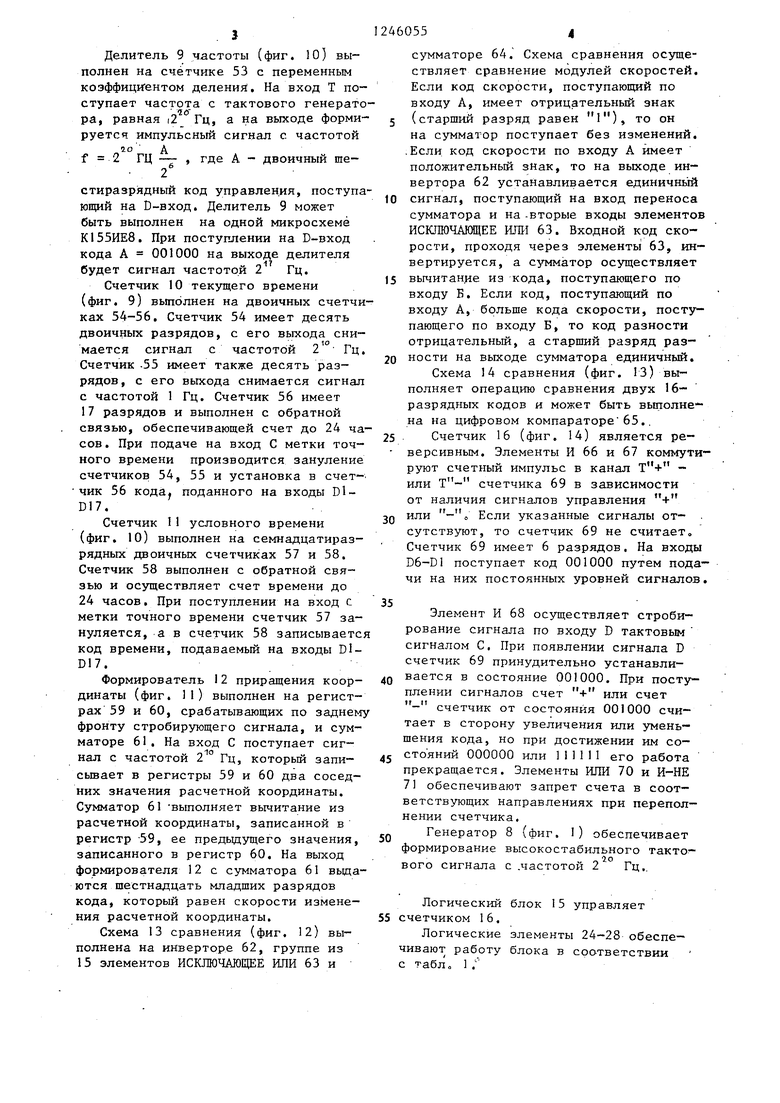

ный времени между и опор- кадре программы период интерполяции ными точками , был кратен степени указывается в условном коде, равном двойки,-т.е. Т 2 С. При зтом в . т (ем. табл. 2).

Номер мультиплексор

2 I 3 I 4 ТГбТ7Т8 9 I 10 I 11 I 12 I 13 IU lsTl6J 17

1000000012 3 4 5 6 7

m 000

2О О О О О О ,1 2 3 4 5 6 7 8 9 10 I 1 12 13 14 15 16 16 :

m 001

3000001234 5 6 7 8 9 10 I 1 12 13 14 15 16 16 16

m 010

I4 .000012345-6 7 8 9 10 11 12 13 14 15 16 16 16 16

;ru on

5 .000123456 7 8 9 10 M 12 13 14 15 16 16, 16 16 16 m 100

6001234567 8 9 10 12 13 14 15 16 16 16 16 16 16

m lO l

7012345678 9 10 1 1 12 13 14 15 16 16 16 16 16 16 16

m 110

81 23456789 10 11 12 13 14 15 16 16 16 16 16 16 16 16

m 1 I I .

В табл. 2 указаны связи 16 выходо сумматора 41 с входами 23 восьмика- нальных мультиплексоров 42. В первом столбце указаны номера входных каналов мультиплексоров и значение кода т, при котором разрешается соот- ветствуюпщй входной канал. В каждой позиции таблицы указан номер выхода сумматора., подключенного к данному входу данного мультиплексора. Если указан О, то на соответствуюпщй вход мультиплексора подается нулевой сиг- нал, например, Корпус. Код с выхода мультиплексоров 42 подается на входы сумматора 43 со сдвигом на 17 разрядов в сторону младших разрядов, а на старшие 7 разрядов подается сиг- ,нал с выхода 23-го мультиплексора. Дополнительный сдвиг кода выхода мултиплексоров необходим для формирования приращения координаты за время, равное такту работы интерполятора, который определяется частотой сигнала С, равной при работе в темп реального времени.

Таблица 2

Номер мультиплексора

18 I 19 20

2lT22

23

9 10 М 12 13- 14 15 16

Устройство работает следующим образом.

После включения питания на вход 18 устройства подается сигнал Сброс который устанавливает блоки 2 и 7 в исходное состояние. При этом руется первый сигнал Смена кадра, обеспечивающий запуск блока 1 ввода для считывания в его буферную память координат первой опорной точки. Для исключения произвольной работы следящей системы при включении устройства сигнал Сброс необходимо подавать одновременно или с небольшой задержкой относительно момента включения. При этом в регистре 45 устанавливается нулевой код, обеспечивающий втягивание привода после включения устройства в нулевое положение.

Для обеспечения работы устройства в реальном времени производится привязка работы счетчиков Ю и 11 к реальному времени, для чего на вход устройства 20 подается код, соответ- ствуюш й времени прихода ближайшей

9

метки текущего времени, например 5- минутной метки. Вход 21 устройства подключается на время привязки к вненему источнику точно го времени. С приходом импульсного сигнала на вход 21 устройства в счетчики 10 и 11 за- письгоается код времени, подаваемый на вход 20 устройства, и начинается счет реального и условного времени. При этом счетчик 16 принудительно. поддерживается в состоянии 001000, так как на выходе схемы 13 сравнения нулевой сигнал, а на втором выходе схемы 14 сравнения - единичный, на выходе делителя 9 присутствует сиг- нал с частотой 2 Гц, а счетчики 10 и 11 работают синхронно.

После подачи на вход 19 устройства сигнала Пуск на выходе блока 7 формируется второй сигнал Смена кадра, обеспечивающий запись координат первой опорной точки в блок 2 памяти и запускающий блок 1 ввода для считывания 2-и опорной точки, С блока 2 памяти угловые координаты и период интерполяции поступают на интерполятор 3, а координата времени - на блок 7.

На выходе интерполятора появляется код координаты первой опорной точ ки, так как сигнал обеспечивает передачу кода из регистра 37 блока памяти в регистр 45 интерполятора. При этом произойдет втягивание привода в первую опорную точку.

В блоке 7 осуществляется сравнение реального и программного времени первой опорной точки. При их равенстве появляется третий импульс Сме- на кадра и сигнал 7 разрешающий работу интерполятора. Интерполятор начинает формировать текущее программное значение координаты с шагом .квантования,, определяемым так товым сигналом, поступающим со счетчика условного времени 11„ 26 старших разрядов текущего значения программной координаты поступают с интерполятора на формирователь 12 и со счетчика 16 старших разрядов - на блок 4 согласования. Следящая система, , состоящая из блока.4 согласования, привода 5, датчика 6 обратной связи, отрабатьшает текущее значение программной координаты.

Устройство имеет три основных режима работы

55 .10

1.Режим работы в обычно м темпе, инхронном с текущим временем, осуествляется при условии, что расчетая координата изменяется со скоротью, не превьш1ающей допустимую. В этом режиме код условного времени авен коду суммарного времени на ыходе сумматора 17, при этом на тором выходе схемы 14 сравнения присутствует единичный сигнал, а на первом выходе схемы 13 сравнения - нулевые сигналы. Логический блок 15 вьщает единичный сигнал на вход счетчика 16, поддерживая в нем код АО {ООЮОО}. Делитель 9 частоты при управляющем коде А, имеет коэ Фициент умножения, равный 1/2 ,,а частота

на его выходе равна 2 Гц. При поступлении на счетчик 10 частоты 2 Гц, а на счетчик 11 частоты 2 Гц счет времени в них происходит синхронно,- что обеспечивает работу устройства в темпе реального времени. При этом код в счетчике I1 отличается от кода в счетчике 10 на постоянную величину, равную временной поправке, поданной на вход устройства 23 в виде двоичного кода.

2.Режим работы в замедленном темпе осуществляется при условии, что расчетная скорость больше допустимой, либо при подаче отрицательной поправки по времени на вход устройства 23.

При появлении единичного сиг Нала на выходе схемы 13 сравнения, сигнализирующего о превышении допустимой скорости, логический блок 15 выдает единичный сигнал на вход - счетчика. 16. Код счетчика 16, первоначально имевший значение А, начинает уменьшаться, уменьшая частоту на выходе делителя 9, Счет условного времени замедляется, соответственно уменьшается частота вьщачи сигналов Смена кадра и частота квантования устройства, В результате этого уменьшается скорость изменения расчетной

координаты, вычисляемой блоком 12, I

Благодаря обратной связи, образованной схемами 13 и 14, логическим блоком 15 и счетчиком 16, создается следящий режим, обеспечивающий движение привода в замедленном темпе времени с допустимой скоростью. В этом режиме осуществляется ограничение расчетной скорости в пределах допустимой скорости привода, при этом привод н,адежно отслеживает расчетную,

координату. Время запаздывания пеукг- мещения привода по программной траектории определяется по разности между суммарным и условным временем. При вводе отрицательной поправки также производится замедление темпа условного времени, -которое может привести к полному останову счета условного времени. Уменьшение кода счетчика 16 в этом случае происходит из-за того,- что. код условного времени оказывается больше, чем код суммарного времени. В результате этого на логический блок поступает комбинация входных сигналов 000, на которую выдается единичный сигнал -

счетчика 16. В момент сравнения суммарного кода и кода счетчика 11 схема 14 сравнения выдает сигнал равенства кодов, который, проходя через логический блок 15, поступает на D-вход счетчика 16, устанавливая в нем код Ад. После этого устройство

переходит в режим работы в темпе ре- Тального времени с учетом введенной поправки по времени.

3. Режим работы в ускоренном времени (догон) осуществляется в том случае, когда программная скорость меньше допустимой, но наблюдается отставание условного времени от суммарного. Такие условия могут возникнуть после прохождения участка с повышенной скоростью, либо при зводе положительной поправки по времени.

В этом режиме единичный сигнал появ- 35 ловного времени соединен с вторым

ляется на первом выходе схемы 14 сравнения и проходя логический блок 15, поступает на вход + счетчика 16. Код счетчика 16 начинает увеличивать-

информационным входом блока управл ния, а второй выход - с входом син хронизации блока управления, первы управляющий вход которого соединен

ся. Темп условного времени убыстряет- с шиной сброса, являющейся первым

ся, что приводит к большей скорости вычислительных процессов в устройстве.

В устройств создается следящий .режим, обеспечивающий догон на допустимой скорости. После сравнения кода счетчика 11 с кодом на выходе сумматора 17 логический блок 15 выдает сигнал на D-вход счетчика 16, устанавливая в нем код Ад.

Устройство переходит в режим работы с темпом реального времени. При этом если догоп был после участка с повьш1енной скоростью, приводит переходит на программную траекторию, а если догон был следствием ввода положительной поправки, то привод переходит на программную траекторию

0

5

0

5

С учетом введенной псшрлнки по яре- моли .

Временные диаграммы, представленные на фиг. 2, поясняют работу устройства в oпиcafIиыx режимах.

Как видно из диаграмм, замедление и ускорение счета условного времени приводит к уменьшению и увеличению частоты квантова1 ия устройства (второй выход счетчика I), при этом длительность Т, периода сигнала,, используемого для вычисления скорости, остается постоянной.

Формула изобретения

1. Устройство программного управления, содержащее блок ввода, шину сброса,-шину пуска, блок памяти, интерполятор, шину установки кода текущего времени, шину метки точного времени, блок- согласования, привод, датчик обратной связи, блок управления, шину ввода поправки, генератор импульсов, делитель частоты, счетчик условного времени, информационный вход которого соединен с шиной установки кода текущего времени, являющийся третьим входом устройства, вход синхронизации - с шиной метки точного времени, являющейся четвертым входом устройства, тактовый вход - с выходом делителя частоты, тактовый вход кото- poi o соединен с выходом генератора импульсов, первый выход счетчика ус-

информационным входом блока управления, а второй выход - с входом синхронизации блока управления, первый управляющий вход которого соединен

5

0

5

входом устройства, второй управляющий вход - с шиной пуска, являющейся вторым входом устройства, первый выход - с входами синхронизации блока ввода и блока памяти, информационный вход которого соединен с выходом блока ввода, первый выход - с информационным входом интерполятора, вход переноса которого соединен с вторым выходом блока управления, а старшие разряды выхода - с соответствующими разрядами первого входа блока согласования, выход которого соединен с входом привода, механически связанного с датчиком обратной связи, вы-ход которого соединен с вторым входом блока согласов ания, отличающееся тем, что, с целью упроS3

щения эксплуатации и повьппемия оперативности управлени, )з него введены счетчик текущего времени, формирователь лриращения координаты, две схемы сравнения, шина задания скорости, логический блок,,реверсивный счетчик и сумматор( второй вход которого соединен с пшной ввода поправки, являющейся Шестым входом устройства, первый вход - с первым выходом счетчика текущего времени, тактовЬш вход которого соединен с выходом генератора импульсов, информационный вход - с шиной установки кода текущего значения, вход синхронизации - с шиной метки точного времени j, второй выход с входом синхронизации формирователя ;разряды информационного входа кото- iporo соединены с соответств тощими :старшими разрядами выхода интерполя- iTOpaj выход - с первым входом первой :скемы сравнения, старший разряд выхода которой соединен с третьим входом логического блока, первый и второй выходы которого соединены с входами сложения и вычитания,реверсивного счетчика соответственно, тактовый вход которого соединен с вторым.вы- ходом счетчика текущего времени, выход - с информационным: входом делите ля частоты вуод синхронизации - с выходом генератора импульсов., информационный вход - с третьим выходом логического блока, первый и второй входы которого соединены соответственно с выходами превьшения и равен™ ства второй схемы сравнения, первый вход которой соединен с выходом сумматора, второй вход - с вторым инфор мационным входом блока управления, вход синхронизации которого соединен с входом синхронизации интерполятора первый управляющий вход - с устано- зЬчным входом блока памяти, первый

55

14

информац;ионный вход - с вторым выходом биока памяти, второй вход первой схемы сравнения соединен с задания скорости, являющейся пятым входом устройства,

2,Устройство по н. 1J о т л и - ч а tp щ е е с я тем, что логический блок содержит два элемента НЕ, три элемента И, элемент ИЛИ, выход

которого является выходом блока,

второй вход соединен с входом лерво- го элемента НЕ и является третьим . входом блока5 вход второго элемента НЕ является первым входом блока и

соединен с вторым входом второго элемента И, выход которого является первьм выходом блока, а первый вход соединен с первыми входа и первого и третьего элементов И и выходом первого элемента HEj вьисод второго элемента НЕ соединен с вторым входом первого элемента И,, выход которого соединен с первым входом элемента ИЛИ5 вторым входом блока являетсявторой вход третьего элемента.И, вы ход которого является третьим выходом блока.

3,Устройство по п. , отличают е е с к тем, что формирователь приращения координаты содер- ж:ит два регистра, сумматор, соответствующие младщие разряды выхода которого являются выходом формирователя р вход переполнения формирователя подсоединен к шине логической едини

ць,, инверсный вход - к выходу второго регистра, прямой вход - к инфор мационному входу второго регистра и выходу первого регистра, информациг онный вход которого является иифор- мационныг.1 входом формирователя, вход синхронизации - входом синхронизации формирователя и соединен с входом CHHxpoHHsanjiH второго регистра.

W

ft

«ъ , 1

к

Stiiif

Tl

L

Фиг. 8

s

N

.9

Фиг. 11

Фиг. 12

Составитель В. Копьиюв Редактор Н. Егорова Техред В.Кадар КорректорЕ, Сирохман

3998/40

Тираж 836 Подписное ВНИМИ Государственного комитента СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., i, 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

Фиг. /J

Фи. /4

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного управления | 1985 |

|

SU1249482A1 |

| ЛИНЕЙНО-КРУГОВОЙ ИНТЕРПОЛЯТОР | 1991 |

|

RU2010293C1 |

| Устройство для коррекции положения резца на станке с программным управлением | 1981 |

|

SU983651A1 |

| Линейный интерполятор | 1987 |

|

SU1439534A1 |

| Устройство для программного управления электроприводом | 1985 |

|

SU1260919A1 |

| Интерполятор | 1987 |

|

SU1413602A1 |

| Интерполятор | 1988 |

|

SU1541557A1 |

| Цифровой интерполятор | 1984 |

|

SU1238033A1 |

| Многокоординатный линейно-круговой интерполятор | 1988 |

|

SU1603345A1 |

| Линейный интерполятор для систем интерактивной графики | 1988 |

|

SU1608691A1 |

Изобретение относится к системам с цифровым программным управлением, предназначено для управления приводами антенных устройств и радиотелескопов и позволяет упростить эксплуатацию и повысить оперативность управления. Сигналом сброс с входа 18 блок 2 памяти и блок 7 управления устанавливаются в исходное состояние и при этом формируется первый сигнал смена кадра в блоке 7, обеспечивающий запуск блока 1 ввода, информация с которого запи- сьтается в блок 2, с которого поступает через интерполятор 3 и блок 4 согласования на привод 5, механически связанный с датчиком 6 обратной связи. Генератор 8 импульсов соединен с делителем 9 частоты и счетчиком 10 текущего времени, работающим синхронно со счетчиком 11 условного времени. Информация со счетчиков 10 и П-поступает на блок 7 и через сумматор 17 - на входы второй схемы 14 сравнения. На входы первой схемы 13 сравнения информация поступает с интерполятора 3 через формирователь S (Л го 4аь а о сд СП

| Система программного управления | 1973 |

|

SU519685A1 |

| Кипятильник для воды | 1921 |

|

SU5A1 |

| Белянский П | |||

| В | |||

| и Сергеев Б | |||

| Г | |||

| Управление наземными антеннами и радиотелескопами | |||

| - М.: Сов, радио, 1980, с | |||

| Транспортер для перевозки товарных вагонов по трамвайным путям | 1919 |

|

SU102A1 |

Авторы

Даты

1986-07-23—Публикация

1984-12-10—Подача