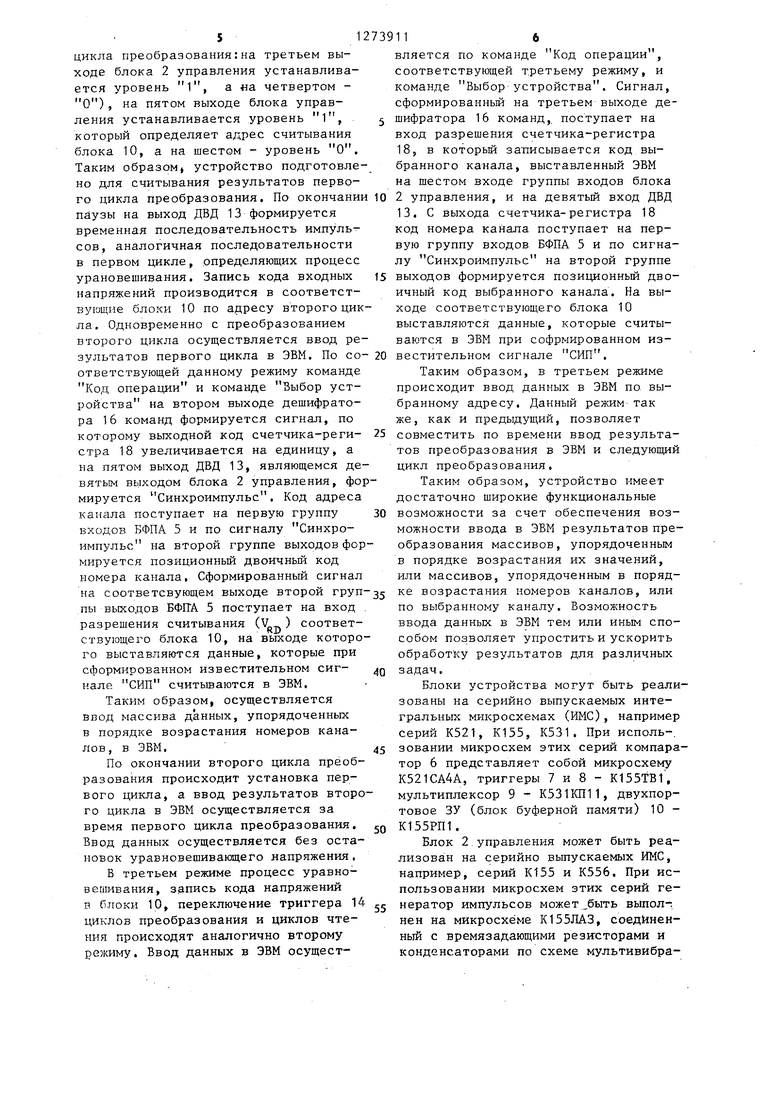

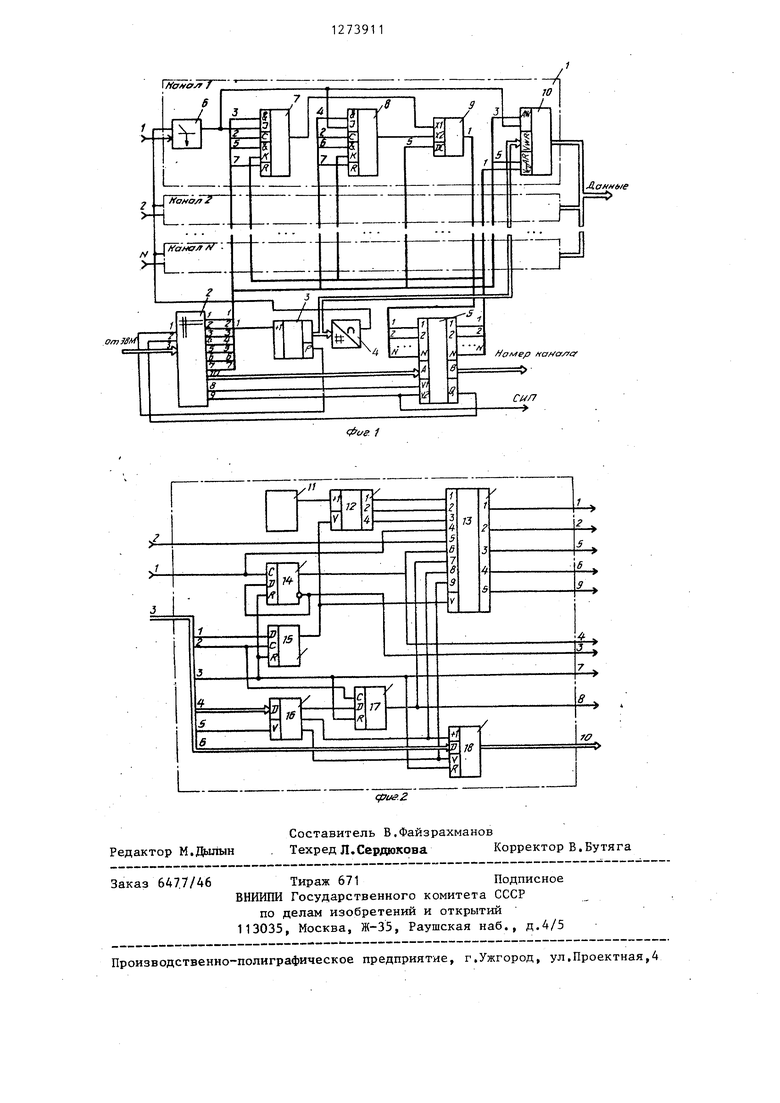

Изобретение относится к измерительной и вычислительной технике и может быть использовацо при пестроении высокопроизводительных систем сбора и обработки аналоговых данных. Цель изобретения - расширение области применения устройства путем введения двух дополнительных режимов ввода данных. На фиг,1 приведена структурная схема устройства; на фиг,2 - конструкция блока управления. Схема содержит каналы 1 преобразования, блок 2 управления,счетчик 3, цифроаналоговый преобразователь (ЦАП) 4, блок 5 формирования приоритетного адреса (БФПА), компараторы 6, триггеры первой 7 и второй 8 груп пы, мультиплексоры 9, блок 10 буферной памяти. На фиг.2 обозначены: генератор 11 импульсов, счетчик 12, де шифратор 13 временной диаграммы (ДВД триггер 14 циклов преобразования,три гер 15 пуска, дешифратор 16 команд, триггер 17 режима, счетчик-регистр 18 Устройство работает следующим образом. Внешнее устройство (ЭВМ) формирует команды Пуск, поступающие на первый вход группы входов блока 2 уп равления Импульс считывания - на второй вход группы входов блока 2 уп равления, Сброс - на третий вход группы входов блока 2 управления. Код опер;ции - на четвертый вход группы вхо,;ов блока 2 управления, Выбор устройства - на пятый вход группы входов блока 2 управления. Код адреса - на шестой вход группы входов блока 2 управления. Команда Код операции определяет один из трех возможных режимов работы системы, первый - измерение и ввод данных в ЭВМ в очередности срабатывания каналов, второй - Измерение и ввод данных в ЭВМ массивом упорядоченных в порядке возрастания номеров канало третий - измерение и ввод данных в ЭВМ по выбранному каналу. Рассмотрим работу системы во всех режимах. В исходном состоянии при включени питания или по команде Сброс триггер 14 циклов преобразования, тригге 15 пуска, триггер 17 режима блока 2 управления, триггер 7 и 8 канала 1 у тановлены в исходное (Нулевое) сост яние. Состояние триггера 14 циклов преобразования определяет цикл записи (в исходном состоянии на третьем выходе блока 2 управления уровен: 1, а на четвертом - О). Уровень выходного сигнала триггера 15 пуска блокирует работу счетчика 12 и ДВД 13. Генератор 11 импульсов вырабатывает импульсы с частотой f,. В первом режиме по соответствующей команде Код и по командам Выбор устройства и Импульс считывания триггер 17 режима блока 2 управления устанавливается в единичное состояние, что определяет работу в данном режиме ДБД 13 блока 2 управления и БФПА 5. По команде Пуск и Импульс считывания триггер 15 пуска устанавливается в единичное состояние и на входы счетчика 12 и ДВД 13.поступает сигнал разрешения. Счетчик 12 управляет работой ДВД 13, на выходе которого формируется последовательность сдвинутых по времени импульсов, определяющих процесс уравновешивания. На пятом выходе блока 2 управления устанавливается уровень 1, а на шестом - О. Высокий уровень на пятом уровне блока 2 управления определяет адрес считывания блока 10 буферной памяти на первом цикле преобразования. Мультиплексор 9 подключает выход первого триггера 7 к соответствующему входу второй группы входов БФПА 5. С первого выхода ДВД 13, являющегося первым выходом блока 2 управления, поступают импульсы +1 СТ ЦАП с частотой f fJ./8 на счетный вход счетчика 3, на выходе которого изменяется код уравновешивающего напряжения. На выходе ЦАП 4 формируется ступенчато-изменяющееся напряжение. В момент совпадения уровня образцового напряжения и напряжения на одном или нескольких входах устройства на выходе соответствующего этому входу (входам) компаратора 6 формируется сигнал разрешения записи в блок 10, по которому происходит запись кода счптчика 3 в соответствующий (соответствующие) блок 10, С второго выхода ДВД 13 (второй выход блока 2 управления) поступают импульсы СИТ, сдвинутые относительно импульсов +1 СТ ЦАП на . время, равное сумме задержек на счетчике 3, ЦАП 4, компараторе 6. При срабатывании компараторов 6 по сигналу сит соответствующий триггер 7 устанавливается в единичное состояние, что является запросом на обслу живание соответствующего канала.Выход ные сигналы с ВЫХОДОВ триггеров 7 по ступают через мультиплексор 9 на соответствующие входы второй группы входов БФПА 5. При наличии одного или .нескольких сработавших триггеров 7 на выходе БФПА 5 выставляется логический уровень сигнала, который поступает на пятый вход ДВД 13 (второй вход блока 2 управления). На пятом выходе ДВД 13 (девятом выходе блока 2 управления) формируется Син хроимпульс, по которому на первой группе выходов БФПА 5 формируется унитарный двоичный код номера сработавшего канала 1 (если произошло сра батывание в двух и более каналах 1, то выставляется код наиболее приоритетного канала), а на второй группе выходов - позиционный двоичньш код данного канала 1. Сформированный сигнал на соответствующем выходе второй группы выходов БФПА 5 поступает на вход разрешения считывания (V--) соответствующего блока 10, на KD выходе которого выставляются данные, а также на первый К-вход соответствующего триггера 7, который по сигналу сит устанавливается в нулевое состояние и снимает запрос. Данные, выставленные на выходе блока 10, и номер канала на выходах первой группы БФПА 5 при сформированном известительном сигнале СИП считываются Р ЭВМ. Таким образом, осуществляется пре образование всех входных напряжений, запись в блоки 10буферной памяти и ввод данных и номеров каналов в по рядке срабатывания, а при одновременном сра батывании нескольких каналов по их приоритету. По окончании цикла преобразования на выходе переполнения счетчика 3 формируется сигнал Конец преобразования, которьш поступает на четвертый вход ДВД 13 и С-вход триггера 14 циклов преобразования (первый вход блока 2 управления). Во временной последовательности импульсов образуется пауза, необходимая для обратного хода уравновешивающего напряжения триггер 14 циклов преобразования устанавливается в единичное состояние, на третьем выходе блока 2 управления устанавливается уровень О, а на чет вертом - 1. По окончании паузы на выходе ДВД 13 формируется последовательность импульсов, аналогичная последовательности в первом цикле,определяющих процесс уравновешивания. На пятом выходе блока 2 управления устанавливается уровень О, а на шестом - 1. Уровень О на пятом выходе блока 2 управления определяет адрес считывания блоков 10 на втором цикле. Мультиплексор 9 подключает выход второго триггера 8 к соответствующему входу второй группы выходов БФПА 5. Запись кода входного напряжения произвсЗдится в соответствующий блок 10 по адресу второго цикла, а факт срабатывания компаратора 6, установка запроса и обслуживание канала происходят с использованием соответствующего триггера 8. Таким образом, данный режим обеспечивает ввод данных в ЭВМ без остановок уравновешивающего напряжения массивом упорядоченных в порядке возрастания значений входных нartpяжeний, Во втором режиме по соответствующей команде Код операции и по команде Выбор устройства и Импульс считывания триггер 17 режима блока 2 управления устанавливается в нулевое состояние, что определяет работу в данном режиме ДВД 13 блока 2 управления и БФПА 5, Одновременно выставляется команда Пуск, по которой триггер 15 пуска устанавливается в единичное состояние и на выходы счетчика 12 и ДВД 13 поступает сигнал разрешение. Счетчик 12 управляет работой ДВД 13, на выходе которого формируется последовательность сдвинутых по времени импульсов, определяющих процесс уравновешивания. За время цикла преобразования происходит срабатывание всех компараторов и запись кода входных напряжений в соответствующие блоки. 10.По окончании цикла преобразования на выходе счетчика 3 формируется сигнал Конец преобразования, который поступает на первый вход блока 2 управления. Во временной последовательности импульсов образуется пауза, необходимая для обратного хода уравновешивающего напряжения, триггер 14 циклов преобразования устанавливается в единичное состояние (таким образом, устройство подготовлено для второго цикла преобразования:на третьем выходе блока 2 управления устанавливается уровень 1, а «а четвертом ), на пятом выходе блока управления устанавливается уровень 1, который определяет адрес считывания блока 10, а на шестом - уровень О. Таким образом, устройство подготовлено для считывания результатов первого цикла преобразования. По окончании 10 паузы на выход ДВД 13 формируется временная последовательность импульсов, аналогичная последовательности в первом цикле, определяюш;их процесс урановешивания. Запись кода входных напряжений производится в соответствующие блоки 10 по адресу второго цикла. Одновременно с преобразованием второго цикла осуществляется ввод ре зультатов первого цикла в ЭВМ. По со ответствующей данному режиму команде Код операции и команде Выбор устройства на втором выходе дешифратора 16 команд формируется сигнал, по которому выходной код счетчика-регистра 18 увеличивается на единицу, а на пятом выход ДВД 13, являющемся де вятым выходом блока 2 управления, фо мируется Синхроимпульс. Код адреса канала поступает на первую группу входов БФПА 5 и по сигналу Синхроимпульс на второй группе выходов фор мируется позиционный двоичный код номера канала. Сформированный сигнал на соответсвующем выходе второй груп пы выходов БФПА 5 поступает на вход разрешения считывания (V ) соответствующего блока 10, на выходе которо го выставляются данные, которые при сформированном известительном сигнале сип считываются в ЭВМ. Таким образом, осуществляется ввод массива данных, упорядоченных в порядке возрастания номеров каналов, в ЭВМ. По окончании второго цикла преобразования происходит установка первого цикла, а ввод результатов второ го цикла в ЭВМ осуществляется за время первого цикла преобразования. Ввод данных осуществляется без остановок уравновешивакщего напряжения. В третьем режиме процесс уравновешивания, запись кода напряжений н блоки 10, переключение триггера 14 циклов преобразования и циклов чтения происходят аналогично второму режиму. Ввод данных в ЭВМ осущест12735 15 11б вляется по команде Код операции, соответствующей третьему режиму, и команде Выбор устройства. Сигнал, сформированньй на третьем выходе дешифратора 16 команд,, поступает на вход разрешения счетчика-регистра 18, в который записывается код выбранного канала, выставленный ЭВМ на шестом входе группы входов блока 2 управления, и на девятый вход ДВД 13. С выхода счетчика-регистра 18 код номера кайала поступает на первую группу входов БФПА 5 и по сигналу Синхроимпульс на второй группе выходов формируется позиционный двоичный код выбранного канала. На выходе соответствующего блока 10 выставляются данные, которые считываются в ЭВМ при софрмированном известительном сигнале СИП, Таким образом, в третьем режиме происходит ввод данных в ЭВМ по выбранному адресу. Данный режим так :, как и предыдущий, позволяет же, совместить по времени ввод результатов преобразова шя в ЭВМ и следующий цикл преобразования, Таким образом, устройство имеет достаточно широкие функциональные возможности за счет обеспечения возможности ввода в ЭВМ результатов преобразования массивов, упорядоченным в порядке возрастания их значений, или массивов, упорядоченным в поряд возрастания номеров каналов, или по выбранному каналу. Возможность ввода данных в ЭВМ тем или иным способом позволяет упростить и ускорить обработку результатов для различных задач. Блоки устройства могут быть реализованы на серийно выпускаемых интегральных микросхемах (ИМС), например серий К521, К155, К531, При исполь-. зовании микросхем этих серий компаратор 6 представляет собой микросхему К521СА4А, триггеры 7 и 8 - К155ТВ1, мультиплексор 9 - К531КП11, двухпортовое ЗУ (блок буферной памяти) 10 К155РП1. Блок 2 управления может быть реализован на серийно выпускаемых ИМС, например, серий К155 и К556. При использовании микросхем этих серий генератор импульсов может быть вьтол-г ней на микросхеме К155ЛАЗ, соедйненный с времязадающими резисторами и конденсаторами по схеме мультивибра7тора; счетчик 12 может быть вьтолнен иа микросхеме К155ИЕ7, триггеры 14, 15 и 17 - на микросхемах К155ТМ2; ДВД 13 - на микросхеме К556ТР5; де.шифратор команд 16 - на микросхеме К155РЕЗ, .счетчик-регистр 18 - на микросхеме К155ИЕ7. Счетчик 3 может быть выполнен,например, на серийно выпускаемых ИМС К155ИЕ7. ЦАП- 4 представляет собой, например, последовательно соединенные микросхемы токового ЦАП - К594ПА1 и операционного усилителя К574УД1А, БФПА 5 представляет собой приоритетньй шифратор и регистр кода адреса, выходы KOTopbix соединены по монтажному ИЛИ,подключенные к дешифратору, и соединенную параллельно с входами шифратора N-входовую схему ИЛИ. Приоритетный шифратор, регистр, дешифратор, N-входовая схема ИЛИ могут быть выполнены соответственно на ИМС 155ИВ1, 155ИР15, К155ИДЗ,К155ЛЛ1 Формула изобретения Многоканальное устройство для вво да аналоговых, данных, содержащее блок управления, счетчик, цифроаналоговый преобразователь, блок формирования приоритетного адреса, блоки буферной памяти, компараторы, триггеры первой группы,, входы группы блока управления являются управляющими входами устройства, первьй выход блока управления соединен с входом счетчика,информационные выходы которого соединены с информационными входами блоков буферной памяти и входами цифроаналогового преобразователя, выход которого соединен с вторыми входами компараторов, первые входы которых являются информационными входами устройства, выход каждого компаратора соеди нен с первым 1-входом соответствую;щегс триггера первой группы, выход переполнения счетчика соединен с первым входом блока управления,к второму входу которого подключен выход бло ка формирования приоритетного адреса, каждьй из выходов второй группы которого соединен с входом разрешения чтения соответствующего блока буфер118ной памяти, соответствующие выходы блока буферной памяти объединены и являются информационными выходами устройства, третий и пятьм выходы блока управления соединены соответственно с входами адресов записи и чтения блоков буферной памяти, отличающееся тем, что, с целью расширения области применения путем введения двух дополнительных режимов ввода информации, устройство содержит триггеры второй группы и мультиплексоры, выход каждого мультиплексора соединен с соответствующим входом второй группы блока формирования приоритетного адреса, выходы первой группы которого являются адресными выходами устройства, второй выход блока управления соединен с С-входами триггеров первой и второй групп, четвертьм и шестой выходы блока управления соединены соответственно с вторыми 1-входами и вторыми К-входами триггеров второй группы, седьмой выход блока управления соединен с R-входами Т15иггеров первой и второй групп, восьмой и девятый выходы блока управления соединены соответственно с первым и вторым входами блока формирования приоритетного адреса, девятый вьгход блока управления является управляющим выходом устройства, выходы группы блока управления соединены с входами первой группы блока формирования приоритетного адреса, вторые 1-входы триггеров первой группы объединены с входами адресов записи блоков буферной памяти, вторые К-входы триггеров первой группы объединены с адресными входами мультиплексоров и входами адресов чтения блоков буферной памяти, первые К-входы соответствующих триггеров первой и второй групп объединены между собой и с входами разрешения чтения соответствующих блоков буферной памяти, вход разрешения записи которого объединен с первыми 1-входами соответствующих триггеров первой и второй групп,выходы которых соединены соответственно с первым и вторым информационными входами соответствуюпщх мультиплексоров .

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1984 |

|

SU1238054A1 |

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1987 |

|

SU1453397A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Многоканальная система для контроля и диагностики цифровых блоков | 1984 |

|

SU1269137A1 |

| Управляющая векторная вычислительная система | 1982 |

|

SU1120340A1 |

| Многоканальная система измерения и регистрации | 1988 |

|

SU1707546A1 |

| Многоканальное устройство для регистрации аналоговых и цифровых сигналов | 1988 |

|

SU1564649A1 |

| Многоканальная система сбора и регистрации измерительной информации | 1989 |

|

SU1783547A1 |

| Устройство для ввода-вывода информации | 1984 |

|

SU1246103A2 |

Изобретение относится к измерительной и вычислительной технике и может быть использовано при построении высокопроизводительных систем сбора и обработки аналоговых данных. Цель изобретения - расширение области применения устройства за счет введения двух дополнительных режимов ввода данных. Устройство содержит блок управления, счетчик, v цифроаналоговый преобразователь, блок формирования приоритетного адреса (БФПА), блоки буферной памяти, компараторы, триггеры первой и второй групп, мультиплексоры. Аналоговые данные поступают на первые входы компараторов, на вторые входы которых поступает линейно меняющийся сигнал с выхода ЦАП, преобразующего цифровой код счетчика. При совпадении сигналов на входах компаратора формируется сигнал разрешения записи кода счетчика в соответствующий блок буферной памяти и выдается сигнал на ввод информации в ЭВМ. Выработку управляющих сигналов и их распределение по каналам производят блок управления и БФПА. Устройство имеет три режима измерения и ввода данных: с первый - измерение и ввода данных в очередности срабатывания каналов; W второй - измерение и ввод данных массивом упорядоченных в порядке возрастания номеров каналов; третий - измерение и ввод данных по выбранному каналу. Применение блоков буферной памяти позволяет совместить процес1C | сы измерения и ввода данных во времени. Введение в устройство триггеров второй группы и мультиплексоров со со и изменение связей позволило организовать работу в первом и третьем режимах. 2 ил.

| Многоканальная система ввода аналоговой информации | 1973 |

|

SU450157A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Многоканальное устройство для ввода аналоговых данных и буферная память | 1984 |

|

SU1238054A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-30—Публикация

1985-01-11—Подача