(5) УМНОЖИТЕЛЬ ЧАСТОТЫ

| название | год | авторы | номер документа |

|---|---|---|---|

| Умножитель частоты следования импульсов | 1981 |

|

SU991614A2 |

| Цифровой умножитель частоты | 1980 |

|

SU928352A1 |

| Умножитель частоты | 1979 |

|

SU905980A1 |

| Умножитель частоты | 1979 |

|

SU907781A1 |

| Цифровой умножитель частоты | 1980 |

|

SU928353A1 |

| Умножитель частоты | 1983 |

|

SU1135004A1 |

| Устройство для контроля параметров двигателя внутреннего сгорания | 1988 |

|

SU1733946A1 |

| Умножитель частоты | 1980 |

|

SU886191A1 |

| Дискретный умножитель частоты | 1977 |

|

SU684709A1 |

| Умножитель частоты | 1979 |

|

SU807322A1 |

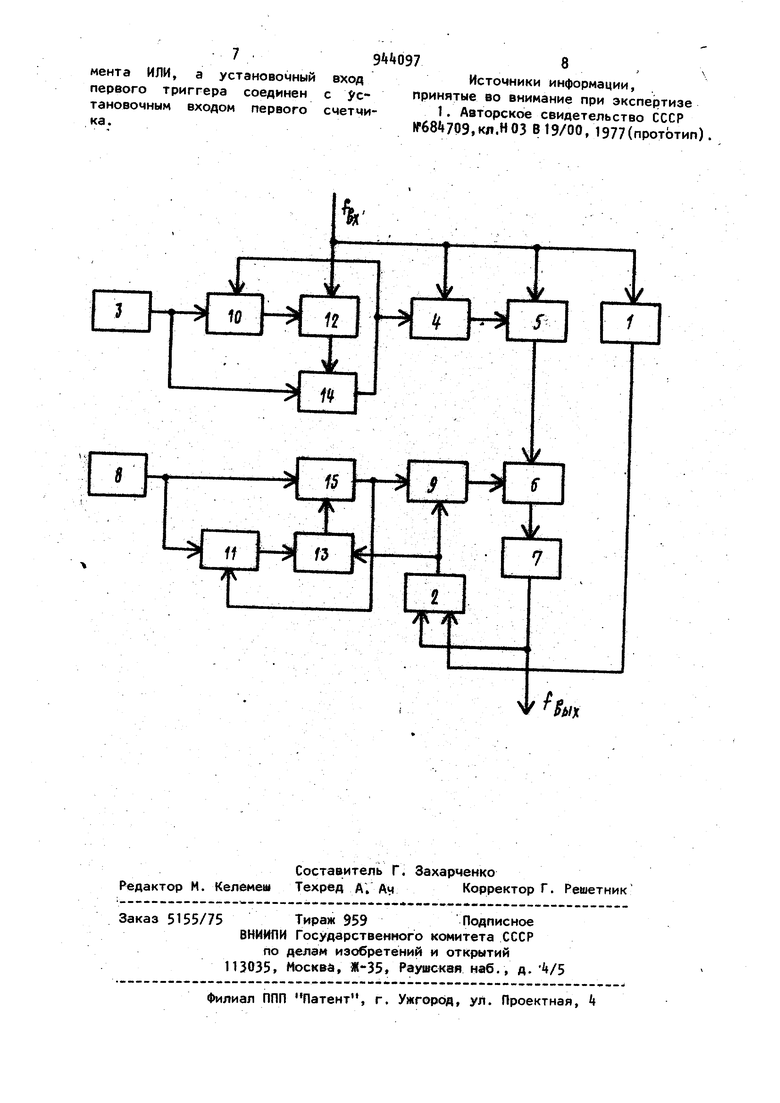

Изобретение относится к радиотехнике и может использоваться для умножения частоты, в частности, в час тотомерах низких частот для расширения диапазона измерений. Известен умножитель частоты, содержащий первый и второй опорные генераторы, а также последовательно со единенные первый счетчик блок памяти, блок сравнения,, второй вход которого соединен с выходом второго счетчика, буферное устройство, элемент ИЛИ, втЪрой вход которого соеди нен с выходом блока дифференцирования, а выход - с установочным входом второго счетчика, при этом установоч ные входы первого счетчика и блока памяти и вход блока дифференцирования соединены между собой, а точка их соединения является входом умножи теля частоты l. Однако известный умножитель час,тоты имеет относительно узкий диа1пазон умножаемых частот из-за неполного использования емкости счетчиков, блока памяти и блока сравнения} так как код на входе блока сравнения содержит в себе код, соответствующий минимальному значению периода входной частоты и представляющий собой избыточную информацию, которой перегружаются счетчики, блок памяти и блок сравнения. Цель изобретения - расширение диапазона умножаемых частот. Для этого в умножителе частоты, содержащем первый и второй опорные генераторы, а также последовательно соединенные первый счетчик, блок памяти, блок сравнения, второй вход которого соединен с выходом второго счетчика,буферное устройство, элемент ИЛИ, второй вход которого сое динен с выходом блока дифференцирования, а выход - с установочным входом второго счетчика, при этом уста(Новочные входы первого счетчика и лока памяти и вход блока дифференцирования соединены между собой, -а точка их соединения является входом умножителя частоты, между выходом первого опорного генератора и счетным входом первого счетчика введены последовательно соединенные первый делитель частоты, первый триггер и первый элемент И, выход которого соединен также с установочным входом первого делителя частоты, а второй вход - с выходом первого опорного генератора, между выходом второго опорного генератора и счетным входом второго счетчика введены последовательно соединенные второй делитель частоты, второй триггер и второй элемент И, выход которого соединен также с установочным входом второго делителя частоты, а второй вход с выходом второго опорного генератора, при этом установочный вход второ го триггера соединен с выходом второ го элемента ИЛИ, а установочный вход Первого триггера соединен с установо входом первого счетчика. На чертеже представлена структурная электрическая схема предложенног умножителя частоты. Умножитель частоты содержит блок дифференцирования 1, элемент ИЛИ 2, первый опорный генератор 3 первый счетчик t, блок памяти 5, блок сравнения 6, буферное устройство 7, второй опорный генератор 8, второй счет чик 9. первый делитель частоты 10, второй делитель частоты 11, первый триггер 12, второй триггер 13 первый элемент И 1 t и второй элемент И 15. Поступление импульса умножаемой частоты faj( на установочные входы первого счетчика i, блока памяти 5 и первого триггера 12 вызывает перенос кода в блок памяти 5 из первого счетчика , обнуление последнего и ог(рокидывание первого триггера 12. При этом прекращается поступление сигнала с прямого выхода первого триггера 12 на второй вход первого элемента И 1 и запрещается прохождение через элемент И И импульсов первого опорного генератора 3 импульсы которого поступают на вход первого делителя частоты 10. После накопления в делителе часто ты 10 NO числа импульсов, определяющего коэффициент деления делителя час тоты 10,с выхода последнего на счетный вход триггера 12 поступает импульс,воз 9 7 вращающий его в исходное состояние, и на прямом выходе триггера 12 вновь возникает сигнал, разрешающий прохождение импульсов первого опорного генератора 3 через элемент И 1 на счетный вход первого счетчика и установочный вход первого делителя частоты 10, чем достигается блокировка накопления в последнем импульсо в первого опорного генератора 3 и запол нение этими импульсами первого счетчика до появления следующего импульса умножаемой частоты foy. Записанный в блоке памяти 5 код непрерывно поступает на один вход блока сравнения 6, на другой вход которого поступает код с выхода второго счетчика 9. При совпадении этих кодов блок сравнения 6 выдает сигнал на буферное устройство 7 на выходе которого формируется импульс, поступающий на выход умножителя частоты и на первый вход элемента ИЛИ . 2, на второй вход которого поступают импульсы1 с выхода блока дифференцирования 1. Сигнал с выхода элемента ИЛИ 2 поступает на установочный вход втдрого триггера 13 и установочный вход второго счетчика 9, обнуляя его. При этом триггер 13 опрокидывается и на его прямом выходе исчезает сигнал, разрешающий прохождение через второй элемент И 15 импульсов второго опорного генератора 8. Эти импульсы проходят на вход второго делителя частоты 11. После накопления в делителе частоты 11 N числа импульсов, на его выходе появляется сигнал, который поступает на счетный вход второго триггера 13 и возвращает его в исходное состояние. В этом случае на прямом выходе второго триггера 13 возникает сигнал, который поступает на один вход второго элемента И 15 и разрешает прохождение через элемент И 15 импульсов второго опорного генератора 8 на счетный вход второго счетчика 9 и установочный вход второго делителя частоты 11. При этом происходит блокировка основного входа второго делителя частоты 11 и накопление импульсов второго делителя частоты 11 и накопление импульсов второго опорного генератора 8 во втором счетчике 9 до следующего момента совпадения кодов на входах блока сравнения 6 или появления следующего импульса умножаемой частоты, который.

воздействуя на вход блока дифференцирования 1, вызывает обнуление второго счетчика 9 и опрокидывание второго триггера 13. Блок дифференцирования 1 и элемент ИЛИ 2 позволяют синхронизировать начало циклов работ второго делителя частоты 11, второго триггера 13, второго элемента И 15 и второго счетчика 9 с появлением импульсов умножаемой частоты, что обеспечивает ограничение набега фазы во втором счетчике 9За один период умножаемой частоты g5 в первом счетчике 4 накапливается число N импульсов первого опорного генератора 3, равное

N --.T«.-N , (1)

вх - ЧИСЛО импульсов, выданных первым опорным генератором 3 за один период умножаемо частоты число импульсов, выдаваемы первым опорным генератором 3 за интервал времени, рав ный минимальному периоду Т уу,и умножаемой частоты g и коэффициент деления первого делителя частоты 10; частота на выходе первого опорного генератора 3; период умножаемой частоты. За один период Тр,(5 выходной част ты f 01,14 ° втором счетчике 9 накапли вается число N импульсов второго опорного генератора 8, равное WBb,X-% частота на выходе второго опорного генератора 8; коэффициент деления второго делителя частоты 11. полученных равенств следует i-i . I вх вых -17 С) частота f на выходе умножителя частоты во столько раз выше частоты Q умножаемой частоты, во сколько раз частота 2. второго опорного генератора 8 выше частоты перво го опорного генератора 3.

На один вход блока сравнения 6 поступает код, соответствующий разности значений текущего и минимального периодов умножаемой частоты, а

на другой вход его поступает код, соответствующий разности значений текущего и минимального периода выходной частоты, что позволяет либо упростить конструкцию умножителя частоты за счет сокращения радиоэлементов, определяющих емкость (разрядность) первого и второго счетчиков i и 9, блока памяти 5 и блока сравнения 6, либо расширить допустимый диапазон

изменения умножаемой частоты за счет увеличения допускаемого значения минимального периода умножаемой частоты. Формула изобретения Умножитель частоты, содержащий первый и второй опорные генераторы, а также последовательно соединенные первый счетчик, блок памяти, блок сравнения, второй вход которого соединен с выходом второго счетчика, буферное устройство, элемент ИЛИ, второй вход которого соединен с выходом блока дифференцирования, а выход - с установочным входом второго счетчика, при этом установочные входы первого счетчика и блока памяти и вход блока дифференцирования соединены между собой, а точка их соединения является входом умножителя частоты, отличающийся тем, что, с целью расширения диапазона умножаемых частот, между выходом первого опорного генератора и счетным входом первого счетчика введены последовательно соединенные первый делитель частоты, первый триггер и первый элемент И, выходы которого соединен также с установочным входом пер-, вого делителя частоты, а второй входс выходом первого опорного генератора, между выходом второго опорного генератора и счетным входом второго счетчика введены последовательно соединенные второй делитель частоты, второй триггер и второй элемент И, выход которого соединен также с установочным входом второго делителя частоты, а второй вход - с выходом второго опорного генератора, при этом установочный вход второго три( гера соединен с выходом второго эле7S JOS 8

мента ИЛИ, а установочный входИсточники информации,

первого триггера соединенс с- принятые во внимание при экспертизе

тановочным входом первогосчетчи- 1. Авторское свидетельство СССР ка.№684709,кя.НОЗ В 19/00,1977(протЬтип)

й

/Х

Авторы

Даты

1982-07-15—Публикация

1980-12-03—Подача